当前位置:网站首页>07-SDRAM: FIFO control module

07-SDRAM: FIFO control module

2022-08-02 00:15:00 【Liu Yan son】

设计文件

// fifo控制模块

// 1. sdram_wr_ack_d1、sdram_wr_ack_d2: 对 sdram_wr_ack 打2拍

// 2. sdram_wr_ack_fall: wr_ack 的下降沿

// 3. sdram_rd_ack_d1、sdram_rd_ack_d2: 对 sdram_rd_ack 打2拍

// 4. sdram_rd_ack_fall: rd_ack 的下降沿

// 5. wr_fifo_num: 写FIFO数据的个数

module fifo_ctrl(

input wire sdram_clk , //sdram时钟——100M

input wire sdram_rst_n , //sdram复位信号

//写fifo信号

input wire wr_fifo_wr_clk , //写FIFO写时钟——50M

input wire wr_fifo_rst , //写复位信号

input wire wr_fifo_wr_req , //写FIFO写请求

input wire [15:0] wr_fifo_wr_data , //写FIFO写数据

input wire [23:0] sdram_wr_b_addr , //写SDRAM首地址

input wire [23:0] sdram_wr_e_addr , //写SDRAM末地址

input wire [9:0] wr_burst_len , //写SDRAM数据突发长度

output wire [9:0] wr_fifo_num , //写fifo中的数据量

//读fifo信号

input wire rd_fifo_rd_clk , //读FIFO读时钟

input wire rd_fifo_rd_req , //读FIFO读请求

input wire [23:0] sdram_rd_b_addr , //读SDRAM首地址

input wire [23:0] sdram_rd_e_addr , //读SDRAM末地址

input wire [9:0] rd_burst_len , //读SDRAM数据突发长度

input wire rd_fifo_rst , //读复位信号

output wire [15:0] rd_fifo_rd_data , //读FIFO读数据

output wire [9:0] rd_fifo_num , //读fifo中的数据量

input wire read_valid , //SDRAM读使能

input wire init_end , //SDRAM初始化完成标志

//SDRAM写信号

input wire sdram_wr_ack , //SDRAM写响应

output reg sdram_wr_req , //SDRAM写请求

output reg [23:0] sdram_wr_addr , //SDRAM写地址

output wire [15:0] sdram_data_in , //写入SDRAM的数据

//SDRAM读信号

input wire sdram_rd_ack , //SDRAM响应

input wire [15:0] sdram_data_out , //读出SDRAM数据

output reg sdram_rd_req , //SDRAM读请求

output reg [23:0] sdram_rd_addr //SDRAM读地址

);

//==========================================parameter===========================================================

//==========================================reg=================================================================

reg sdram_wr_ack_d1 ; //写响应打1拍

reg sdram_wr_ack_d2 ; //写响应打2拍

reg sdram_rd_ack_d1 ; //读响应打1拍

reg sdram_rd_ack_d2 ; //读响应打2拍

//==========================================wire=================================================================

wire sdram_wr_ack_fall ; //写响应信号下降沿

wire sdram_rd_ack_fall ; //读响应信号下降沿

//==========================================assign=================================================================

//sdram_wr_ack_fall,sdram_rd_ack_fall:检测读写响应信号下降沿

assign sdram_wr_ack_fall = (sdram_wr_ack_d2 & ~sdram_wr_ack_d1);

assign sdram_rd_ack_fall = (sdram_rd_ack_d2 & ~sdram_rd_ack_d1);

//==========================================always=================================================================

//wr_ack_dly:Write response to signal beat,采集下降沿

[email protected](posedge sdram_clk or negedge sdram_rst_n)begin

if(!sdram_rst_n)begin

sdram_wr_ack_d1 <= 1'b0;

sdram_wr_ack_d2 <= 1'b0;

end

else begin

sdram_wr_ack_d1 <= sdram_wr_ack;

sdram_wr_ack_d2 <= sdram_wr_ack_d1;

end

end

//rd_ack_dly:Read the beat in response to the signal,采集下降沿

[email protected](posedge sdram_clk or negedge sdram_rst_n)begin

if(!sdram_rst_n)begin

sdram_rd_ack_d1 <= 1'b0;

sdram_rd_ack_d2 <= 1'b0;

end

else begin

sdram_rd_ack_d1 <= sdram_rd_ack;

sdram_rd_ack_d2 <= sdram_rd_ack_d1;

end

end

//sdram_wr_addr:sdram写地址

[email protected](posedge sdram_clk or negedge sdram_rst_n)begin

if(!sdram_rst_n)

sdram_wr_addr <= 24'd0;

else if(wr_fifo_rst)

sdram_wr_addr <= sdram_wr_b_addr; //复位fifoThe address is the initial address

else if(sdram_wr_ack_fall) //一次突发写结束,更改写地址

begin

if(sdram_wr_addr < (sdram_wr_e_addr - wr_burst_len)) // SDRAMAfter a burst write is completed,start writing the next line,So the address is,+突发长度 来表示

sdram_wr_addr <= sdram_wr_addr + wr_burst_len; //未达到末地址,写地址累加

else

sdram_wr_addr <= sdram_wr_b_addr; //到达末地址,回到写起始地址

end

end

//sdram_rd_addr:sdram读地址

[email protected](posedge sdram_clk or negedge sdram_rst_n)begin

if(!sdram_rst_n)

sdram_rd_addr <= 24'd0;

else if(rd_fifo_rst)

sdram_rd_addr <= sdram_rd_b_addr;

else if(sdram_rd_ack_fall) //一次突发读结束,更改读地址

begin

if(sdram_rd_addr < (sdram_rd_e_addr - rd_burst_len))

sdram_rd_addr <= sdram_rd_addr + rd_burst_len; //读地址未达到末地址,读地址累加

else

sdram_rd_addr <= sdram_rd_b_addr; //到达末地址,回到首地址

end

end

//sdram_wr_req,sdram_rd_req:读写请求信号

[email protected](posedge sdram_clk or negedge sdram_rst_n)begin

if(!sdram_rst_n)

begin

sdram_wr_req <= 1'b0;

sdram_rd_req <= 1'b0;

end

else if(init_end) //初始化完成后响应读写请求

begin //优先执行写操作,防止写入SDRAM中的数据丢失

if(wr_fifo_num >= wr_burst_len)begin //写FIFO中的数据量达到写突发长度

sdram_wr_req <= 1'b1; //写请求有效

sdram_rd_req <= 1'b0;

end

else if((rd_fifo_num < rd_burst_len) && (read_valid))begin //读FIFO中的数据量小于读突发长度,且读使能信号有效

sdram_wr_req <= 1'b0;

sdram_rd_req <= 1'b1; //读请求有效

end

else begin

sdram_wr_req <= 1'b0;

sdram_rd_req <= 1'b0;

end

end

else begin

sdram_wr_req <= 1'b0;

sdram_rd_req <= 1'b0;

end

end

//==========================================状态机=================================================================

//==========================================模块例化=================================================================

//------------- wr_fifo_data -------------

fifo_data wr_fifo_data(

//用户接口

.wrclk (wr_fifo_wr_clk ), //写时钟

.wrreq (wr_fifo_wr_req ), //写请求

.data (wr_fifo_wr_data), //写数据

//SDRAM接口

.rdclk (sdram_clk ), //读时钟

.rdreq (sdram_wr_ack ), //读请求

.q (sdram_data_in ), //读数据

.rdusedw (wr_fifo_num ), //FIFO中的数据量

.wrusedw ( ),

.aclr (~sdram_rst_n || wr_fifo_rst) //清零信号

);

//------------- rd_fifo_data -------------

fifo_data rd_fifo_data(

//sdram接口

.wrclk (sdram_clk ), //写时钟

.wrreq (sdram_rd_ack ), //写请求

.data (sdram_data_out ), //写数据

//用户接口

.rdclk (rd_fifo_rd_clk ), //读时钟

.rdreq (rd_fifo_rd_req ), //读请求

.q (rd_fifo_rd_data), //读数据

.rdusedw ( ),

.wrusedw (rd_fifo_num ), //FIFO中的数据量

.aclr (~sdram_rst_n || rd_fifo_rst) //清零信号

);

endmodule

边栏推荐

猜你喜欢

如何发现新的潜力项目?工具推荐

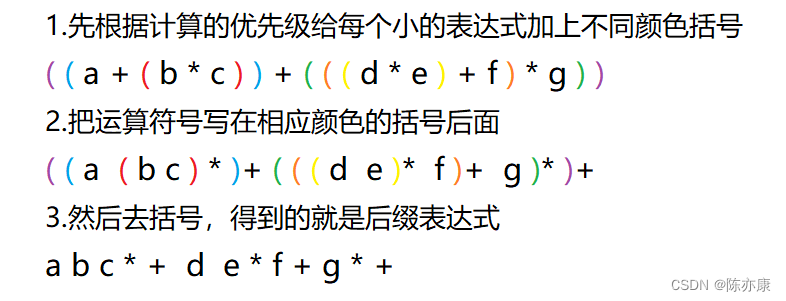

中缀转后缀、前缀表达式快速解决办法

![[Three sons] C language implements simple three sons](/img/96/c3f6c331cbc6d794dc5381cf176ba7.png)

[Three sons] C language implements simple three sons

一文概览最实用的 DeFi 工具

Artifact XXXwar exploded Artifact is being deployed, please wait...(已解决)

Wincc报表教程(SQL数据库的建立,wincc在数据库中保存和查询数据,调用Excel模板把数据保存到指定的位置和打印功能)

当奈飞的NFT忘记了Web2的业务安全

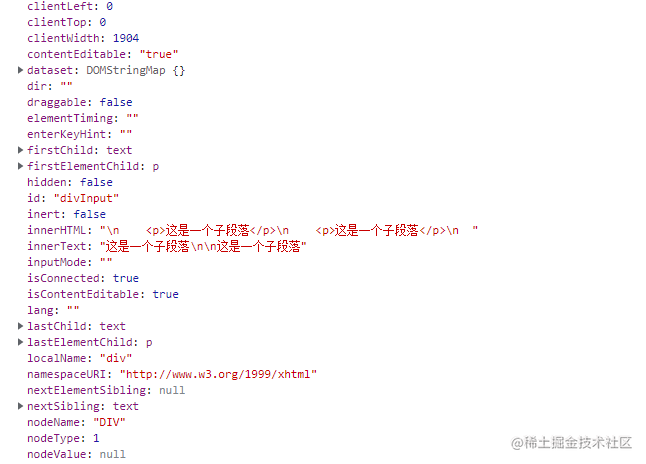

contentEditable属性

为什么要使用MQ消息中间件?这几个问题必须拿下

如何设计循环队列?快进来学习~

随机推荐

@Scheduled注解详解

双队列实现栈?双栈实现队列?

如何进行数据库备份

@Transactional 注解使用详解

security CSRF漏洞保护

玩转NFT夏季:这份工具宝典值得收藏

Programmer is still short of objects? A new one is enough

Is TCP reliable?Why?

Flink Yarn Per Job - CliFrontend

DVWA靶场环境搭建

以交易为生是一种什么体验?

Use Jenkins for continuous integration, this knowledge point must be mastered

【MySQL系列】MySQL数据库基础

短视频SEO优化教程 自媒体SEO优化技巧方法

ansible模块--copy模块

Collection of NFT tools

Bean的生命周期

2022 6th Strong Net Cup Part WP

短视频seo搜索优化主要内容

contentEditable属性