当前位置:网站首页>【UVM入门 ===> Episode_9 】~ 寄存器模型、寄存器模型的集成、寄存器模型的常规方法、寄存器模型的应用场景

【UVM入门 ===> Episode_9 】~ 寄存器模型、寄存器模型的集成、寄存器模型的常规方法、寄存器模型的应用场景

2022-06-25 06:38:00 【AI很不错呦】

1. 寄存器模型

1.1 概述

1.2 模型建立

1.3 中心化管理

1.4 uvm_reg

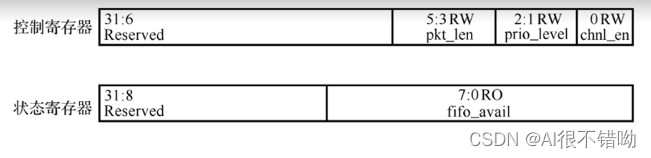

1.4.1 MCDF寄存器模型

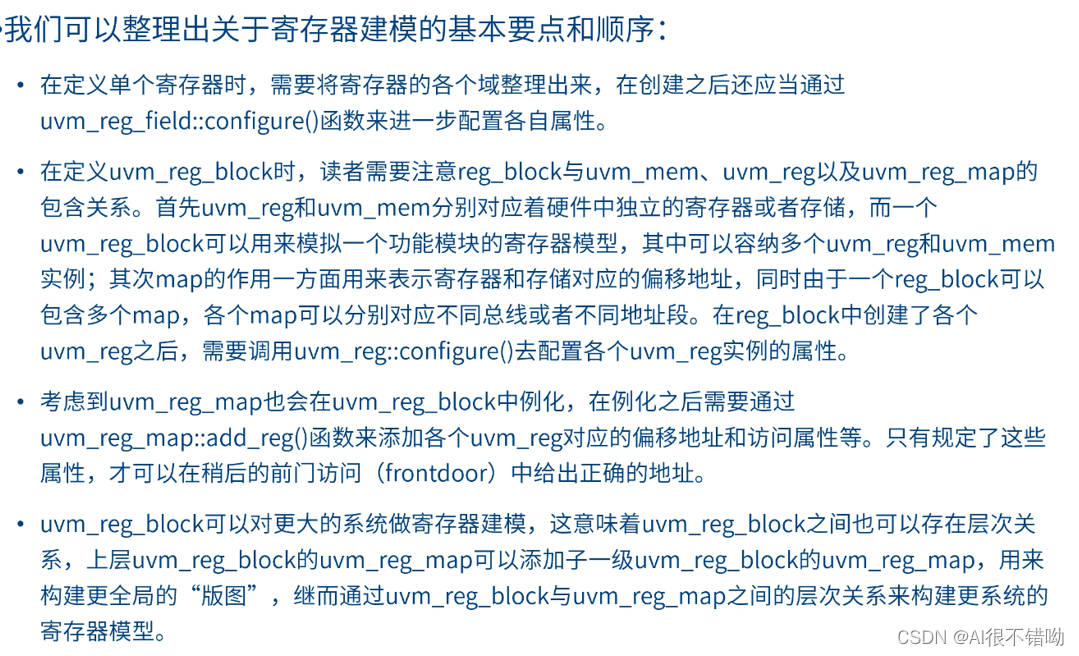

1.5 寄存器建模

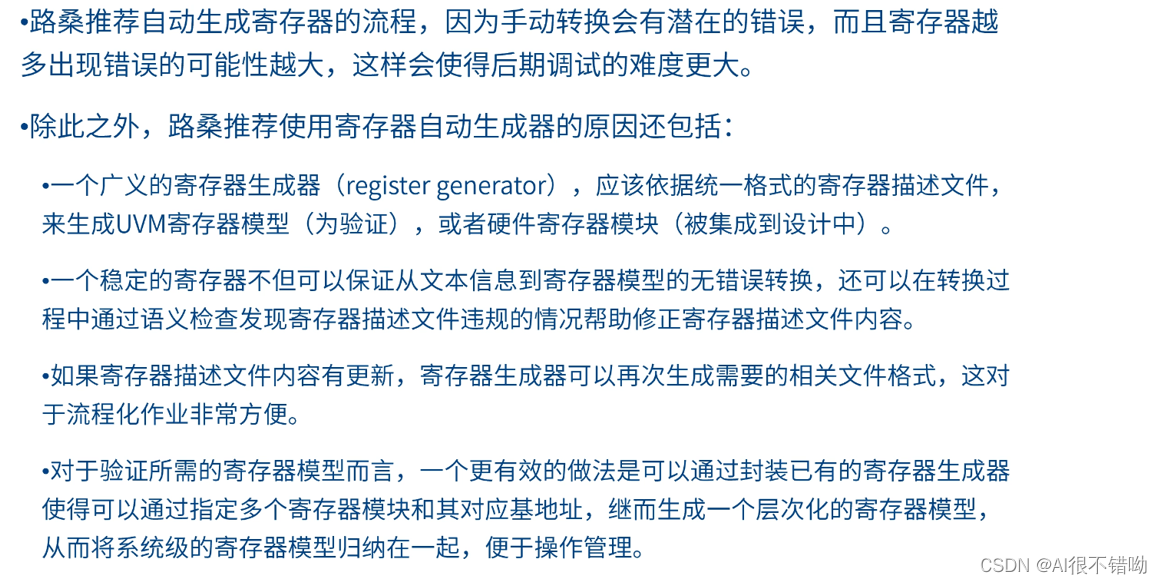

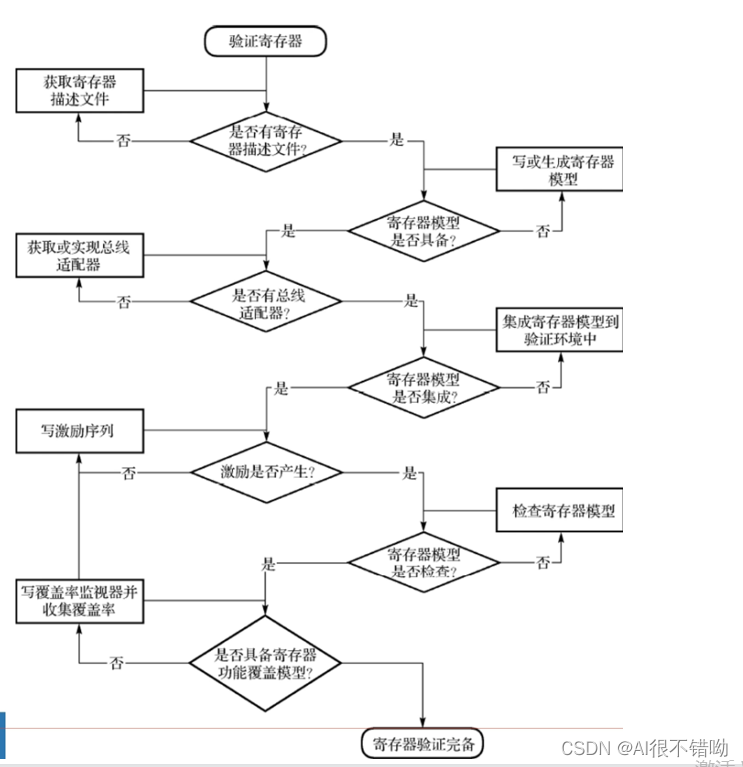

1.5.1 模型使用流程

2. 寄存器模型的集成

2.1 总线UVC

2.1.1 什么是UVC?

UVC的全称是UVM Component,往往是我们构建环境中所用到的最底层的组件,它虽然“小”,但却十分重要,许多模块级的验证甚至SOC验证都会使用相同的UVC,牵一发而动全身。

2.1.2 什么是VIP?

这里的VIP可不是大家生活中的 VIP 呀!这里是指 Verification IP,VIP的范围更广,多为第三方提供(也有企业自研VIP),它可能不仅仅只是一个uvm的组件,可能会是一个纯sv的对象集合,也可能会是一些verilog的model,所以uvc是vip的一个非空真子集。

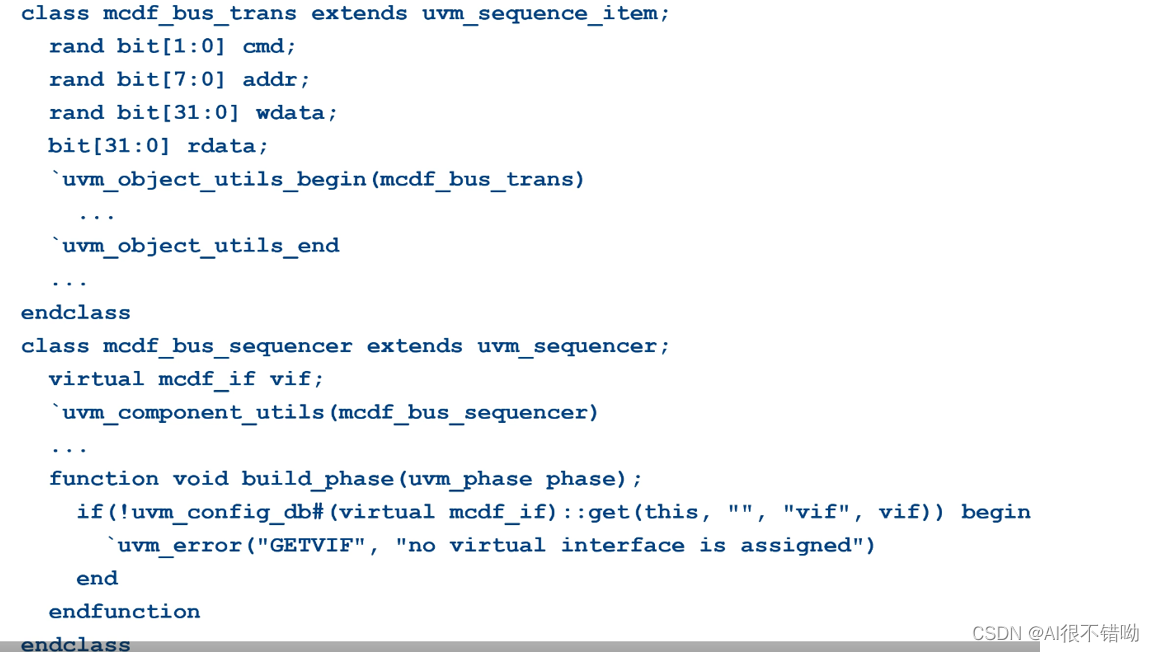

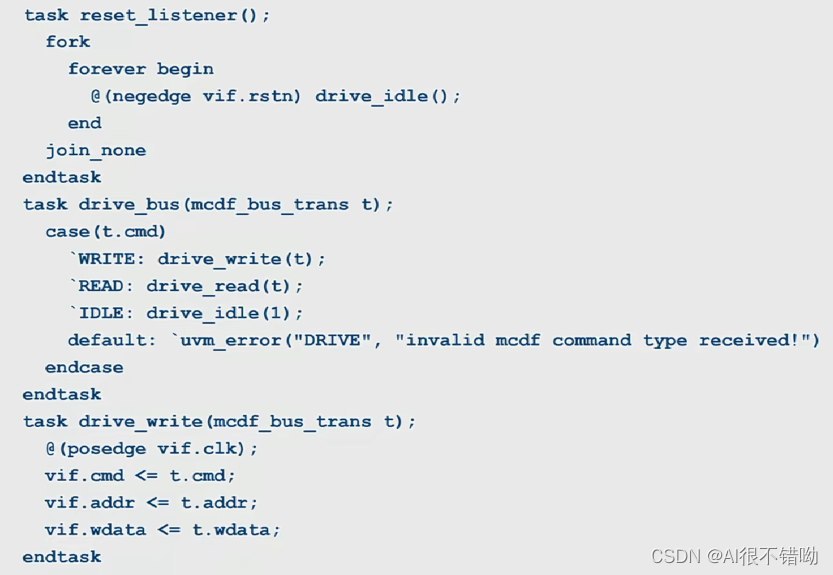

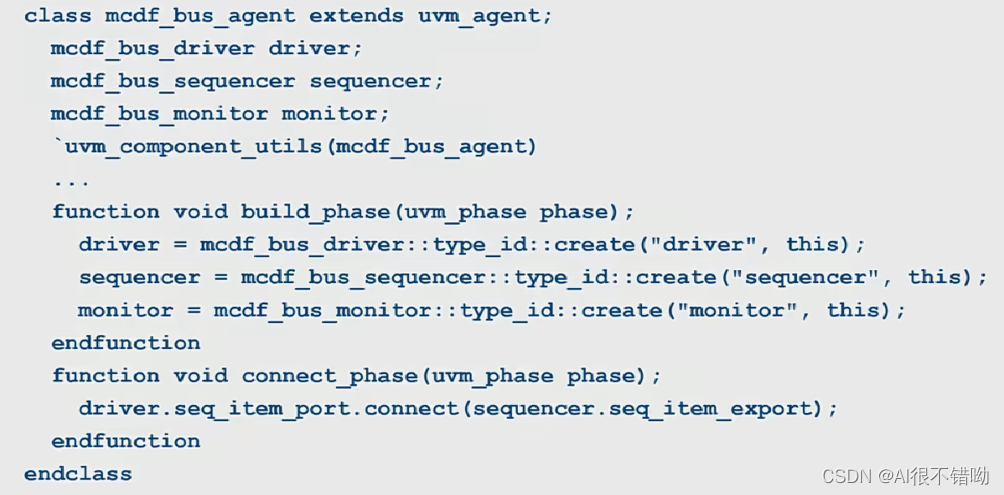

2.1.3 实现

2.1.4 代码解析

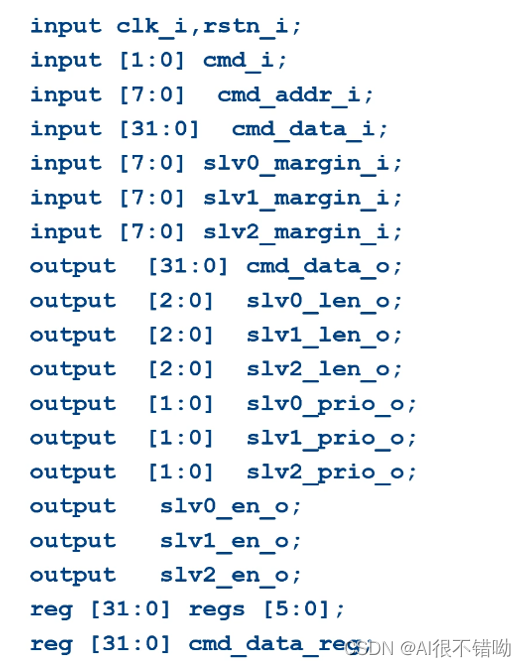

2.2 MCDF寄存器设计代码

2.3 Adapter

2.3.1 概述

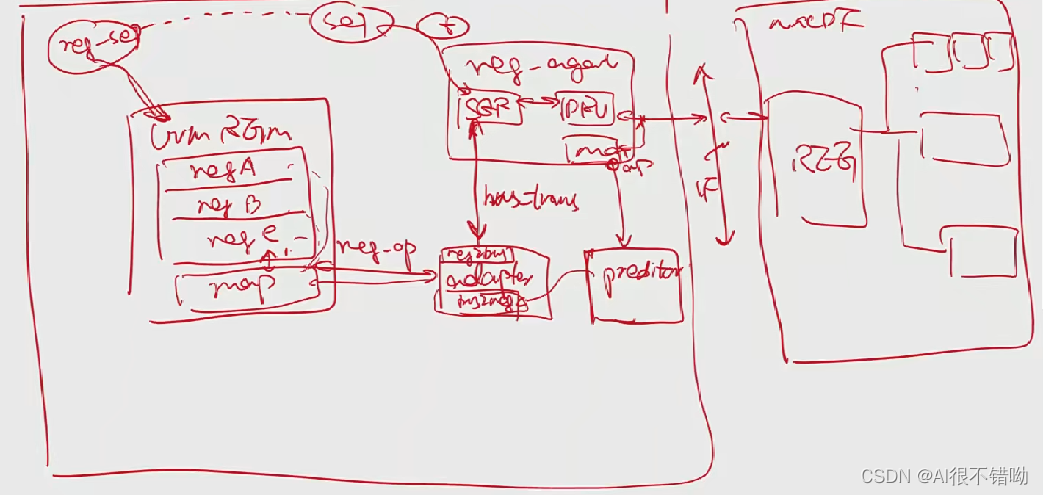

2.3.1.1 无predictor

2.3.1.2 有predictor

2.3.2 实现

2.3.3 解析

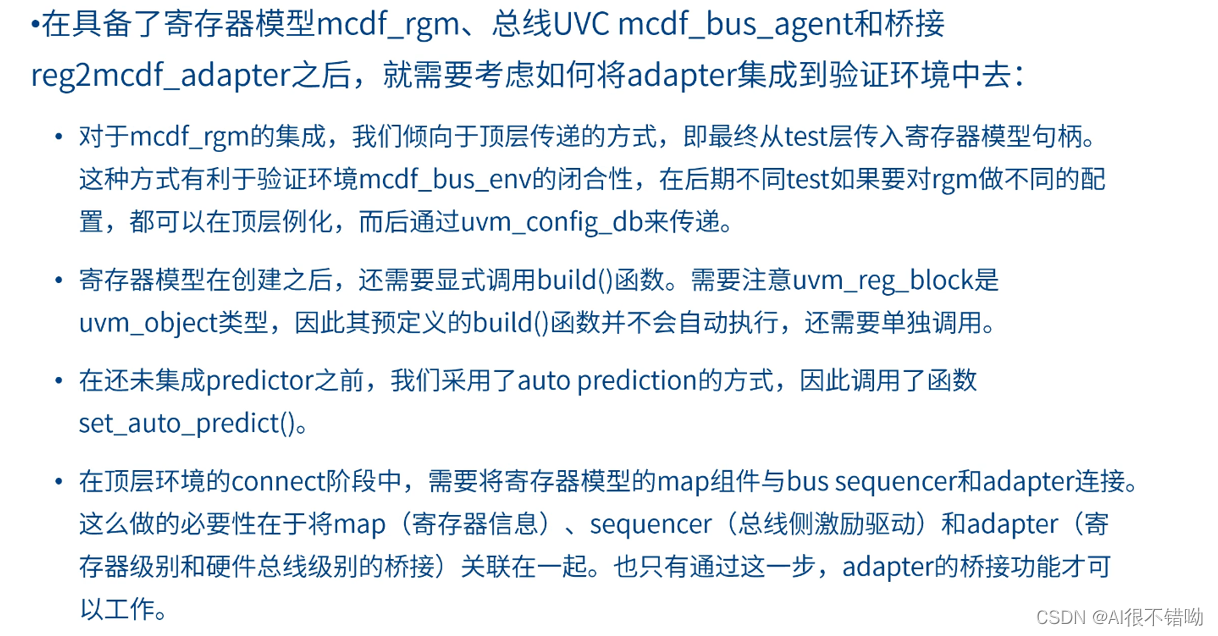

2.3.4 集成

2.3.4.1 代码实现

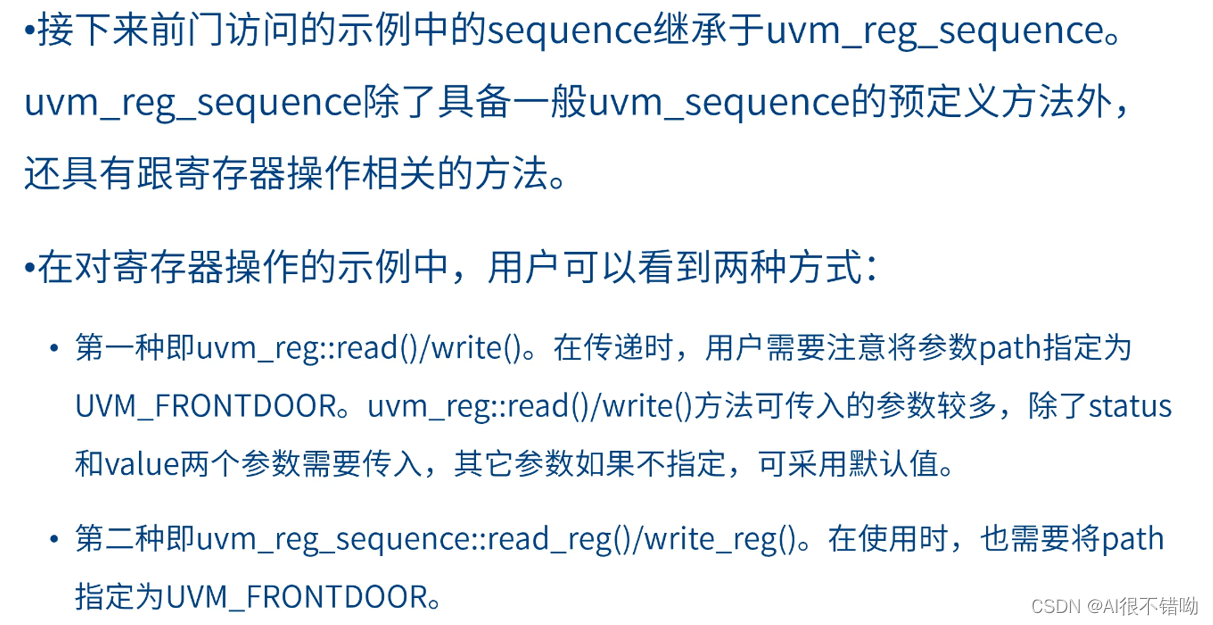

2.3.5 访问方式

2.3.5.1 前门访问

2.3.5.2 举例说明

2.3.5.3 后门访问

2.3.5.4 举例说明

2.3.5.5 二者的比较

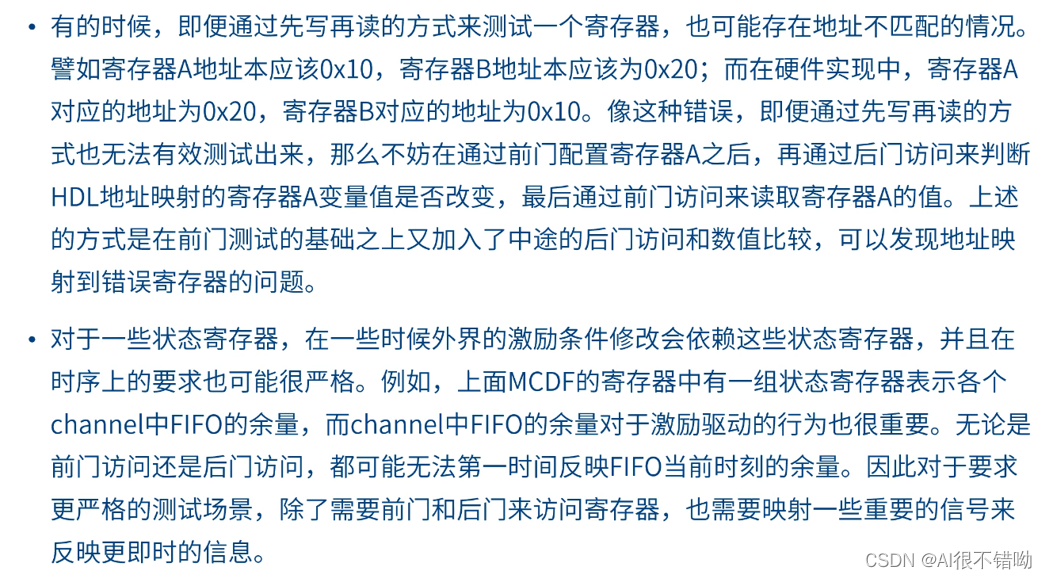

2.3.5.6 混合应用

3. 寄存器模型的常规方法

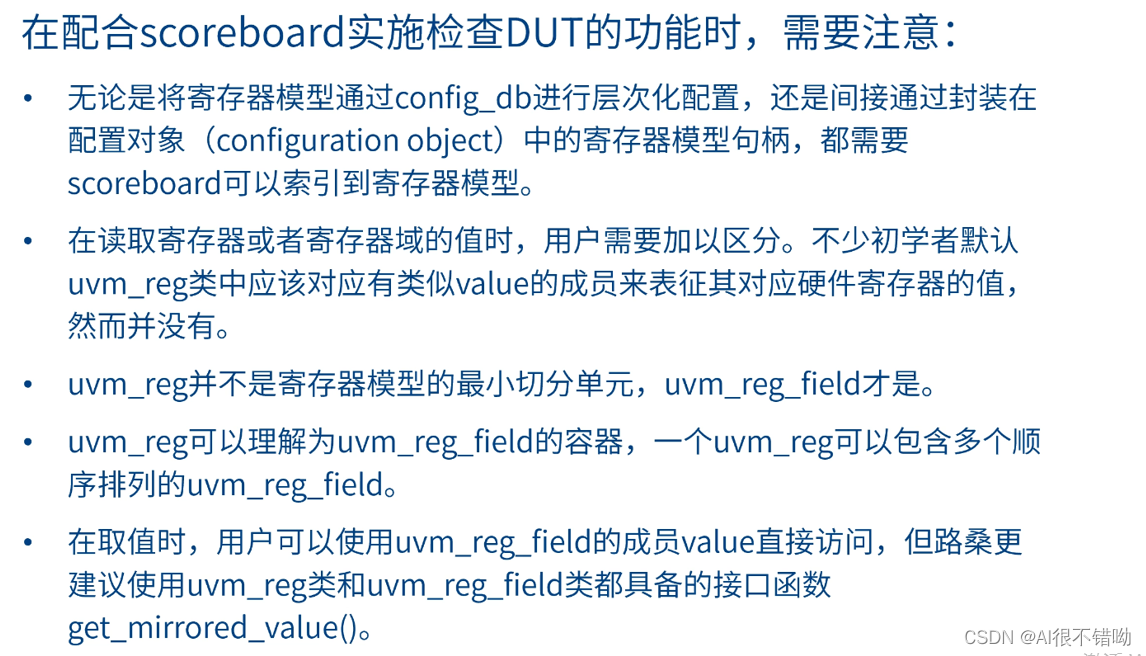

3.1 mirror、desired和actual value

3.2 prediction的分类

3.2.1 自动预测

3.2.2 显示预测

3.3 访问方法

3.4 mem 与 reg 的联系和差别

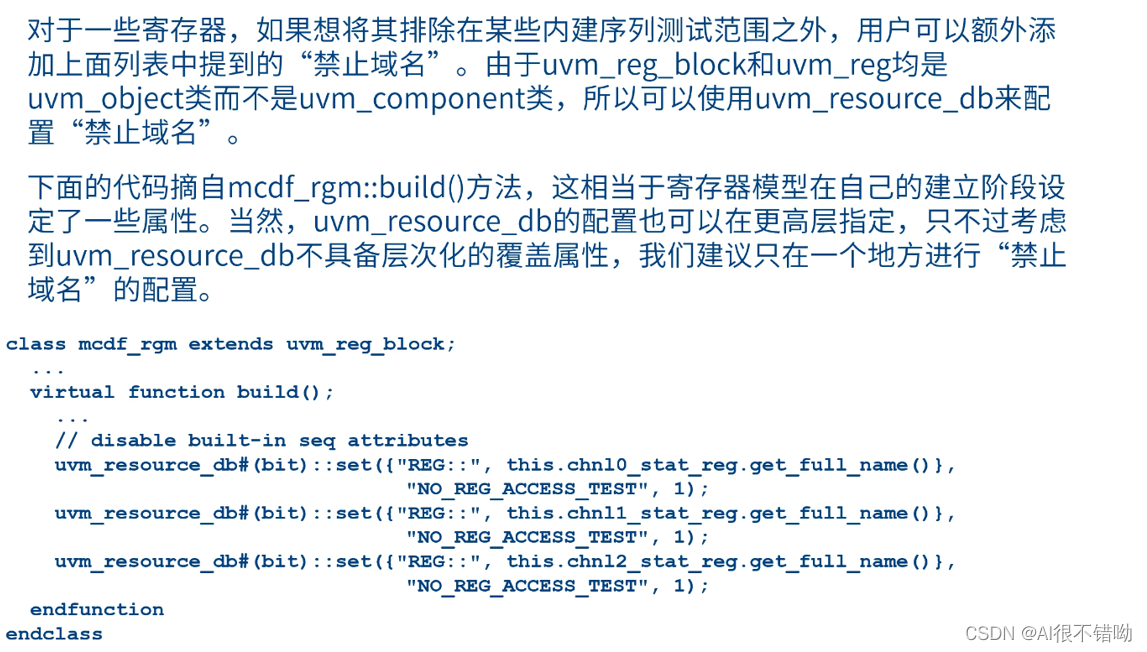

3.5 内建(build-in)sequences

4. 寄存器模型的应用场景

4.1 概述

4.2 寄存器检查

4.3 功能覆盖率概述

4.3.1 举例说明

边栏推荐

- 想买股票去哪个证券公司开户更快更安全

- Shandong finds clean energy that can be used by China for 3800 years? You should know the truth first

- Blue Bridge Cup SCM module code (LED) (code + comments)

- Three laws of go reflection

- Reading sensor data with GPIO analog SPI interface

- Shell命令学习

- [Shangshui Shuo series] day 4

- Kubernetes cluster dashboard & kuboard installation demo

- Direct select sort and quick sort

- Clearing Magento log data - clearing Magento log data

猜你喜欢

Ctfhub web information disclosure directory traversal

![[he doesn't mention love, but every word is love]](/img/28/0c3ddad3dc9b1ef8d0618164f39e53.png)

[he doesn't mention love, but every word is love]

爱情️终结者

分布式锁中的王者方案 - Redisson

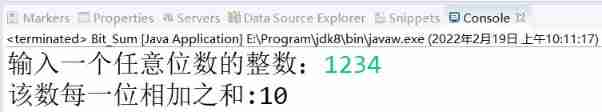

Enter an integer with any number of bits, and output the sum of each bit of the number. For example: 1234 – > 10

The process of making wooden barrels with 3DMAX software: a three-step process

レ / leilei

【他字字不提爱,却句句都是爱】

アルマ / alchemy girl

1W字|40 图|硬核 ES 实战

随机推荐

Ctfhub web - divulgation d'informations - traversée du Répertoire

joda. Time get date summary

Conditional grouping with $exists inside $cond

lotus v1.16.0-rc2 Calibration-net

【工具分享】一款颜值与技能并重的软件

Wow, it's so rich.

100 times larger than the Milky way, Dutch astronomers found mysterious objects in deep space

Cloning and importing DOM nodes

Atomic alpha development board -- SD card and EMMC burning tool

Common cluster scripts

[Shangshui Shuo series] day 5

终于等到你,小程序开源啦~

Keil debug view variable prompt not in scope

Ppt template of small fresh open class education courseware

The most basic difference between clustering and classification.

Can we use function pointers in go- Can we have function pointers in Go?

Too beautiful promise because too young

lotus v1.16.0-rc3 calibnet

The process of making wooden barrels with 3DMAX software: a three-step process

Direct select sort and quick sort