当前位置:网站首页>Required questions for group planning: storage system (completed, with detailed analysis attached)

Required questions for group planning: storage system (completed, with detailed analysis attached)

2022-06-21 06:10:00 【Cold froth】

List of articles

The first part

1. Which of the following is a volatile memory (A)

A.Cache

B.EPROM

C.Flash Memory

D.DVD

analysis :RAM All belong to volatile memory , and ROM All nonvolatile memory , Therefore, this question can be translated into determining which of the following memories is RAM. Cache cache It must be RAM, and EPROM It must be ROM, Flash memory and DVD It's also ROM, The answer to the question .

2. The following semiconductor memories need to be refreshed (B)

A.SRAM

B.DRAM

C.EPROM

D.Flash Memory

analysis :DRAM Is the only memory that needs to be constantly refreshed .

3. Memory is the memory device of computer system , It is mainly used for (C)

A. Storing data

B. Store the program

C. Store data and programs

D. Store microprograms

analysis : The function of memory is to store data and programs . Microprograms are placed in specific memory , Control memory , therefore D Generalize options .

4. A computer's memory is addressed in bytes , The size of the main memory address space is 64MB, use 4M*8 Of RAM Expanded into 64MB Main memory , How many bits does the memory address register have (D)

A.22 position

B.23 position

C.25 position

D.26 position

analysis : The memory address register is used to store the address of a memory unit . Because the main memory space is 64MB, and 64M=2^26, Therefore, the memory address register has at least 26 position .

5. One capacity is 4K×16 Bit memory , The sum of its address line and data line is (C)

A.20

B.24

C.28

D.30

analysis : The total number of storage units in the memory is 4K, The data of each unit is 16 position , Therefore, the number of digits of the data line is log2(4K)=12 position , The number of digits of the data line is 16 position , So the total number of digits equals the sum of the two equals 28 position . Be careful ! This question needs to be distinguished from the previous one : The number of bits in the memory address register is equal to... Of the total number of bytes in memory 2 logarithm , The number of bits of the address line is equal to% of the total number of words in the memory 2 logarithm .

6. One has 24 Bit address and 8 Bit word long memory , If the memory consists of 4M×1 Bit RAM Chip composition , How many such chips are needed (D)

A.48

B.24

C.8

D.32

analysis : Because the address is 24 position , So the total number of words is 2pow(24) individual , And each word is 8 position , So the total number of digits =2pow(27) position . One 4M×1 Bit RAM Chips share 2pow(22) position , Therefore need 32 Films like this RAM The chip can be used to form the chip with larger capacity .

7. Can be used as Cache Our memory chip is (C)

A.RAM

B.DDR

C.SRAM

D.SDRM

analysis :SRAM yes Cache The carrier of the chip , and DRAM Is the main carrier of memory . Direct use RAM Generalization is obviously not as good as SRAM accuracy .

The second part (Cache relevant )

Example 1: The cache of a direct mapping is 128B, Each piece is 4 A word (1 A word 32 position ), Main memory capacity 4096B, Write out the cache address and main memory address .

analysis :

① because Cache Each block of has 4 A word , And every word 32 position , So every Cache Block for 128 position =16B;

② because Cache The capacity of is 128B, therefore Cache The number of lines in =128B/16B=8( That's ok ), Therefore, it is necessary to 3 Bit indicates the line number in the area ;

③ Because each piece is 16B, Therefore need 4 Bit to represent the address within the block ;

④ Because the main memory capacity is 4096B, And each block is 16B, One district has 8 Block , So there is 4096/(16*8)=32 Districts , So we need to 5 Bits indicate area code .

in summary , The cache address is “3 Tag block number +4 Address in bit block ”, The main memory address is “5 Bit area code +3 Block number in bit area +4 Address in bit block ”.

Example 2: A direct mapping cache has 8 block , Each piece is 16B, Then the byte is 191 The address of should correspond to Cache Which piece of the ?

analysis : According to the principle of direct mapping , Memory unit 191 The number of blocks in main memory is 191 to be divisible by 16=11( block ), So the corresponding Cache The number of blocks in is 11%8=3( block ).

Example 3: Assuming a Cache Yes 64 block , Each piece is 16 Bytes , Then the address in memory is 1200 The unit of should correspond to Cache Which piece of the ?

analysis : In main memory 1200 The block number corresponding to the cell =1200//( To divide or divide )16=75( block ), And the first 75 Block main memory data is mapped to Cache The number of lines in =75%64=11( That's ok ), Thus the solution is obtained .

Example 4: Main memory and cache Direct mapping between , Block size is 16B.cache The data area capacity of is 64KB, The main memory address is 32 position , Address by byte . If significant bits and marker bits are taken into account , Calculation cache Capacity size of (C)

A.64KB

B.64K×16b(tag)+64K×8b

C.4K×(1+16)b+64K×8b

D.4K×16b+64K×8b+1b(V Effective bit )

analysis :

① Without special instructions Cache The capacity of the data area defaults to the capacity of the data area , But here we consider the part of the associated memory .

② Because the size of each block is 16B, Therefore, the address in the block is 4 position .

③ because Cache The data area capacity of is 64KB, So there is 64KB/16B=4K( block ), Therefore, the block number in the area needs to use 12 Bit representation .

④ Because the main memory address is 32 position , So the rest 32-4-12=16 Bit is used to mark bit , That is, the area code .

⑤ because Cache There's a total of 4K Block , Each piece has 16 Bits mark bits and 1 The bit significand therefore Cache The total capacity of 64KB+4K×(1+16)b=64K×8b+4K×(1+16)b.

Example 5: Suppose main memory is addressed in bytes ,Cache share 64 That's ok , Direct mapping is adopted , The size of the main memory block is 32 byte , All numbers from 0 Start , ask 2593 The main memory block of Unit No. is located in Cache The corresponding line in is (B)

A.1

B.17

C.34

D.63

analysis : Because a block is 32 Bytes , therefore 2593 Block number of No. unit in main memory =2593//( to be divisible by )32=81, In main memory, there are 81 Block mapping to Cache The number of lines in =81%64=17, Thus the solution is obtained .

Example 6: The cache of a direct mapping is 128B, Each piece is 4 A word , namely 4*32 position (16B), The main memory capacity is 4096B, Please write out the composition of cache address and main memory address .

analysis : Because each piece is 16 Bytes , Therefore, the address within the block needs to 4 Bit representation ; Because the cache is 128B, And each block is 16B, Therefore, the block number in the cache needs log2(128B/16B)=3 Bit representation ; Because the main memory capacity is 4096B The cache capacity is 128B, Therefore, the main memory needs to be divided into 4096/128B=32 Districts , So we need to 5 Bits indicate area code . in summary , The form of cache address is “3 Tag block number +4 Address in bit block ” In the form of , The form of the main memory address is “5 Bit area code +3 Tag block number +4 Address in bit block ”.

The third part ( Virtual storage related )

Example 1: Page tables in virtual memory can be divided into fast tables and slow tables , What is correct in the following description of the page table is (D)

A. Both fast and slow tables are stored in main memory , But the capacity of fast meter is smaller than that of slow meter

B. The fast table adopts an optimized search algorithm , So search speed is fast

C. The hit rate of fast table is higher than that of slow table , So the quick table can get more search results

D. The fast meter is composed of fast memory components , Follow what you find to access , Therefore, it is faster than slow table query

analysis :

A Options : The capacity of fast meter is smaller than that of slow meter ; The slow table is stored in main memory , The fast table is stored in a special fast memory TLB in , and TLB Not in main memory , therefore A Wrong option .

B Options : Fast tables look up faster than slow tables , The reason is that the fast table is stored in the fast memory instead of the algorithm , therefore B Wrong option .

C Options : The hit rate of the fast table is generally lower than that of the slow table and the capacity is smaller than that of the slow table , So the slow table can get more search results , therefore C Wrong option . D Options : Same interpretation B Options , therefore D The options are right .

Example 2: What is wrong in the following statement is (C)

A.TLB It's a fast watch , That is, convert the backup buffer

B. The quick table stores the common page table items in the current process

C. When the fast watch hits , It must hit in the first layer cache

D. A fast table is also a cache of page table entries , It must be CPU in

analysis : It can be considered that the conversion backup buffer TLB It's a fast watch , therefore A The options are right ; A fast table is equivalent to a page table Cache For memory , Used to store commonly used page table items , therefore B The options are right ; Page tables can be considered as a kind of cache and stored in CPU in , therefore D The options are right ; When the fast table hits, it indicates that the page table entry is stored in the fast table , That is, the corresponding page table is in memory , However, it does not mean that the data in the page table is also Cache in , therefore C Wrong option .

Example 3: In a paged virtual memory , Page size is 4KB, The virtual memory size is 4GB, The size of the physical memory block is 4MB, Then the corresponding virtual page number digits are (B)

A.12

B.20

C.28

D.32

analysis : Assuming that 32 Bit of computer , From the conditions of the topic , Because the page size is 4KB, Therefore, the in page offset address is log2(4K)=12 position , To use 32 The rest of the bits 20 Bit indicates the virtual page number , That is, the virtual page number has 20 position .

边栏推荐

- Latest analysis on operation of refrigeration and air conditioning equipment in 2022 and examination question bank for operation of refrigeration and air conditioning equipment

- sqli-labs-17

- 代码生成器文件运行出错:The server time zone value ‘�й���ʱ��‘ is unrecognized or represents more than one time

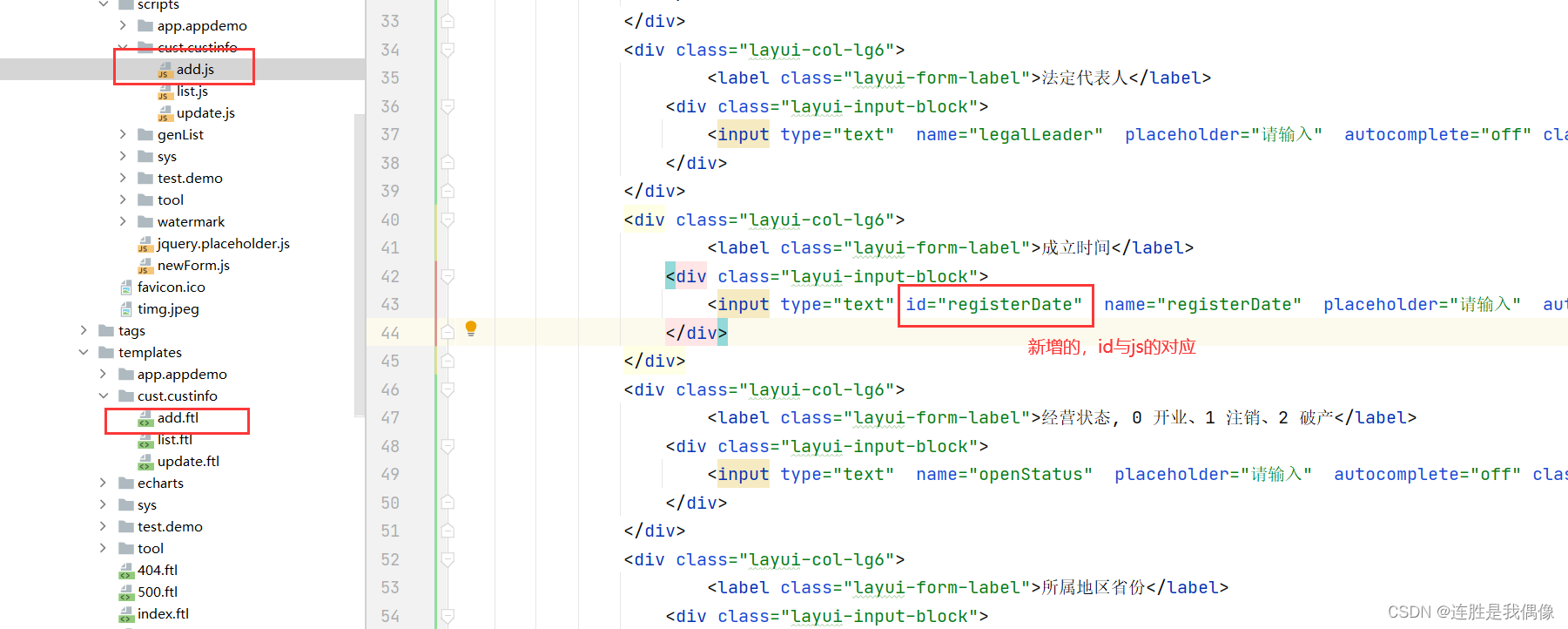

- Improve the determination of the required items of business details. When the error information is echoed according to the returned status code, the echoed information is inconsistent with the expecta

- Refine business details

- FPGA - 7 Series FPGA selectio -06- odelay of logic resources

- tf. compat. v1.get_ default_ graph

- 【JVM】方法区

- [MySQL] SQL statement execution process of MySQL

- tf. AUTO_ Reuse effect

猜你喜欢

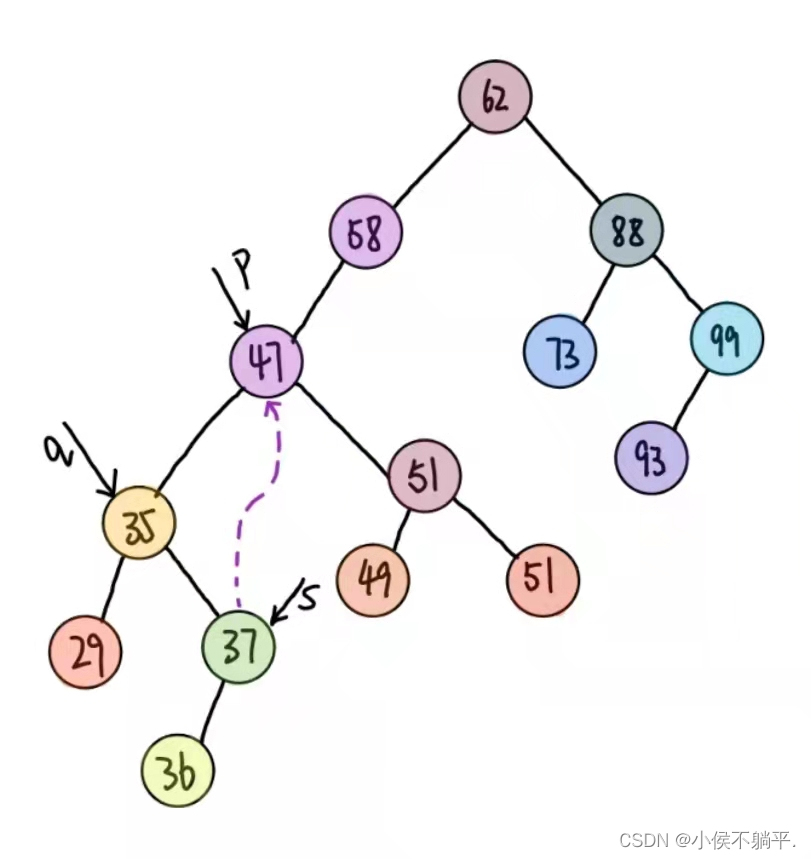

二叉排序树的基本操作

Excel column numeric index to character index

代码生成器文件运行出错:The server time zone value ‘�й���ʱ��‘ is unrecognized or represents more than one time

The time plug-in is used for the establishment time, but when modifying parameters on the web page, if the time is not modified, an error will be reported when saving it for the first time, and it can

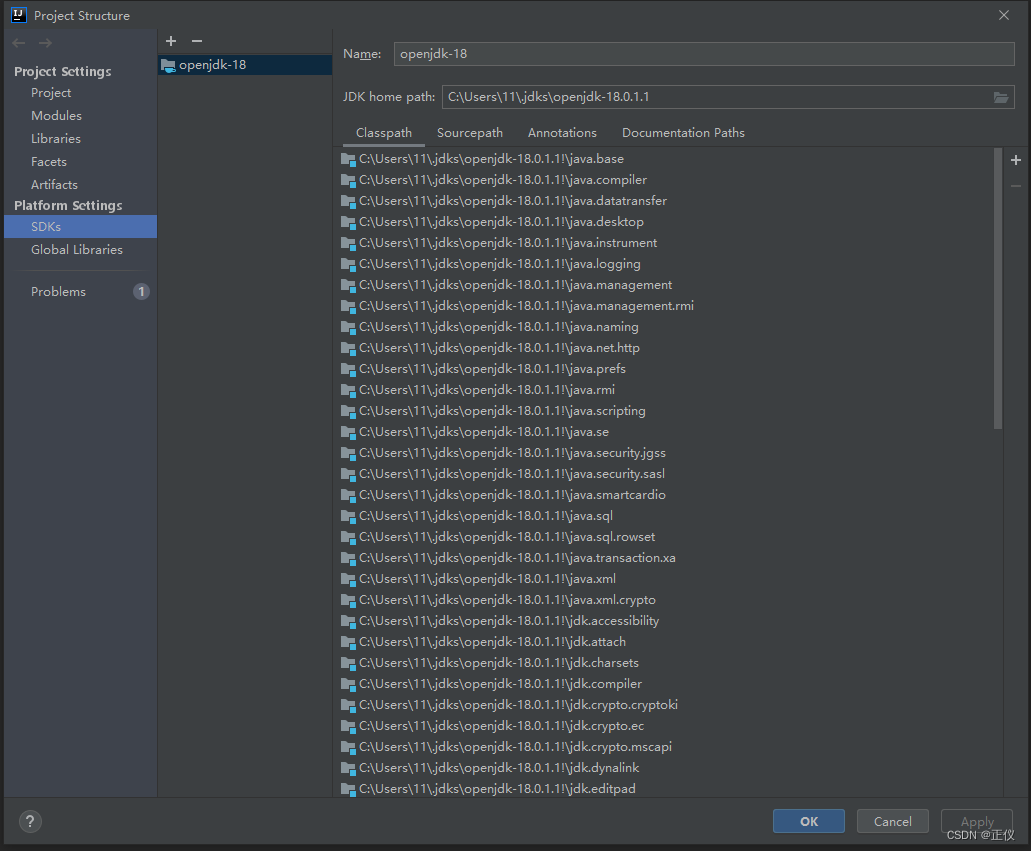

IDEA 使用记录

【数据挖掘】期末复习 第三章

sqli-labs-17

sqli-labs23

FPGA - 7系列 FPGA SelectIO -02- 源语简介

Account1 is not in the sudoers file. The matter will be reported.

随机推荐

Aurora 8b10b IP use - 02 - IP function design skills

第一章:数据库系统概述(数据库期末复习)

Laravel

【JVM】 类加载器(ClassLoader)

Improved Object Categorization and Detection Using Comparative Object Similarity

Touch chip applied in touch screen of washing machine

tf. compat. v1.MetaGraphDef

tf.compat.v1.MetaGraphDef

simple_ JS attack and defense world

leetcode 675. Cutting down trees for golf competitions - (day29)

Connection refused : no futher information : localhost/127.0.0.1:6379

三维引擎软件Vizard入门

深度学习的几种优化方法

Do you want to manually implement CSDN dark mode for web page '?

深度理解RNN的梯度消失和LSTM为什么能解决梯度消失

代码生成器文件运行出错:The server time zone value ‘�й���ʱ��‘ is unrecognized or represents more than one time

sqli-labs23

微生物生态数据分析——冗余分析

El table circular upgrade

Aurora8b10b IP usage-05-transceiver test application example