当前位置:网站首页>Based on FPGA in any number of bytes (single-byte or multibyte) serial port (UART) to send (including source engineering)

Based on FPGA in any number of bytes (single-byte or multibyte) serial port (UART) to send (including source engineering)

2022-08-01 20:34:00 【lonely single knife】

1、概述

在这篇文章中串口(UART)的FPGA实现(Contains the source code project),实现了基于FPGASerial port to send driver.Use send driver can realize 起始位1bit+数据位8bit+停止位1bit 共10bitSingle-byte transmission.

But in the process of practical application and often requires a one-time send multiple bytes of data.比如,A sends a bit wide for【39:0】的数据.诚然,Can change the article directly in the serial port to send driver,使其变成 起始位1bit+数据位40bit+停止位1bit 共42bitMulti-byte transmission.这种方法理论上是可行的,因为UARTAgreement did not stipulate time to send you、Receive more lessbit的数据,既然能发送8个bit,It can also send40个bit.

但是很不幸,In fact the basic won't work,Because most of general PC do not support a resolution40bit的数据位(If you write a machine when I didn't say).

So can only think of some other way to,比如:写个逻辑,多次调用8bitThe single-byte serial port to send driver,40bitThe data of call5次,That is cut into5个 起始位1bit+数据位8bit+停止位1bit共10bit的单字节 Respectively, it is ok to send the past.

2、A serial port to send driver

请参考:串口(UART)的FPGA实现(Contains the source code project),In this article introduces in detail a serial port to send driver.

以下代码可以实现 1bit+数据位8bit+停止位1bit 共10bitSingle-byte transmission,无奇偶校验.

// *******************************************************************************************************

// ** 作者 : 孤独的单刀

// ** 邮箱 : [email protected]

// ** 博客 : https://blog.csdn.net/wuzhikaidetb

// ** 日期 : 2022/07/31

// ** 功能 : 1、基于FPGASerial port to send driver module;

// 2、可设置波特率BPS、主时钟CLK_FRE;

// 3、起始位1bit,数据位8bit,停止位1bit,无奇偶校验;

// 4、每发送1After the bytes upuart_tx_done一个周期,Can be used for subsequent multi-byte module.

// *******************************************************************************************************

module uart_tx

#(

parameter integer BPS = 9_600 , //发送波特率

parameter integer CLK_FRE = 50_000_000 //主时钟频率

)

(

//系统接口

input sys_clk , //系统时钟

input sys_rst_n , //系统复位,低电平有效

//用户接口

input [7:0] uart_tx_data , //需要通过UART发送的数据,在uart_tx_en为高电平时有效

input uart_tx_en , //Send the effective,当其为高电平时,On behalf of the need to send data valid at this time

//UART发送

output reg uart_tx_done , //成功发送1BYTEData after raising a cycle

output reg uart_txd //UART发送数据线tx

);

//param define

localparam integer BPS_CNT = CLK_FRE / BPS; //Calculated according to transmission baud rate for eachbitNeed to count more than the system clock

localparam integer BITS_NUM = 10 ; //Send the format to determine the need to sendbit数,10bit = 1起始位 + 8数据位 + 1停止位

//reg define

reg tx_state ; //发送标志信号,Up on behalf of the sending process is ongoing

reg [7:0] uart_tx_data_reg ; //寄存要发送的数据

reg [31:0] clk_cnt ; //计数器,Is used to count to send abitThe data needed on the number of clock

reg [3:0] bit_cnt ; //bit计数器,Marks the current sent how manybit

//When can send make signal arrived,Check to send data in order to avoid subsequent changes、丢失

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

uart_tx_data_reg <=8'd0;

else if(uart_tx_en) //To send effective data

uart_tx_data_reg <= uart_tx_data; //Check needs to send data

else

uart_tx_data_reg <= uart_tx_data_reg;

end

//When can send make signal arrived,进入发送过程

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

tx_state <=1'b0;

else if(uart_tx_en)

tx_state <= 1'b1; //Send signals effectively, in the process of sending

//Send out the final data is sent process

else if((bit_cnt == BITS_NUM - 1'b1) && (clk_cnt == BPS_CNT - 1'b1))

tx_state <= 1'b0;

else

tx_state <= tx_state;

end

//To send data to end up sent signals a cycle,Indicating a byte is sent

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

uart_tx_done <=1'b0;

//To send data to end up sent signals a cycle

else if((bit_cnt == BITS_NUM - 1'b1) && (clk_cnt == BPS_CNT - 1'b1))

uart_tx_done <=1'b1;

else

uart_tx_done <=1'b0;

end

//进入发送过程后,Start the clock counter and send the numberbit计数器

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)begin

clk_cnt <= 32'd0;

bit_cnt <= 4'd0;

end

else if(tx_state) begin //在发送状态

if(clk_cnt < BPS_CNT - 1'd1)begin //一个bit数据没有发送完

clk_cnt <= clk_cnt + 1'b1; //时钟计数器+1

bit_cnt <= bit_cnt; //bit计数器不变

end

else begin //一个bit数据发送完了

clk_cnt <= 32'd0; //Empty the clock counter,重新开始计时

bit_cnt <= bit_cnt+1'b1; //bit计数器+1,Said to send over abit的数据

end

end

else begin //Is not in the delivery status

clk_cnt <= 32'd0; //清零

bit_cnt <= 4'd0; //清零

end

end

//根据发送数据计数器来给uart发送端口赋值

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

uart_txd <= 1'b1; //The default for high status,空闲状态

else if(tx_state) //处于发送状态

case(bit_cnt) //Data sent from low to high

4'd0: uart_txd <= 1'b0; //起始位,拉低

4'd1: uart_txd <= uart_tx_data_reg[0]; //Send the lowest data

4'd2: uart_txd <= uart_tx_data_reg[1]; //

4'd3: uart_txd <= uart_tx_data_reg[2]; //

4'd4: uart_txd <= uart_tx_data_reg[3]; //

4'd5: uart_txd <= uart_tx_data_reg[4]; //

4'd6: uart_txd <= uart_tx_data_reg[5]; //

4'd7: uart_txd <= uart_tx_data_reg[6]; //

4'd8: uart_txd <= uart_tx_data_reg[7]; //发送最高位数据

4'd9: uart_txd <= 1'b1; //终止位,拉高

default:uart_txd <= 1'b1;

endcase

else //Not in the delivery status

uart_txd <= 1'b1; //The default for high status,空闲状态

end

endmodule 3、Any method to realize the bytes sent

A serial port to send driver module foreign ports is as follows:

其中uart_tx_doneThe signal is the key.When a byte of data is according to the serial port protocol to send out,The signal will be raising a clock cycle,Said a transmitting end.

Can be in after sending a byte,Send the signal as the next byte enabling signal,Until all the bytes are sent.

But there is a need to pay attention to the problem:The first byte sent can make reference signal is not uart_tx_done,So when the first signal to send?同样的,In any bytes sent an external signal module design:uart_bytes_en,Only when the signal effectively initiate a transfer,The signal at the same time also can be used as the first byte sent can make signal,如下:

总结一下,More bytes sent logic:

- 1、Convey more bytes sent can make+多字节数据

- 2、According to many bytes sent to minimum to send bytes(最低8bit),As for the first time send a single-byte

- 3、According to the single byte is sent indicating signal,Start sending a second single-byte,The multi-byte time lowbyte

- 4、All single byte is sent after the completion of,拉高uart_bytes_done,Said a multibyte sending end

完整代码如下:

// *******************************************************************************************************************

// ** 作者 : 孤独的单刀

// ** 邮箱 : [email protected]

// ** 博客 : https://blog.csdn.net/wuzhikaidetb

// ** 日期 : 2022/07/31

// ** 功能 : 1、基于FPGAThe serial interface of bytes sent module;

// 2、Can be set up of the number of bytes at a time、波特率BPS、主时钟CLK_FRE;

// 3、UARTAgreement is set to start bit1bit,数据位8bit,停止位1bit,无奇偶校验(In the port change,Can only change to send driver source code);

// 4、每发送1After multi-byte up indicator a cycle,Indicating a multibyte sending end;

// 5、Data sent order,先发送低字节、再发送高字节.如:发送16’h12_34,To send a single-byte8'h34,Send a single-byte again8'h12.

// *******************************************************************************************************************

module uart_bytes_tx

#(

parameter integer BYTES = 4 , //发送字节数,单字节8bit

parameter integer BPS = 9_600 , //发送波特率

parameter integer CLK_FRE = 50_000_000 //输入时钟频率

)

(

//系统接口

input sys_clk , //系统时钟

input sys_rst_n , //系统复位,低电平有效

//用户接口

input [(BYTES * 8 - 1):0] uart_bytes_data , //需要通过UARTSend a multibyte data,在uart_bytes_en为高电平时有效

input uart_bytes_en , //Send the effective,当其为高电平时,On behalf of the need to send data valid at this time

//UART发送

output uart_bytes_done , //After successfully sent all bytes data up1个时钟周期

output uart_txd //UART发送数据线tx

);

//reg define

reg [(BYTES*8-1):0] uart_bytes_data_reg; //Register to receive multibyte data

reg work_en; //High level said in the sending state,Low level said idle

reg [9:0] byte_cnt; //Send the number of bytes of the count(Because of lazy directly with10bit计数,最大可以表示1024BYTE,Big probability will not overflow)

reg [7:0] uart_sing_data; //To send a single byte data apart

reg uart_sing_en; //To send a single byte data can make

reg uart_bytes_done_reg; //All bytes sent a shot

reg uart_sing_done_reg; //A single byte data sent a shot

//wire define

wire uart_sing_done; //Completion of a single byte signal

//The end KouFu value

assign uart_bytes_done = uart_bytes_done_reg;

//When can send make signal arrived,Check sent multibyte data so as to avoid subsequent changes、丢失

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

uart_bytes_data_reg <= 0;

else if(uart_bytes_en && ~work_en) //To send effective data,And is not in a state

uart_bytes_data_reg <= uart_bytes_data; //Check needs to send data

else if(uart_sing_done)

uart_bytes_data_reg <= uart_bytes_data_reg >> 8; //发送完一个数据后,The multibyte data moves to the right8bit

else

uart_bytes_data_reg <= uart_bytes_data_reg;

end

//When can send make signal arrived,进入工作状态

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

work_en <= 1'b0;

else if(uart_bytes_en && ~work_en) //To send effective data in working conditions and

work_en <= 1'b1; //进入发送状态

else if(uart_sing_done && byte_cnt == BYTES - 1) //Send out the last byte of data

work_en <= 1'b0; //发送完毕,Quit working condition

else

work_en <= work_en;

end

//In the working state of sending data to count number

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

byte_cnt <= 0;

else if(work_en)begin //In the sending state need to send the number of bytes of the count

if(uart_sing_done && byte_cnt == BYTES - 1) //Count to the maximum value is zero

byte_cnt <= 0;

else if(uart_sing_done) //Send out a single-byte the counter+1

byte_cnt <= byte_cnt + 1'b1;

else

byte_cnt <= byte_cnt;

end

else //Not in the sending state is reset

byte_cnt <= 0;

end

//Play shoot up timing·~·

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

uart_sing_done_reg <= 0;

else

uart_sing_done_reg <= uart_sing_done;

end

//Sending a single byte of data

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

uart_sing_data <= 8'd0;

else if(uart_bytes_en && ~work_en) //Enter the working state after sending the first data immediately

uart_sing_data <= uart_bytes_data[7:0]; //Send the lowest bytes

else if(uart_sing_done_reg) //Send out a byte is sent another

uart_sing_data <= uart_bytes_data_reg[7:0]; //先右移8bit,然后取低8bit

else

uart_sing_data <= uart_sing_data; //保持稳定

end

//Sending a single byte of data can make

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

uart_sing_en <= 1'b0;

else if(uart_bytes_en && ~work_en) //Enter the working state after sending the first data immediately

uart_sing_en <= 1'b1;

else if(uart_sing_done_reg && work_en) //Send out a byte is sent another

uart_sing_en <= 1'b1;

else

uart_sing_en <= 1'b0; //Other times it is0

end

//All data is sent

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

uart_bytes_done_reg <= 1'b0;

else if(uart_sing_done && byte_cnt == BYTES - 1)

uart_bytes_done_reg <= 1'b1;

else

uart_bytes_done_reg <= 1'b0;

end

//Instantiated send driver module

uart_tx #(

.BPS (BPS ),

.CLK_FRE (CLK_FRE )

)

uart_tx_inst(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.uart_tx_data (uart_sing_data ),

.uart_tx_en (uart_sing_en ),

.uart_tx_done (uart_sing_done ),

.uart_txd (uart_txd )

);

endmodule 4、仿真

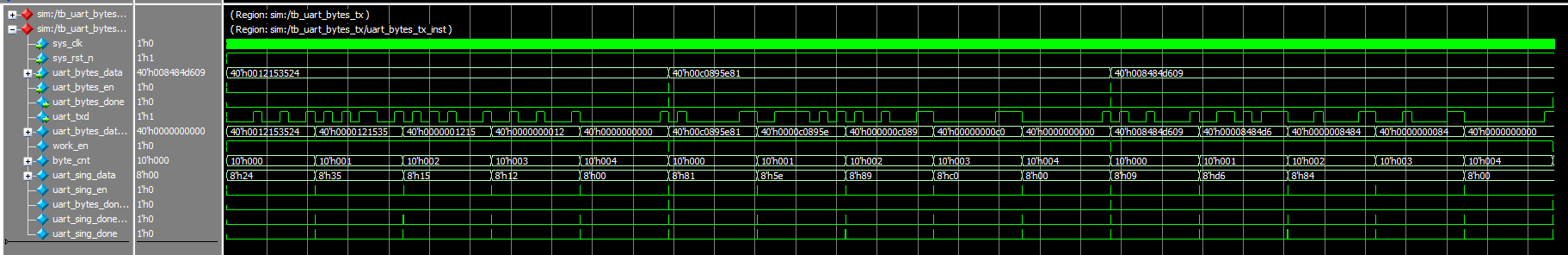

Use the module sends data3次,Observation send results conformed to theUART协议要求.Use single-byte respectively(8位)、双字节(16位)、5字节(40位)进行测试.

4.1、Single-byte simulation

TB如下:

`timescale 1ns/1ns //Define time scale

module tb_uart_bytes_tx();

localparam integer BYTES = 1 ; //The number of bytes at a time

localparam integer BPS = 230400 ; //波特率

localparam integer CLK_FRE = 50_000_000 ; //系统频率50M

reg sys_clk ; //系统时钟

reg sys_rst_n ; //系统复位,低电平有效

reg [(BYTES * 8 - 1):0] uart_bytes_data ; //需要通过UARTSend a multibyte data,在uart_bytes_en为高电平时有效

reg uart_bytes_en ; //Send the effective,当其为高电平时,On behalf of the need to send data valid at this time

wire uart_bytes_done ; //Successfully sent all theBYTEAfter the data up1个时钟周期

wire uart_txd ; //UART发送数据线

initial begin

sys_clk <=1'b0;

sys_rst_n <=1'b0;

uart_bytes_en <=1'b0;

uart_bytes_data <= 0;

#80 //系统开始工作

sys_rst_n <=1'b1;

//*******************************************************************************

//第1Time send random data

#90 //发送1Random multibyte data

uart_bytes_en <=1'b1;

uart_bytes_data <= {$random}; //生成随机数据

#20

uart_bytes_en <=1'b0;

wait(uart_bytes_done); //Waiting for the sending

//*******************************************************************************

//*******************************************************************************

//第2Time send random data

#20

uart_bytes_en <=1'b1;

uart_bytes_data <= {$random}; //发送1Random multibyte data

#20

uart_bytes_en <=1'b0;

wait(uart_bytes_done); //Waiting for the sending

//*******************************************************************************

//第3Time send random data

#20

uart_bytes_en <=1'b1;

uart_bytes_data <= {$random}; //发送1Random multibyte data

#20

uart_bytes_en <=1'b0;

wait(uart_bytes_done); //Waiting for the sending

//*******************************************************************************

#1000 $finish(); //结束仿真

end

always #10 sys_clk=~sys_clk; //设置主时钟,20ns,50M

//Instantiated multibyte delivery module

uart_bytes_tx #(

.BYTES (BYTES ),

.BPS (BPS ),

.CLK_FRE (CLK_FRE )

)

uart_bytes_tx_inst(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.uart_bytes_data (uart_bytes_data ),

.uart_bytes_en (uart_bytes_en ),

.uart_bytes_done (uart_bytes_done ),

.uart_txd (uart_txd )

);

endmodule 仿真结果如下:

- 该模块调用了3次,To send data respectively8'h24,8'h81,8'h09

- A serial port to send driver to send the same3个数据8'h24,8'h81,8'h09

- In the first time send8'h24为例,A serial port to send the line at this timeTXThe data on the respectively0(起始位) --0--0--1--0--0--1--0--0--1(停止位),According to the data in the previous low,The principle of high in the,即8'b00100100,也就是8'h24

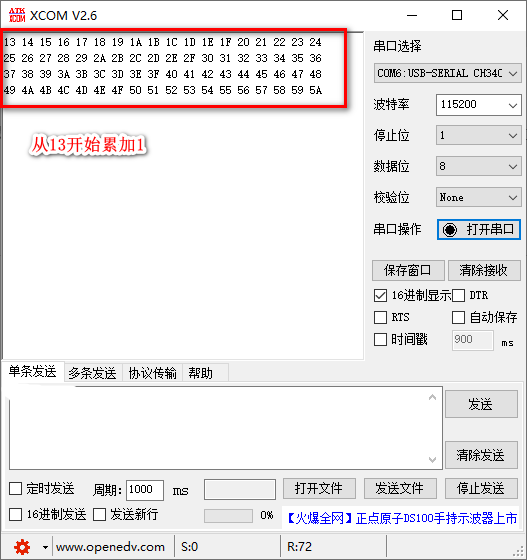

4.2、Double byte simulation

TB基本不用修改,仅仅把BYTESThis parameter into2就行.仿真结果如下:

- 该模块调用了3次,To send data respectively16'h3524,16'h5e81,16'hd609

- A serial port to send driver to send6个数据8'h24,8'h35,8'h81,8'h5e,8'h09,8'hd6

- Based on the principle of starter low byte backwardness high byte,将3A double byte tear open a6A single-byte respectively send

4.3、5Byte simulation

TB基本不用修改,仅仅把BYTESThis parameter into5就行.仿真结果如下:

According to the above logic you see it,我就不啰嗦了.

5、实测

The lower the measured,Need to write a top-level module to instantiated the arbitrary byte serial port to send the module.在顶层模块,设置成每1sPull up a signal,At the same time will send data+1.

5.1、Single-byte measured

顶层模块如下:

// *******************************************************************************************************************

// ** 作者 : 孤独的单刀

// ** 邮箱 : [email protected]

// ** 博客 : https://blog.csdn.net/wuzhikaidetb

// ** 日期 : 2022/07/31

// ** 功能 : 1、对基于FPGASerial port multibyte delivery module test module;

// 2、Set up of the number of bytes at a time、波特率、主时钟频率;

// 3、UARTAgreement is set to start bit1bit,数据位8bit,停止位1bit,无奇偶校验(In the port change,Can only change to send driver source code);

// 4、Data sent order,先发送低字节、再发送高字节.如:发送16’h12_34,To send a single-byte8'h34,Send a single-byte again8'h12.

// *******************************************************************************************************************

module uart_bytes_tx_test(

//系统接口

input sys_clk , //主时钟

input sys_rst_n , //低电平有效的复位信号

//UART发送线

output uart_txd //UART发送线

);

localparam integer BYTES = 1 ; //发送的字节数,单字节8bit

localparam integer BPS = 115200 ; //发送波特率

localparam integer CLK_FRE = 50_000_000 ; //输入时钟频率

localparam integer CNT_MAX = 50_000_000 ; //发送时间间隔,1秒

reg [31:0] cnt_time;

reg uart_bytes_en; //发送使能,当其为高电平时,On behalf of the need to send data at this time

reg [BYTES*8-1 :0] uart_bytes_data; //需要通过UART发送的数据,在uart_bytes_en为高电平时有效

//1s计数模块,每隔1sSend an enabling signal data and pull up a,Increasing data starting from the initial value1

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)begin

cnt_time <= 'd0;

uart_bytes_en <= 1'd0;

uart_bytes_data <= 'h12; //初始数据

end

else if(cnt_time == (CNT_MAX - 1'b1))begin

cnt_time <= 'd0;

uart_bytes_en <= 1'd1; //Up to send can make

uart_bytes_data <= uart_bytes_data + 1'd1; //To send data accumulation1

end

else begin

cnt_time <= cnt_time + 1'd1;

uart_bytes_en <= 1'd0;

uart_bytes_data <= uart_bytes_data;

end

end

//Instantiated serial multibyte delivery module

uart_bytes_tx

#(

.BYTES (BYTES ),

.BPS (BPS ),

.CLK_FRE (CLK_FRE )

)

uart_bytes_tx_inst

(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.uart_bytes_data (uart_bytes_data ),

.uart_bytes_en (uart_bytes_en ),

.uart_bytes_done ( ),

.uart_txd (uart_txd )

);

endmodule

初始值设定为8'h13,This PC per1sYou can receive a data,其值分别为8'h13、8'h14、8'h15、8'h16、8'h17·····,PC receives the data is as follows:

测试结果与预期一致.

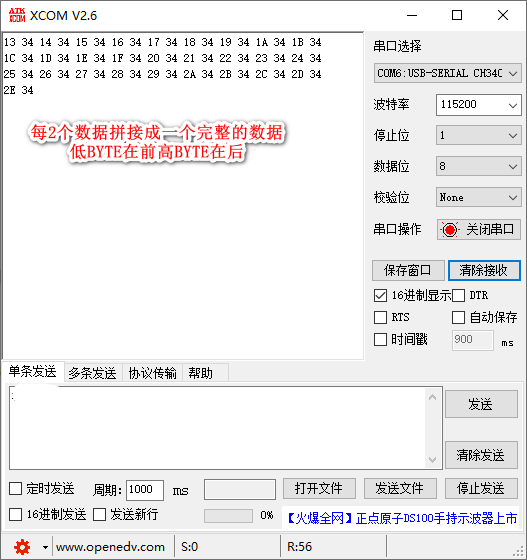

5.2、Double byte measured

顶层模块如下:

// *******************************************************************************************************************

// ** 作者 : 孤独的单刀

// ** 邮箱 : [email protected]

// ** 博客 : https://blog.csdn.net/wuzhikaidetb

// ** 日期 : 2022/07/31

// ** 功能 : 1、对基于FPGASerial port multibyte delivery module test module;

// 2、Set up of the number of bytes at a time、波特率、主时钟频率;

// 3、UARTAgreement is set to start bit1bit,数据位8bit,停止位1bit,无奇偶校验(In the port change,Can only change to send driver source code);

// 4、Data sent order,先发送低字节、再发送高字节.如:发送16’h12_34,To send a single-byte8'h34,Send a single-byte again8'h12.

// *******************************************************************************************************************

module uart_bytes_tx_test(

//系统接口

input sys_clk , //主时钟

input sys_rst_n , //低电平有效的复位信号

//UART发送线

output uart_txd //UART发送线

);

localparam integer BYTES = 2 ; //发送的字节数,单字节8bit

localparam integer BPS = 115200 ; //发送波特率

localparam integer CLK_FRE = 50_000_000 ; //输入时钟频率

localparam integer CNT_MAX = 50_000_000 ; //发送时间间隔,1秒

reg [31:0] cnt_time;

reg uart_bytes_en; //发送使能,当其为高电平时,On behalf of the need to send data at this time

reg [BYTES*8-1 :0] uart_bytes_data; //需要通过UART发送的数据,在uart_bytes_en为高电平时有效

//1s计数模块,每隔1sSend an enabling signal data and pull up a,Increasing data starting from the initial value1

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)begin

cnt_time <= 'd0;

uart_bytes_en <= 1'd0;

uart_bytes_data <= 'h3412; //初始数据

end

else if(cnt_time == (CNT_MAX - 1'b1))begin

cnt_time <= 'd0;

uart_bytes_en <= 1'd1; //Up to send can make

uart_bytes_data <= uart_bytes_data + 1'd1; //To send data accumulation1

end

else begin

cnt_time <= cnt_time + 1'd1;

uart_bytes_en <= 1'd0;

uart_bytes_data <= uart_bytes_data;

end

end

//Instantiated serial multibyte delivery module

uart_bytes_tx

#(

.BYTES (BYTES ),

.BPS (BPS ),

.CLK_FRE (CLK_FRE )

)

uart_bytes_tx_inst

(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.uart_bytes_data (uart_bytes_data ),

.uart_bytes_en (uart_bytes_en ),

.uart_bytes_done ( ),

.uart_txd (uart_txd )

);

endmodule初始值设定为16'h3413,This PC per1sYou can receive a data,其值分别为8'h13、8'h34、8'h14、8'h34、8'h15、8'h34·····,PC receives the data is as follows:

测试结果与预期一致.

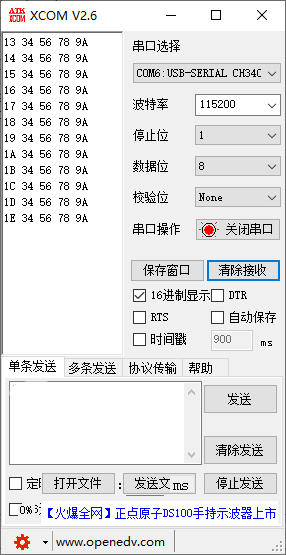

5.3、5Byte measured

顶层模块如下:

// *******************************************************************************************************************

// ** 作者 : 孤独的单刀

// ** 邮箱 : [email protected]

// ** 博客 : https://blog.csdn.net/wuzhikaidetb

// ** 日期 : 2022/07/31

// ** 功能 : 1、对基于FPGASerial port multibyte delivery module test module;

// 2、Set up of the number of bytes at a time、波特率、主时钟频率;

// 3、UARTAgreement is set to start bit1bit,数据位8bit,停止位1bit,无奇偶校验(In the port change,Can only change to send driver source code);

// 4、Data sent order,先发送低字节、再发送高字节.如:发送16’h12_34,To send a single-byte8'h34,Send a single-byte again8'h12.

// *******************************************************************************************************************

module uart_bytes_tx_test(

//系统接口

input sys_clk , //主时钟

input sys_rst_n , //低电平有效的复位信号

//UART发送线

output uart_txd //UART发送线

);

localparam integer BYTES = 5 ; //发送的字节数,单字节8bit

localparam integer BPS = 115200 ; //发送波特率

localparam integer CLK_FRE = 50_000_000 ; //输入时钟频率

localparam integer CNT_MAX = 50_000_000 ; //发送时间间隔,1秒

reg [31:0] cnt_time;

reg uart_bytes_en; //发送使能,当其为高电平时,On behalf of the need to send data at this time

reg [BYTES*8-1 :0] uart_bytes_data; //需要通过UART发送的数据,在uart_bytes_en为高电平时有效

//1s计数模块,每隔1sSend an enabling signal data and pull up a,Increasing data starting from the initial value1

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)begin

cnt_time <= 'd0;

uart_bytes_en <= 1'd0;

uart_bytes_data <= 40'h9a_78_56_34_12; //初始数据

end

else if(cnt_time == (CNT_MAX - 1'b1))begin

cnt_time <= 'd0;

uart_bytes_en <= 1'd1; //Up to send can make

uart_bytes_data <= uart_bytes_data + 1'd1; //To send data accumulation1

end

else begin

cnt_time <= cnt_time + 1'd1;

uart_bytes_en <= 1'd0;

uart_bytes_data <= uart_bytes_data;

end

end

//Instantiated serial multibyte delivery module

uart_bytes_tx

#(

.BYTES (BYTES ),

.BPS (BPS ),

.CLK_FRE (CLK_FRE )

)

uart_bytes_tx_inst

(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.uart_bytes_data (uart_bytes_data ),

.uart_bytes_en (uart_bytes_en ),

.uart_bytes_done ( ),

.uart_txd (uart_txd )

);

endmodule初始值设定为40'h9a78563413,This PC per1sYou can receive a data,其值分别为8'h13、8'h34、8'h56、8'h78、8'h9a、8'h14、8'h34、8'h56、8'h78、8'h9a、·····,PC receives the data is as follows:

测试结果与预期一致.

- 工程源码(nk20):点击这里下载

- 博客主页:wuzhikai.blog.csdn.net

- 本文由 孤独的单刀 原创,首发于CSDN平台

- 您有任何问题,都可以在评论区和我交流!

- 创作不易,您的支持是我持续更新的最大动力!如果本文对您有帮助,还请多多点赞、评论和收藏!

边栏推荐

猜你喜欢

OSG Notes: Set DO_NOT_COMPUTE_NEAR_FAR to manually calculate far and near planes

仿牛客论坛项目

进行交互或动画时如何选择Visibility, Display, and Opacity

What is the difference between a utility model patent and an invention patent?Understand in seconds!

4.1 配置Mysql与注册登录模块

启明云端分享|盘点ESP8684开发板有哪些功能

面试突击70:什么是粘包和半包?怎么解决?

WeChat applet cloud development | personal blog applet

SIPp 安装及使用

面试突击70:什么是粘包和半包?怎么解决?

随机推荐

excel高级绘图技巧100讲(二十二)-如何对不规则数据进行分列

用户身份标识与账号体系实践

有点奇怪!访问目的网址,主机能容器却不行

字符串

【多任务优化】DWA、DTP、Gradnorm(CVPR 2019、ECCV 2018、 ICML 2018)

【nn.Parameter()】生成和为什么要初始化

【Untitled】

LTE时域、频域资源

自定义指令,获取焦点

Use WeChat official account to send information to designated WeChat users

宝塔搭建PESCMS-Ticket开源客服工单系统源码实测

Protocol Buffer usage

Batch get protein .pdb files based on Uniprot ID/PDB ID

泰德制药董事长郑翔玲荣膺“2022卓越影响力企业家奖” 泰德制药荣获“企业社会责任典范奖”

模板特例化和常用用法

【torch】张量乘法:matmul,einsum

小数据如何学习?吉大最新《小数据学习》综述,26页pdf涵盖269页文献阐述小数据学习理论、方法与应用

[Personal work] Wireless network image transmission module

idea插件generateAllSetMethod一键生成set/get方法以及bean对象转换

StringTable Detailed String Pool Performance Tuning String Concatenation