当前位置:网站首页>吃透Chisel语言.08.Chisel基础(五)——Wire、Reg和IO,以及如何理解Chisel生成硬件

吃透Chisel语言.08.Chisel基础(五)——Wire、Reg和IO,以及如何理解Chisel生成硬件

2022-07-04 12:49:00 【github-3rr0r】

Chisel基础(五)——Wire、Reg和IO,以及如何理解Chisel生成硬件

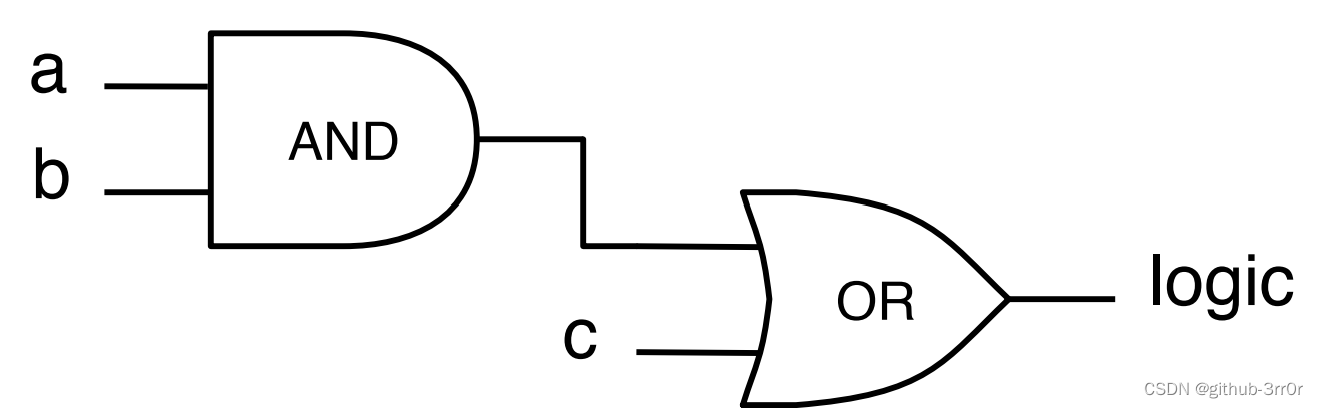

上一篇的结语中提到,UInt、SInt和Bits都是Chisel类型,它们本身是不直接表示硬件的,只有把它们封装成为Wire、Reg或IO才会生成电路。这件事可以这么理解,数字逻辑电路是由连线、逻辑门、寄存器和输入输出(包括时钟和复位信号)等组成的,其中连线对应Wire,逻辑门对应运算符,寄存器对应Reg,输入输出对应IO。那么在Chisel中它们到底怎么使用呢?又如何理解Chisel生成电路呢?这一篇文章一起学习一下。

Wire、Reg和IO

在Chisel中,Wire用于表示组合逻辑,Reg用于表示寄存器(D-触发器的集合),而IO则用于表示一个模块的接口(比如某个具体的集成电路的引脚)。前面也提到,Wire、Reg和IO可以封装任何Chisel类型,当然也包括Bundle和Vec。

在Scala中,变量分为var和val两种类型,前者是可变的,后者是不可变的。而在Chisel中,我们只需要使用val来描述电路,即不可变的Scala变量,比如:

val number = Wire(UInt())

val reg = Reg(SInt())

我们可以在声明后再将值或表达式赋值或重新赋值给Wire、Reg或IO,用到的Chisel操作符是:=:

number := 10.U

reg := value - 3.U

这里显然和Scala中的赋值操作符=是不一样的。这两种操作符怎么用呢?很简单,在创建一个硬件对象的时候我们使用Scala操作符=,而在给已经存在的硬件对象赋值或重新赋值的时候,就使用Chisel操作符:=。

组合逻辑值也是可以条件赋值的,但是需要在条件的每个分支都赋值。否则的话,会引入锁存器(latch),这是Chisel编译器不接受的。最好的办法就是在创建Wire的时候就给定一个默认值,因此,前面的代码这样写更好:

val number = WireDefault(10.U(4.W))

同理,之前提到过,Chisel会为信号和寄存器推断需要的位宽,但是最好还是在创建硬件对象的时候指定想要的位宽。在大多数场合,给寄存器一个已知的复位初始化值也是最好的:

val reg = RegInit(0.S(8.W))

RegInit和WireDefault稍有不同,前者指的是复位时的值,而后者指的是默认连接。

至于IO,用于声明一个模块的接口,用法通常如下:

val io = IO(new Bundle {

val in_a = Input(UInt(8.W))

val out_b = Output(UInt(8.W))

})

IO()里面是个bundle的实例,bundle内是输入输出接口,分别用Input和Output封装。这里仅简单介绍,后面会展开讲述。

如何理解Chisel生成硬件

我们到现在为止,已经解除了一些Chisel的基本代码,看起来跟传统的编程语言比如C和Java这种差不多。但是,Chisel和其他硬件描述语言一样,确实是定义硬件组件的。区别在哪里呢?在软件中,代码是一行一行按顺序执行的,而在硬件中所有的代码行是并行执行的。

写Chisel的时候一定要牢记Chisel确实是生成硬件的。你可以想象,或者在纸上画,一个个由我们写的Chisel电路描述生成的模块。每次创建一个组件,都会添加一个硬件,每条赋值语句,都会生成一个门电路和/或触发器。

那么从技术上来讲,Chisel在执行代码的时候,是执行的Scala程序,然后通过执行Chisel语句,集合(collect)所有的硬件组件并把这些节点连接起来。这些硬件节点构成的网络就是Chisel生成的硬件,可以生成为Verilog代码用于ASIC或FPGA综合,也可以用Chisel tester进行测试。这些硬件节点构成的网络就是完全并行执行的!

对于之前写软件的人来讲理解这种并行执行可能有点困难,因为它跟软件的并行程序还不一样,硬件就是天然并行的,不需要把程序分配给各个线程,也不需要为线程间通信搞什么加锁,就是很简单的并行执行,电流在硬件的每一部分同时运转,仅此而已。

结语

刚接触硬件描述语言的时候,我也很困惑,经常用写软件的思维来写硬件,最后写完的东西完全不是想象中的样子。只能把写软件的思维收一收,简单地把写硬件理解为搭积木,我们要做的工作就是把它们有逻辑地连接起来。

到目前为止,我们还没运行过代码,只是学习了基础的Chisel语法。下一篇文章,我们会学习如何利用sbt构建我们的Chisel项目并运行,同时也简单介绍Chisel的工具流,敬请期待。

边栏推荐

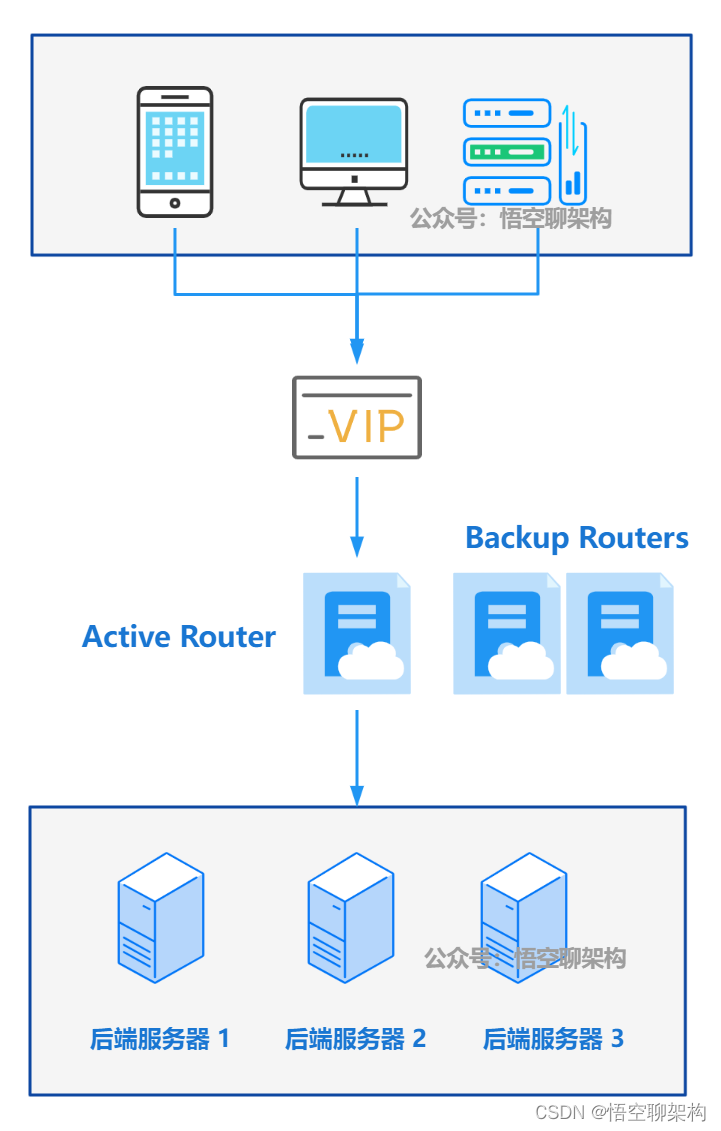

- Haproxy high availability solution

- golang fmt.printf()(转)

- 自主工业软件的创新与发展

- Understanding and difference between viewbinding and databinding

- Fs4056 800mA charging IC domestic fast charging power IC

- How to choose a technology stack for web applications in 2022

- . Net using redis

- #yyds干货盘点# 解决名企真题:连续最大和

- 字节面试算法题

- 中邮科技冲刺科创板:年营收20.58亿 邮政集团是大股东

猜你喜欢

一次 Keepalived 高可用的事故,让我重学了一遍它

字节面试算法题

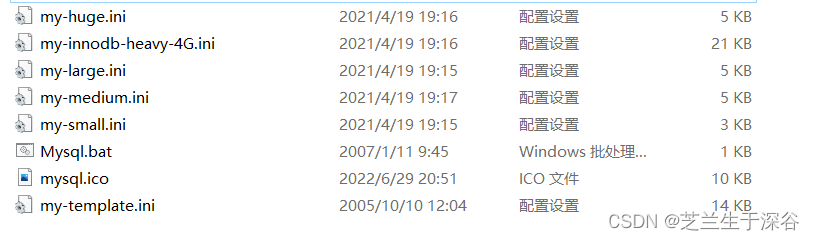

MySQL5免安装修改

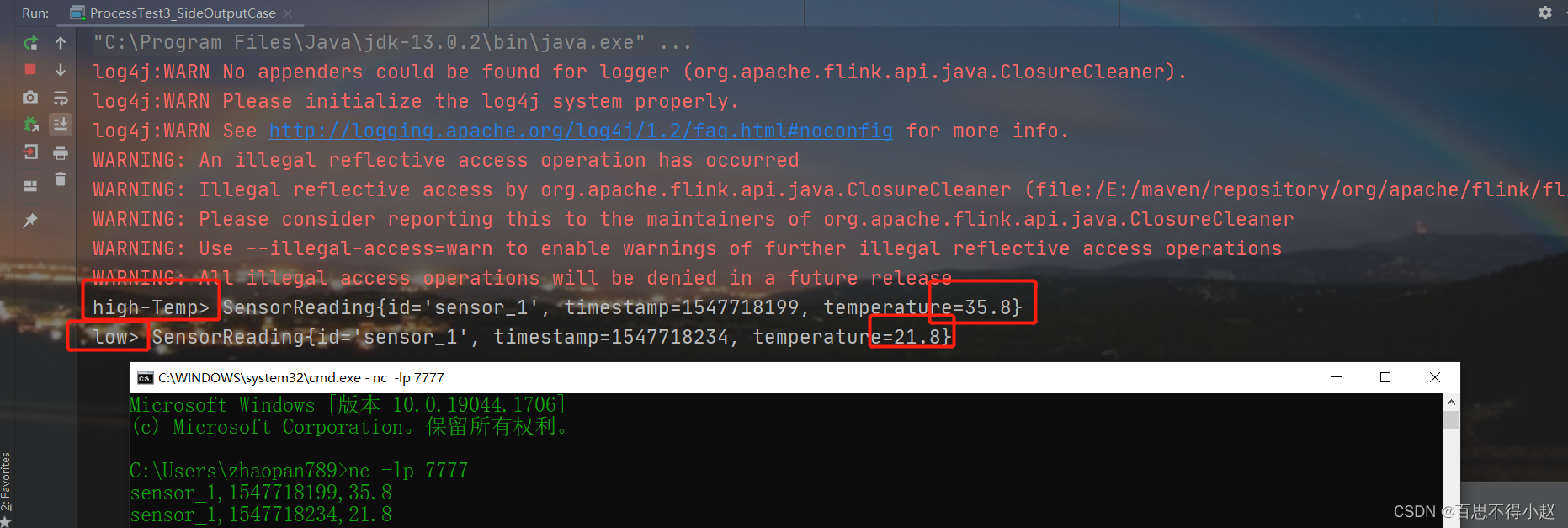

结合案例:Flink框架中的最底层API(ProcessFunction)用法

華昊中天沖刺科創板:年虧2.8億擬募資15億 貝達藥業是股東

Doctoral application | West Lake University Learning and reasoning system laboratory recruits postdoctoral / doctoral / research internship, etc

2022g3 boiler water treatment examination question simulation examination question bank and simulation examination

基于链表管理的单片机轮询程序框架

Automatic filling of database public fields

吃透Chisel语言.05.Chisel基础(二)——组合电路与运算符

随机推荐

Fs4056 800mA charging IC domestic fast charging power IC

MySQL45讲——学习极客时间MySQL实战45讲笔记—— 06 | 全局锁和表锁_给表加个字段怎么有这么多阻碍

美国土安全部长:国内暴力极端主义是目前美面临的最大恐怖主义威胁之一

好博医疗冲刺科创板:年营收2.6亿 万永钢和沈智群为实控人

Summary of recent days (non-technical article)

30: Chapter 3: develop Passport Service: 13: develop [change / improve user information, interface]; (use * * * Bo class to accept parameters, and use parameter verification)

Programmer anxiety

. Net delay queue

XML入门二

Secretary of Homeland Security of the United States: domestic violent extremism is one of the biggest terrorist threats facing the United States at present

CVPR 2022 | 大幅减少零样本学习所需的人工标注,提出富含视觉信息的类别语义嵌入(源代码下载)...

Fisher信息量检测对抗样本代码详解

Source code compilation and installation of MySQL

ViewBinding和DataBinding的理解和区别

免费、好用、强大的轻量级笔记软件评测:Drafts、Apple 备忘录、Flomo、Keep、FlowUs、Agenda、SideNote、Workflowy

苹果5G芯片研发失败:继续依赖高通,还要担心被起诉?

C array supplement

读取 Excel 表数据

Detailed explanation of Fisher information quantity detection countermeasure sample code

Go 语言入门很简单:Go 实现凯撒密码