当前位置:网站首页>PS + PL heterogeneous multicore case development manual for Ti C6000 tms320c6678 DSP + zynq-7045 (3)

PS + PL heterogeneous multicore case development manual for Ti C6000 tms320c6678 DSP + zynq-7045 (3)

2022-07-26 15:38:00 【Tronlong Chuang long】

This paper mainly introduces ZYNQ PS + PL Instructions for heterogeneous multi-core cases , Applicable development environment :Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4. The test board is TMS320C6678 Development board , The article contains several characteristic cases , Such as axi_gpio_led_demo Case study 、axi_timer_pwm_demo Case study 、axi_uart_demo Case study 、emio_gpio_led_demo Case study 、mig_dma Case etc. , Because the length is too long , The article is divided into upper and lower 6 Section display , Welcome to check the content of the article in order .

The test board is TMS320C6678 Development board , It is based on TI KeyStone framework C6000 series TMS320C6678 Eight cores C66x Fixed point / floating-point DSP, as well as Xilinx Zynq-7000 series XC7Z045/XC7Z100 SoC High end heterogeneous multi-core evaluation board for processor design ,TMS320C6678 The dominant frequency of each core of the development board can be as high as 1.25GHz,XC7Z045/XC7Z100 Integrate PS End binuclear ARM Cortex-A9 + PL End Kintex-7 framework 28nm Programmable logic resources , Lead out two way CameraLink、 dual SFP+ Smooth mouth 、 Four Gigabit Ethernet ports 、 dual SATA、 dual PCIe、 Four way USB、 dual CAN、 dual CAMERA、HDMI IN/OUT、LVDS、LCD、RS485、RS232、Micro SD、HPC FMC Such as the interface .

mig_dma Case study

Case function

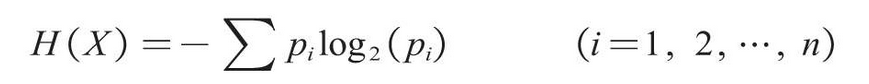

Case function :PS End pass AXI4-Lite Bus control AXI DMA, Put the data in DDR And BRAM Carry it between , To test DDR Read / write rate and bit error rate .

because PS End Master GP Other peripherals are connected to the interface , therefore PS End mapping PL End DDR The maximum memory space of is 1GByte.

Operation instructions

load PS End bare metal program 、PL After the end program , You can see PS The end serial port debugging terminal prints the following information .

chart 128

Case configuration PL End DDR The theoretical maximum bandwidth is :533MHz*2*32bit=4264MByte/s. The test results are as follows :

surface 1

read / Write rate | Minimum speed | Maximum speed | Average rate |

Write rate | 3821.32MByte/s | 3829.36MByte/s | 3824.52MByte/s |

Read rate | 3601.01MByte/s | 3607.63MByte/s | 3604.41MByte/s |

Key code (PS End )

Initialize and calibrate Timer.

chart 129

initialization DMA equipment , Use polling mode , close DMA interrupt .

chart 130

obtain DDR Actual effective capacity .

chart 131

DDR Data line test .

chart 132

DDR Address line test .

chart 133

start-up DMA transmission , Use Timer time , wait for DMA Calculate the data transmission rate after transmission .

chart 134

Conduct DDR -> DMA -> BRAM Data transmission test .

chart 135

Conduct BRAM -> DMA -> DDR Data transmission test .

chart 136

Update relevant information about rate test after transmission , Including the minimum value 、 Maximum and average .

chart 137

After each transmission , Verify the transmitted data .

chart 138

Vivado Project description

Click on BLOCK DESIGN Under window "Address Editor" Options , see IP Nuclear address , The address allocation is shown in the figure below .

chart 139

IP Nuclear configuration

AXI DMA IP nucleus

Use in this case AXI DMA IP Nuclear data in DDR And BRAM Carry it between .

AXI DMA(AXI Direct Memory Access) IP Nuclear development documents are product materials “6- Development reference \Xilinx Official references \” In the catalog 《pg021_axi_dma.pdf》, The specific configuration is as follows .

- Cancel the default check Enable Scatter Gather Engine Options , To configure DMA The working mode is direct register mode (Direct Register Mode).

- Width of Buffer Length Register Set to 23, be DMA The maximum addressing range of a single transmission is 2^(Width of Buffer Length Register),DMA The maximum amount of data transmitted in a single time is 2^(Width of Buffer Length Register)*8=8MByte.

- read / Write channel Memory Map Data Width、Stream Data Width All set to 512,Max Burst Size All set to 64.

chart 140

MIG 7 Series IP nucleus

Use in this case MIG 7 Series IP Nuclear complete DDR Initialization and read / write verification of .

MIG(Memory Interface Generator) 7 Series IP Nuclear development documents are product materials “6- Development reference \Xilinx Official references \” In the catalog 《ds176_7Series_MIS.pdf》 and 《ug586_7Series_MIS.pdf》, The specific configuration is as follows .

Memory Selection choice DDR3 SDRAM.

chart 141

adopt Controller Options To configure DDR3 Parameters .

Clock Period Set to 1875ps( That is, the bus frequency is 533.33MHz),DDR The transmission rate is 533.33x2≈1066Mb/s.

chart 142

PHY to Controller Clock Ratio Set to 4:1, Configure through this parameter IP Core user clock ui_clk frequency .DDR Clock Period by 533.33MHz, Such as PHY to Controller Clock Ratio Configure to 4:1, be ui_clk The clock frequency is 533.33/4=133.33MHz.

Memory Part Set to MT41K512M16XX-107, compatible MT41K256M16XX-107.

Data Width Set to 32.

Number of Bank Machines Set to 8.

The maximum theoretical bandwidth is :533.33MHz*2*32bit/8≈4264MByte/s.

chart 143

AXI The bit width is set to 256bit.

chart 144

adopt Memory Options To configure IP Core input clock . Select... Here 200MHz, Address mapping is selected as RBC(ROW/BANK/COLUMN) Pattern .

chart 145

chart 146

FPGA Options configuration option ,System Clock choice "No Buffer",Reference Clock choice "Use System Clock".

chart 147

IO Planning Options choice "Fixed Pin Out:Pre-existing pin out is known and fixed".

chart 148

Pin Selection configuration option , Click on "Read XDC/UCF", Select project "mig_dma.srcs\constrs_1\imports\constraints\" The next path mig_dma_tl6678zh.ucf Import it into , Click again Vaildate Verify the pins , Click OK.

chart 149

Click on Next, Until the following interface appears , choice Accept.

chart 150

Click on Next, Until the following interface appears , choice Generate Can finish IP Nuclear configuration .

chart 151

AXI BRAM Controller IP nucleus

Use in this case AXI BRAM Controller IP Nuclear creation BRAM controller .

AXI BRAM Controller IP Nuclear development documents are product materials “6- Development reference \Xilinx Official references \” In the catalog 《pg078-axi-bram-ctrl.pdf》, The specific configuration is as follows .

FCLK_CLK1 Output 200MHz The clock serves as BRAM The working clock of .

chart 152

chart 153

stay BLOCK DESIGN Interface "Address Editor" Configuration in options BRAM The size is 1MByte.

chart 154

The configuration data bit width is 256,BRAM The number of interfaces is 1.

chart 155

Block Memory Generator IP nucleus

Use in this case Block Memory Generator IP Nuclear creation BRAM resources .

Block Memory Generator IP Nuclear development documents are product materials “6- Development reference \Xilinx Official references \” In the catalog 《pg058-blk-mem-gen.pdf》, The specific configuration is as follows .

chart 156

AXI Timer IP nucleus

Use in this case AXI Timer IP Count the nuclei , Used to calculate the data transmission rate .

AXI Timer IP Nuclear development documents are product materials “6- Development reference \Xilinx Official references \” In the catalog 《pg079-axi-timer.pdf》, The specific configuration is as follows .

chart 157

AXI GPIO IP nucleus

Use in this case AXI GPIO IP Nuclear reading MIG 7 Series IP Nuclear init_calib_complete Pin value , To judge DDR The state of . When MIG 7 Series IP Nuclear complete DDR After initialization and read / write verification of ,init_calib_complete The pins will be pulled up .

AXI GPIO IP Nuclear development documents are product materials “6- Development reference \Xilinx Official references \” In the catalog 《pg144-axi-gpio.pdf》, The specific configuration is as follows .

chart 158

According to the development documentation , Through registers GPIO_TRI Can be GPIO Configure as input / The output mode ; Through registers GPIO_DATA Can be GPIO Configure as high / Low level , And readable GPIO The level state of .

chart 159

chart 160

chart 161

aurora_dma Case study

Case function

Case function :PS End pass AXI4-Lite Bus control AXI DMA, Put the data in BRAM And SFP+ Carry between smooth ports , To test SFP+ The data transmission rate and bit error rate of the external loop of the optical port ,SFP+ Optical port is based on Aurora Protocol for data transmission .

chart 162 Program function block diagram

Operation instructions

Will evaluate the board ZYNQ The end start mode selection dial switch is set to 00(1~2), This gear is JTAG Pattern . Use Micro USB Wire connection PC Machine and evaluation board CON9(USB TO UART) Interface , And connect correctly PS End debugging serial port . Use RS232 Cross serial bus 、USB turn RS232 Male serial port cable , Will evaluate the board PL End debugging serial port CON19(RS232) Connect to PC The machine USB Interface .

Will a SFP+ Multimode dual fiber optical module access SFP1 Smooth mouth , And use an optical fiber cable to connect the RX And TX Connect , Form an external loop .SFP1 Optical port uses GTX Quad 110 Of MGTXRX_3、MGTXTX_3 Pin .

chart 163

be based on PS End bare metal testing

load PS End bare metal program aurora_dma_a9.elf、PL After the end program , You can see PS Terminal serial port debugging terminal printing SFP+ Data transmission test information of the external loop of the optical port . In this case GTX The bandwidth is configured as 10Gbps, That is, the theoretical speed is 1250MB/s.

chart 164

The following information can be obtained from the above figure :

- SFP+ The data transmission rate of the external loop of the optical port is 1145MB/s.

- SFP+ The bit error rate of data transmission of the external loop of the optical port is 0.

be based on PL End MicroBlaze test

Take this case PL End Vivado Project executable document aurora_dma_xxx.bin Copy to the evaluation board file system "/lib/firmware/" Under the table of contents , then PL End "baremetal_demo\bin\" In the catalog MicroBlaze Applications aurora_dma_microblaze.bin and PS End application tl_devmem_rw Copy to any same path of the evaluation board file system .

Execute the following command , load MicroBlaze Application to PS End DDR Of 0x18000000 Address .

Target# ./tl_devmem_rw -w -a 0x18000000 -s 100000 -o byte -f aurora_dma_microblaze.bin

chart 165

Execute the following command , load PL End Vivado Project executable document .

Target# echo aurora_dma_xc7z045.bin > /sys/class/fpga_manager/fpga0/firmware

After execution of the above order , You can see PL Terminal serial port debugging terminal printing SFP+ Data transmission test information of the external loop of the optical port . In this case GTX The bandwidth is configured as 10Gbps, That is, the theoretical speed is 1250MB/s.

chart 166

The following information can be obtained from the above figure :

- SFP+ The data transmission rate of the external loop of the optical port is 1145MB/s.

- SFP+ The bit error rate of data transmission of the external loop of the optical port is 0.

Key code (PS End bare metal /PL End MicroBlaze)

Initialize and calibrate Timer.

chart 167

initialization DMA equipment .

chart 168

Use polling mode , close DMA interrupt .

chart 169

Based on the open Aurora Agreed GTX Data transmission rate and bit error rate test , Build the packets to be sent for each transmission .

chart 170

Go to separately DMA The device writes the source address 、 Destination address and data volume , And start the DMA transmission .

chart 171

start-up DMA After transmission , Use Timer time , wait for DMA Calculate the data transmission rate after transmission .

chart 172

After each transmission , Verify the transmitted data .

chart 173

chart 174

Calculate the average data transmission rate and bit error rate .

chart 175

Vivado Project description

Click on BLOCK DESIGN Under window "Address Editor" Options , see IP Nuclear address , The address allocation is shown in the figure below .

chart 176

modular /IP Nuclear configuration

AXI DMA IP nucleus

Use in this case AXI DMA(AXI Direct Memory Access) IP Nuclear data in BRAM And SFP+ Carry between smooth ports .

AXI DMA IP Nuclear development documents are product materials “6- Development reference \Xilinx Official references \” In the catalog 《pg021_axi_dma.pdf》, The specific configuration is as follows .

- Cancel the default check Enable Scatter Gather Engine Options , To configure DMA The working mode is direct register mode (Direct Register Mode).

- Width of Buffer Length Register Set to 23, be DMA The maximum addressing range of a single transmission is 2^(Width of Buffer Length Register),DMA The maximum amount of data transmitted in a single time is 2^(Width of Buffer Length Register)*8=8MByte.

- read / Write channel Memory Map Data Width、Stream Data Width All set to 64,Max Burst Size All set to 256.

- m_axi_mm2s_aclk and m_axi_s2mm_aclk Use by Aurora 64B66B IP nucleus usr_clk_out Output 156.25MHz The clock .

chart 177

chart 178

AXI BRAM Controller IP nucleus

Use in this case AXI BRAM Controller IP Nuclear creation BRAM controller .

AXI BRAM Controller IP Nuclear development documents are product materials “6- Development reference \Xilinx Official references \” In the catalog 《pg078-axi-bram-ctrl.pdf》, The specific configuration is as follows .

FCLK_CLK1 Output 200MHz The clock serves as BRAM The working clock of .

chart 179

chart 180

stay BLOCK DESIGN Interface "Address Editor" Configuration in options BRAM The size is 512KByte.

chart 181

The configuration data bit width is 512,BRAM The number of interfaces is 1.

chart 182

边栏推荐

- 谷歌尝试为ChromeOS引入密码强度指示器以提升线上安全性

- Using two stacks to implement a queue

- 请问参数化视图可以根据传入参数的特点得到不同行数的SQL吗?比如这里我想根据传输参数@field中列

- 【C】 Flexible array

- [leetcode daily question] - 121. The best time to buy and sell stocks

- Desktop application layout

- Credit card number recognition (openCV, code analysis)

- promise,async-await 和 跨域问题的解决--代理服务器的原理

- 蓝牙BLE4.0-HM-10设备配对指南

- 【EXPDP导出数据】expdp导出23行记录,且不包含lob字段的表,居然用时48分钟,请大家帮忙看看

猜你喜欢

筑牢生态安全防线,广州开展突发环境事件应急演练

anaconda No module named ‘cv2‘

桌面应用布局图

What is the transport layer protocol tcp/udp???

How much help does solid state disk have for game operation

白话详解决策树模型之使用信息熵构建决策树

TI C6000 TMS320C6678 DSP+ Zynq-7045的PS + PL异构多核案例开发手册(4)

持续集成(二)Jenkins基本使用介绍

![[leetcode daily question] - 268. Missing numbers](/img/96/dcf18522257dea7cb7e52f5bb7ced3.png)

[leetcode daily question] - 268. Missing numbers

VS添加作者信息和时间信息的设置

随机推荐

阿里巴巴一面 :十道经典面试题解析

TI C6000 TMS320C6678 DSP+ Zynq-7045的PS + PL异构多核案例开发手册(3)

Continuous integration (II) introduction to the basic use of Jenkins

数仓:爱奇艺数仓平台建设实践

【静态代码质量分析工具】上海道宁为您带来SonarSource/SonarQube下载、试用、教程

R语言ggplot2可视化:可视化折线图、使用aes函数中的group参数为不同分组可视化折线图

Deep packet inspection using cuckoo filter paper summary

No module named ‘win32gui‘

R语言ggplot2可视化:使用ggpubr包的ggballoonplot函数可视化气球图(可视化由两个分类变量组成的列联表)、配置guides函数中的size参数指定不显示数据点大小的图例

原来卡布奇诺信息安全协会是干这个的呀,一起来看看吧。

Creation and traversal of binary tree

[leetcode daily question] - 268. Missing numbers

Data preprocessing of data mining

Is there any need for livedata to learn—— Jetpack series (2)

Qt最基本的布局,创建window界面

Zhaoqi science and technology innovation high-end talent project was introduced and implemented, mass entrepreneurship and innovation competition was organized, and online live roadshow was broadcast

Soft test (VII) performance test (1) brief introduction

NAT/NAPT地址转换(内外网通信)技术详解【华为eNSP】

[leetcode daily question] - 121. The best time to buy and sell stocks

Digital warehouse: iqiyi digital warehouse platform construction practice