当前位置:网站首页>【Note17】PECI(Platform Environment Control Interface)

【Note17】PECI(Platform Environment Control Interface)

2022-07-05 22:50:00 【Coder programming record】

List of articles

1. Mode and command introduction

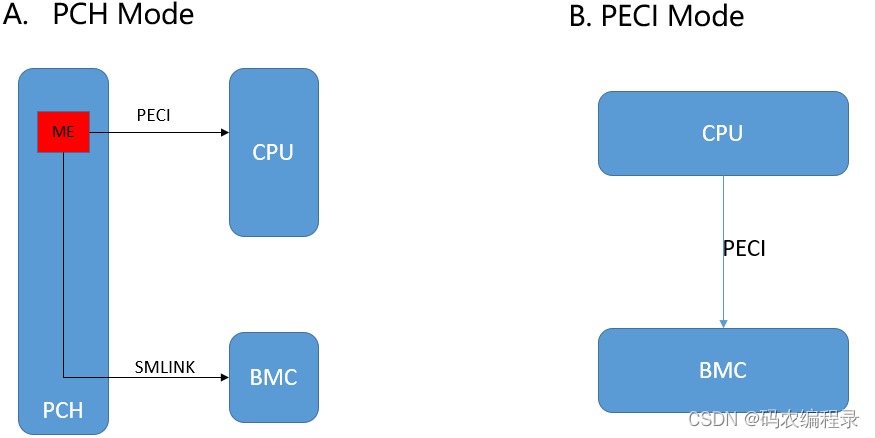

peci yes intel Private agreement provided ,openbmc By intel Authorized by the , Others cannot be used without authorization . The hardware consists of a wire , Unlike i2c Yes, there is 2 Root line .peci1.1 Only support CPU temperature ,2.0 Increase support MSR Related registers ,3.0 Add support for reading intel Of PCI To configure .PCI Mainly based on intel Of BDF【Bus/Device/Function (PCI technology)】 Confirm reading pcie The register address in the device . as follows peci There are two ways to request :AMIbmc yes A,obmc With B.

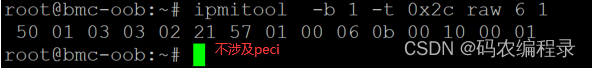

1.PCH Pattern :cpu There is usually one ME The address is hung on smlink On ,-b Just hang up bus Number ( The simple understanding is i2c Of bus Number ),-t It's the hanging address , It's usually 0x2c.BMC adopt IPMI to ME Send a raw date command ,ME Reissue pcie Order to cpu. the truth is that ME Keep giving cpu Send some peci Command to get the data it needs , It caches these data inside itself ,bmc Access data to it ,me The cached data will be directly returned to bmc On , as follows raw 6 1 Yes. ME Version number of .

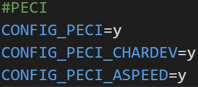

2.PECI Pattern :obmc There's one on peci-util command , Through this command, you can directly access cpu Inside ,peci-util Although it is a binary command , But the underlying call libpeci library (https://github.com/openbmc/libpeci.git), adopt libpeci visit /dev/peci-0 Nodes carry out IO Operation means that the data line sends peci Instructions .Openbmc Can make PECI Need to modify at the same time kernel.cfg and image.bb file : stay image.bb IMAGE_INSTALL Append to variable ”peci-util-v2” To install peci-util command , stay kernel.cfg add CONFIG_PECI Related macros to enable PECI drive , Here's the picture :

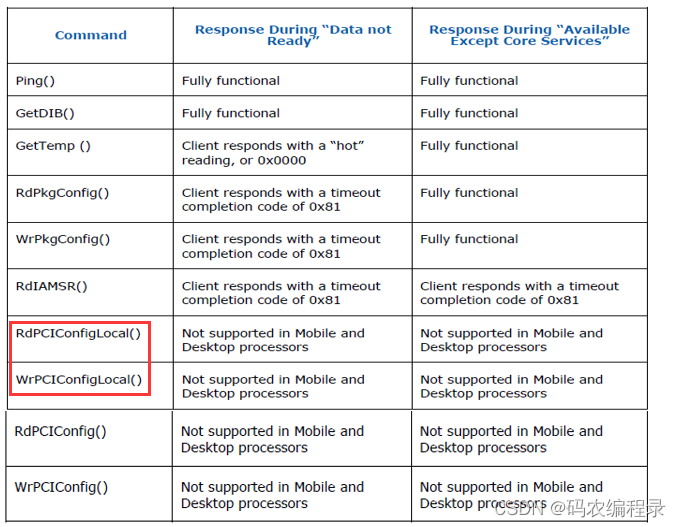

as follows peci3.0 The way to support , as follows 10 Not all commands cpu All platforms support , It depends on cpu manual , because cpu The platform functions are divided in detail , Not all platforms support all functions , front 5 Full platform support .

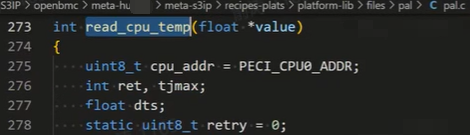

2. adopt peci read cpu temperature

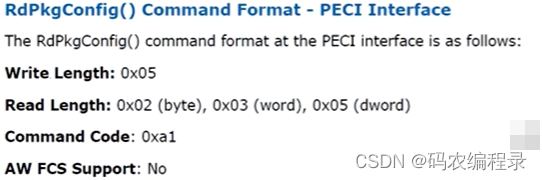

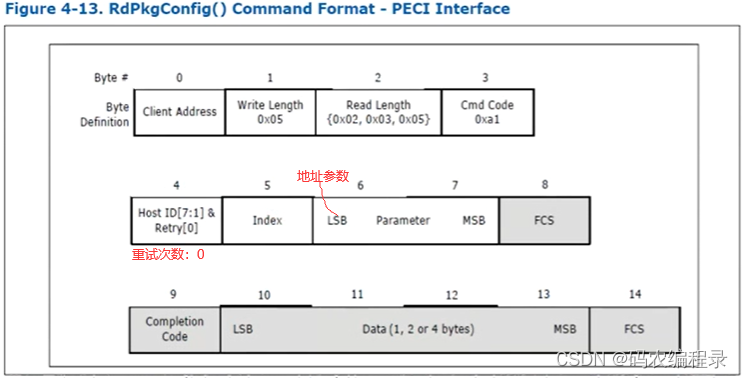

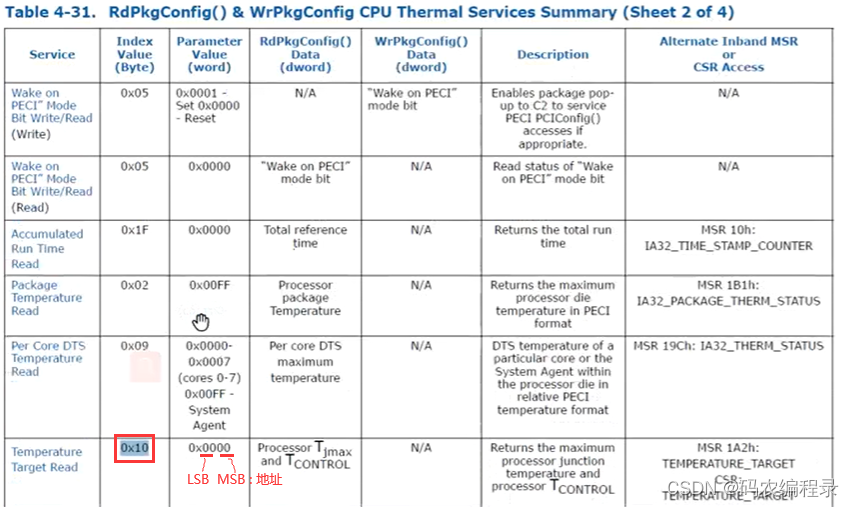

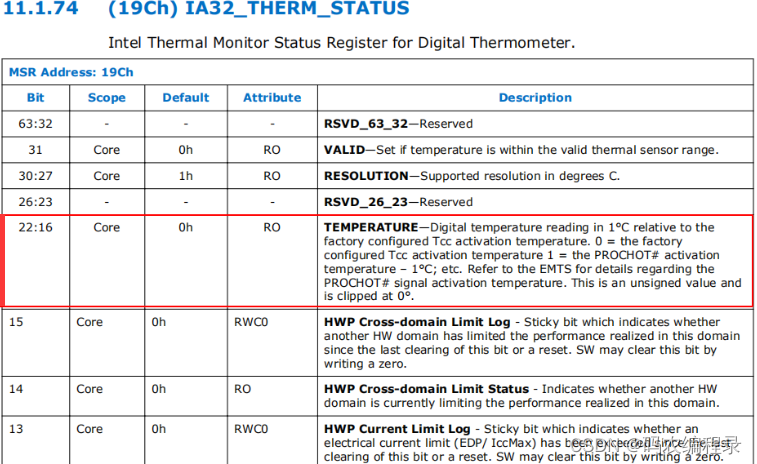

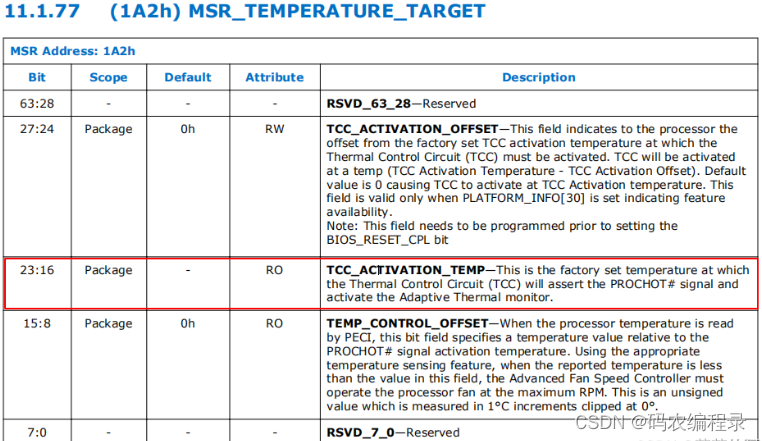

cpu Temperature use RdPkgconfig() command (read page config), adopt peci Read cpu The maximum of (tjmax) And an offset (Tcontrol)( How much is the difference from the currently set maximum value ), The difference between these two is taken as cpu The actual temperature . Here is intel In the chip manual :

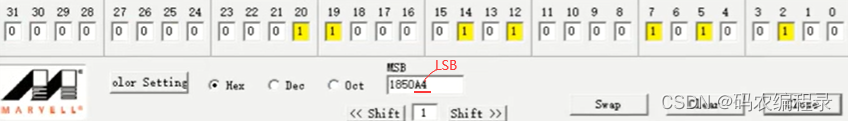

as follows 6,7 It's two bytes .

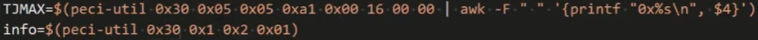

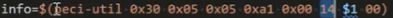

0x10( Hexadecimal ) = 16( Decimal system ).info It's the offset . as follows 0x30 yes cpu Of id, first cpu Namely 0x30,cpu2 Word is 0x31, first 05 Write the length ,oxa1 It means now read config operation ( fixed ).

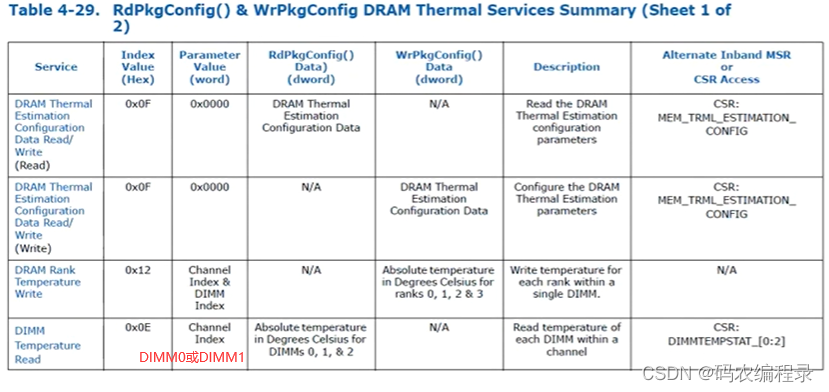

3. adopt peci read DIMM temperature

DIMM The temperature does not involve the deviation , Read the real-time temperature directly , Also use RdPkgconfig() command .DIMM Every channel You can insert two DIMM namely DIMM0 and DIMM1.14 Corresponding 0x0E,$1 Corresponding to the incoming 0 perhaps 1, Next is hexadecimal conversion .

4. adopt peci read MSR

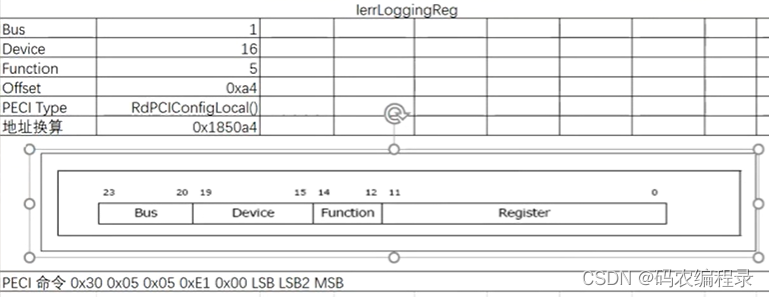

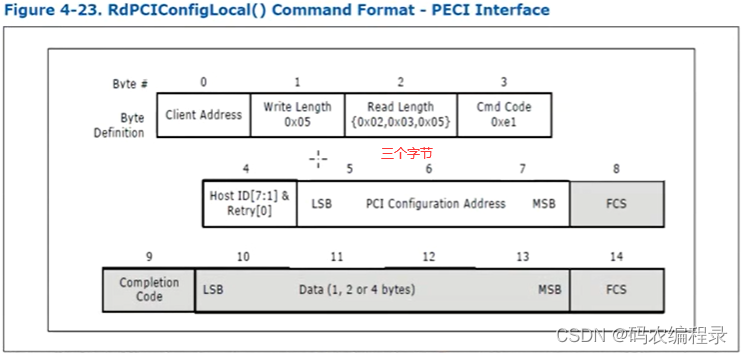

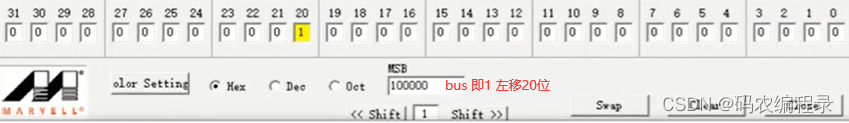

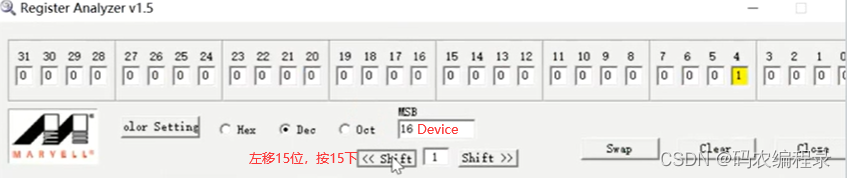

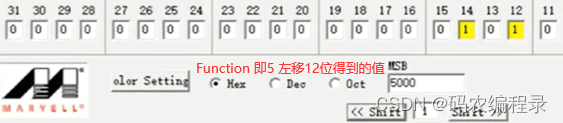

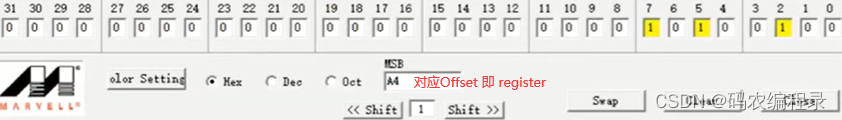

The customer gave more than msr, also pcie Some ways of reading registers ,lerrLoggingReg Through investigation cpu manual , Found to be pcie register ,BDFO Four variables can determine an address , Out of band mode RdPCIConfigLocal() read PCIE register . The following address conversion value is the three byte address ( according to BDF get ).

The following is reading cpu On pcie Registers can be read out of band , The last words need to be read lerrLoggingReg and MCerrLoggingReg All registers are read in the same way .

The above four values or ( Yes 1 by 1) Get three byte values at once .

PTSTS(Power And Reset) yes cpu Internal register , Can't read out of band . as follows C Language can also be sent PECI command , Parameters are passed in by array .

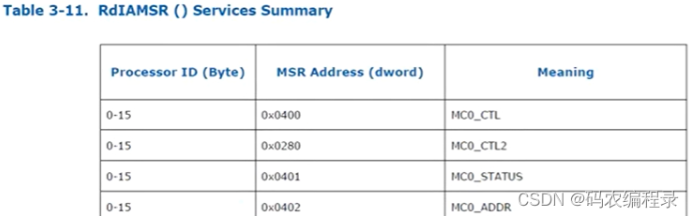

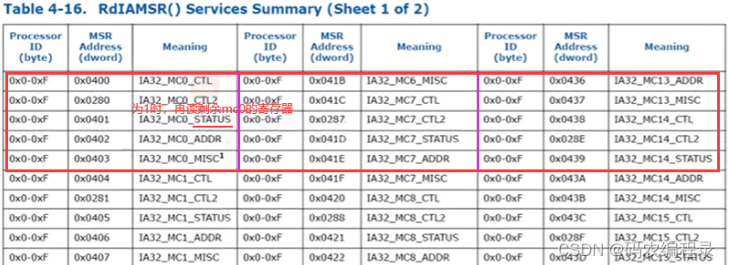

MSR(Model Specific Register) yes x86 Concepts in Architecture , Refer to x86 Architecture processor , A series of for controlling CPU function 、 Function switch 、 debugging 、 Trace program execution 、 monitoring CPU Performance and other aspects of the register .MSR Use RdIAMSR() command .

Here are all msr register ,0-15 A physical nucleus , The project is 0-4 A physical core is equivalent to 5 individual cpu, The core of logic is 0-7, Now the project reads only the physical core . We are generally only responsible for reading the register value , Specific analysis bios do , We give him the data , They check it out by themselves .

# dumplwt.sh

. /usr/local/bin/openbmc-utils.sh

renice -20 -p $$ >/dev/null 2>&1

do_msr_deal()

{

echo

echo CPU MSR DUMP:

echo ==============

echo

echo "MCA_ERR_SRC_LOG"

peci-util 0x30 0x05 0x05 0xA1 0x00 0x00 0x05 0x00

echo

echo "IerrLoggingReg"

peci-util 0x30 0x05 0x05 0xE1 0x00 0xA4 0x50 0x18

echo

echo "MCerrLoggingReg"

peci-util 0x30 0x05 0x05 0xE1 0x00 0xA8 0x50 0x18

echo

echo "********************************************************"

echo "* MC index 00 *"

echo "********************************************************"

echo " IA32_MC0_CTL, ProcessorID from 0 to 4 "

peci-util 0x30 0x05 0x09 0xB1 0x00 0x00 0x00 0x04 # The penultimate is ProcessorID

peci-util 0x30 0x05 0x09 0xB1 0x00 0x01 0x00 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x02 0x00 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x03 0x00 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x04 0x00 0x04

echo " IA32_MC0_CTL2, ProcessorID from 0 to 4 "

peci-util 0x30 0x05 0x09 0xB1 0x00 0x00 0x80 0x02

peci-util 0x30 0x05 0x09 0xB1 0x00 0x01 0x80 0x02

peci-util 0x30 0x05 0x09 0xB1 0x00 0x02 0x80 0x02

peci-util 0x30 0x05 0x09 0xB1 0x00 0x03 0x80 0x02

peci-util 0x30 0x05 0x09 0xB1 0x00 0x04 0x80 0x02

echo " IA32_MC0_STATUS, ProcessorID from 0 to 4 "

peci-util 0x30 0x05 0x09 0xB1 0x00 0x00 0x01 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x01 0x01 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x02 0x01 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x03 0x01 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x04 0x01 0x04

echo " IA32_MC0_ADDR, ProcessorID from 0 to 4 "

peci-util 0x30 0x05 0x09 0xB1 0x00 0x00 0x02 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x01 0x02 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x02 0x02 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x03 0x02 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x04 0x02 0x04

echo " IA32_MC0_MISC, ProcessorID from 0 to 4 "

peci-util 0x30 0x05 0x09 0xB1 0x00 0x00 0x03 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x01 0x03 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x02 0x03 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x03 0x03 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x04 0x03 0x04

echo "********************************************************"

echo "* MC index 01 *"

echo "********************************************************"

echo " IA32_MC1_CTL, ProcessorID from 0 to 4 "

peci-util 0x30 0x05 0x09 0xB1 0x00 0x00 0x04 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x01 0x04 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x02 0x04 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x03 0x04 0x04

peci-util 0x30 0x05 0x09 0xB1 0x00 0x04 0x04 0x04

echo " IA32_MC1_CTL2, ProcessorID from 0 to 4 "

peci-util 0x30 0x05 0x09 0xB1 0x00 0x00 0x81 0x02

peci-util 0x30 0x05 0x09 0xB1 0x00 0x01 0x81 0x02

peci-util 0x30 0x05 0x09 0xB1 0x00 0x02 0x81 0x02

peci-util 0x30 0x05 0x09 0xB1 0x00 0x03 0x81 0x02

peci-util 0x30 0x05 0x09 0xB1 0x00 0x04 0x81 0x02

do_peci_select 7 #peci The channel is manually selected in advance , stay openbmc-utils.sh in source Some borad.sh Some common script interfaces

do_msr_deal

do_peci_select 8

do_msr_deal

# as follows 0x400 yes MC0,0x404 yes MC1....

IA32_MCi_CTL=(0x400 0x404 0x408 0x40c 0x410 0x414 0x418 0x41c 0x420 0x424 0x428)

mce_log(){

modprobe msr

mcelog --daemon # Manual start mcelog. see mcelog journal :vim /var/log/mcelog

i=${

#IA32_MCi_CTL[@]}

echo "read IA32_MCi_CTL register begin ${IA32_MCi_CTL[*]}"

for ((cpu=0;cpu<8;cpu++));do

echo "cpu $cpu read IA32_MCi_CTL register"

for ((row=0;row<i;row++));do

rdmsr -p $cpu ${IA32_MCi_CTL[row]} -x

done

done

echo "read IA32_MCi_CTL register end"

}

mce_log

5.rdmsr read CPU temperature

Original scheme from /sys/class/hwmon/ The read CPU temperature , There are hwmon0、hwmon1、hwmon2 Three files , among hwmon2 There are records in the directory CPU Temperature file temp_input, You can read directly from this file CPU temperature . After the discovery temp_input Documents are sometimes in hwmon1 Next , Sometimes in hwmon2 Next , Different environments and locations . I don't want to use the method of directly reading files to obtain temperature , see CPU The manual found the way to read the register to obtain the temperature , The scheme is relatively stable .

rdmsr programme :intel cpu The following two registers are available for reading CPU temperature .CPU temperature = TCC_ACTIVATION_TEMP - TEMPERATURE.0x1A2: The register of bit23-16 Recorded TCC_ACTIVATION_TEMP value , The modified value can be understood as CPU Threshold for triggering the temperature regulation means , This threshold is set at the factory ;0x19C: The register of bit22-16 Recorded TEMPERATURE value , This value is CPU The temperature is relative to TCC_ACTIVATION_TEMP The temperature value of ;

#define TEMP_TARGET_MSR_REG (0x1a2)

#define TEMP_STATUS_MSR_REG (0x19c)

static int get_cpu_msr_temp_info(void) // Interface directly returns CPU The actual temperature

{

int ucTempOffset;

int ucTempActivation;

int dwValh=0,dwVall=0;

rdmsr(TEMP_TARGET_MSR_REG, dwVall, dwValh);

/*bit23-16*/

dwVall &= 0x00FF0000;

ucTempActivation = (dwVall>>16)&0xff;

dwVall=0;

dwValh=0;

rdmsr(TEMP_STATUS_MSR_REG, dwVall, dwValh);

/*bit22-16*/

dwVall &= 0x007F0000;

ucTempOffset = (dwVall>>16)&0xff;

return (ucTempActivation-ucTempOffset);

}

边栏推荐

- Evolution of APK reinforcement technology, APK reinforcement technology and shortcomings

- The difference between MVVM and MVC

- [speech processing] speech signal denoising based on Matlab GUI Hanning window fir notch filter [including Matlab source code 1711]

- Overview of Fourier analysis

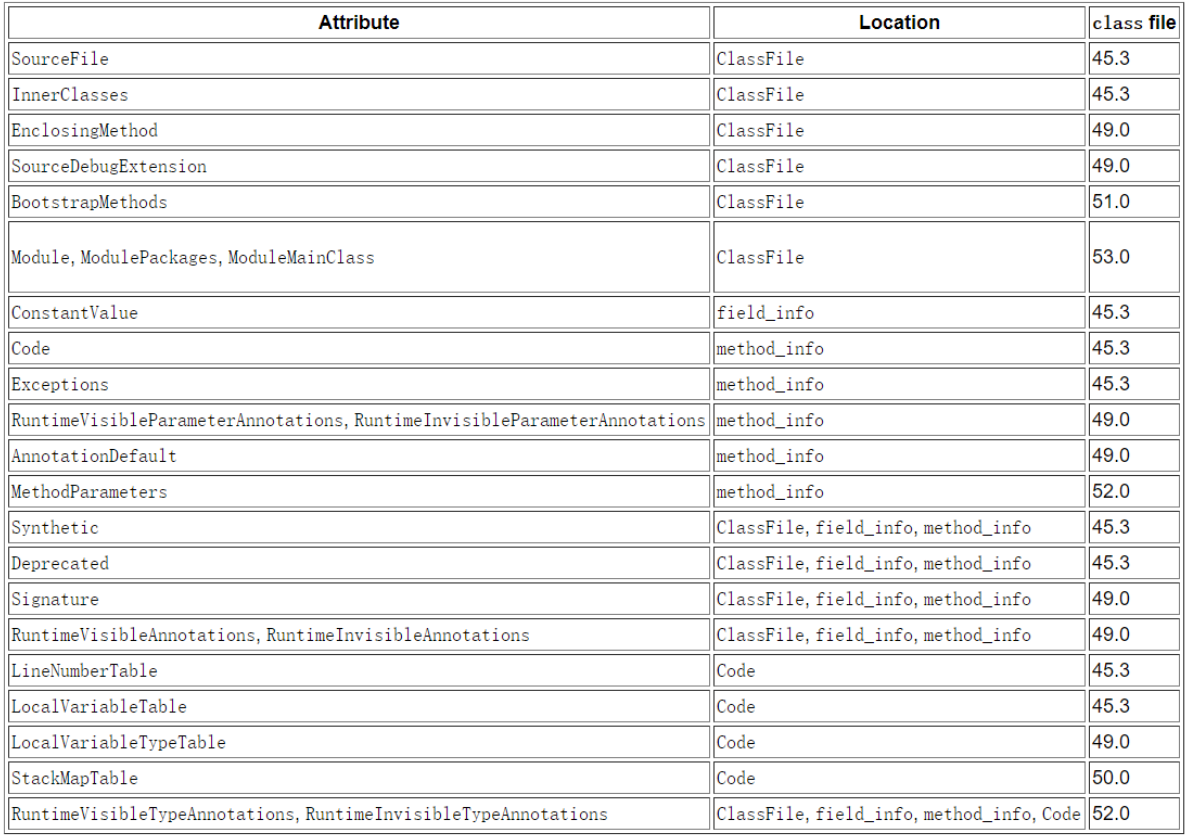

- Un article traite de la microstructure et des instructions de la classe

- Metasploit(msf)利用ms17_010(永恒之蓝)出现Encoding::UndefinedConversionError问题

- Distributed resource management and task scheduling framework yarn

- I closed the open source project alinesno cloud service

- VIM tail head intercept file import

- Exponential weighted average and its deviation elimination

猜你喜欢

![[speech processing] speech signal denoising based on Matlab GUI Hanning window fir notch filter [including Matlab source code 1711]](/img/03/8fa104b177698a15b7ffa70d4fb524.jpg)

[speech processing] speech signal denoising based on Matlab GUI Hanning window fir notch filter [including Matlab source code 1711]

一文搞定class的微观结构和指令

![Sparse array [matrix]](/img/62/27b02deeeaa5028a16219ef51ccf82.jpg)

Sparse array [matrix]

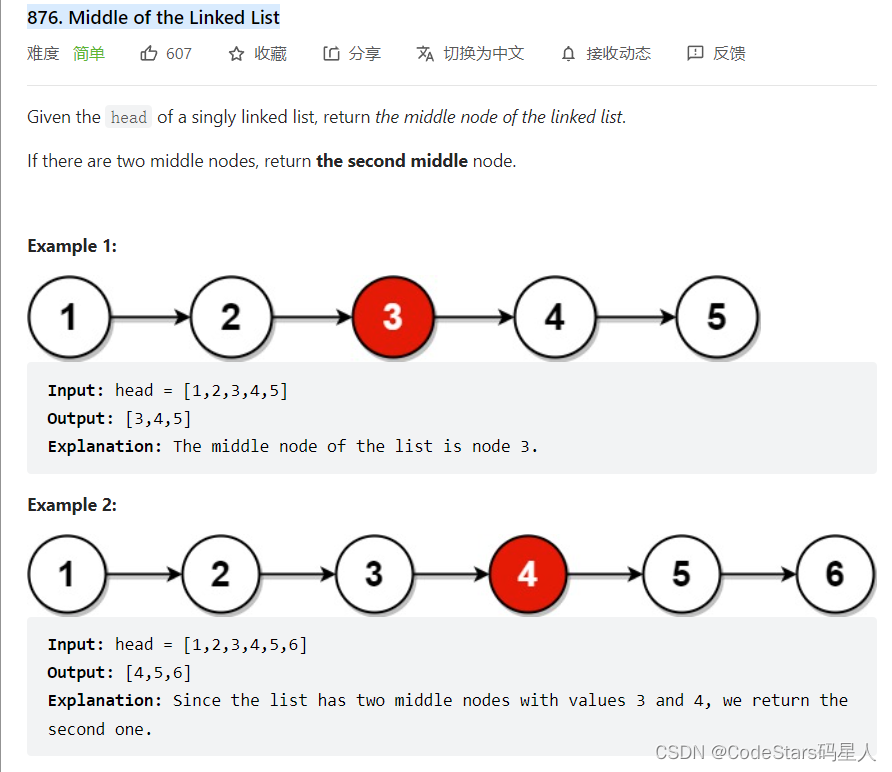

鏈錶之雙指針(快慢指針,先後指針,首尾指針)

一文搞定JVM常见工具和优化策略

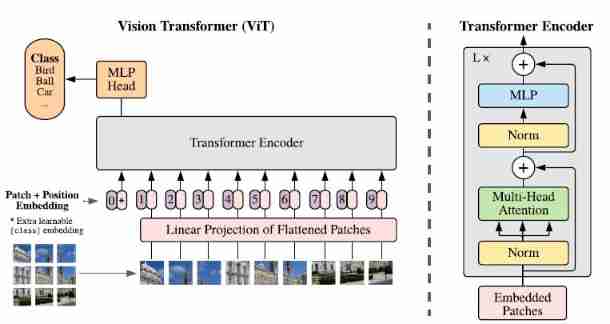

Vision Transformer (ViT)

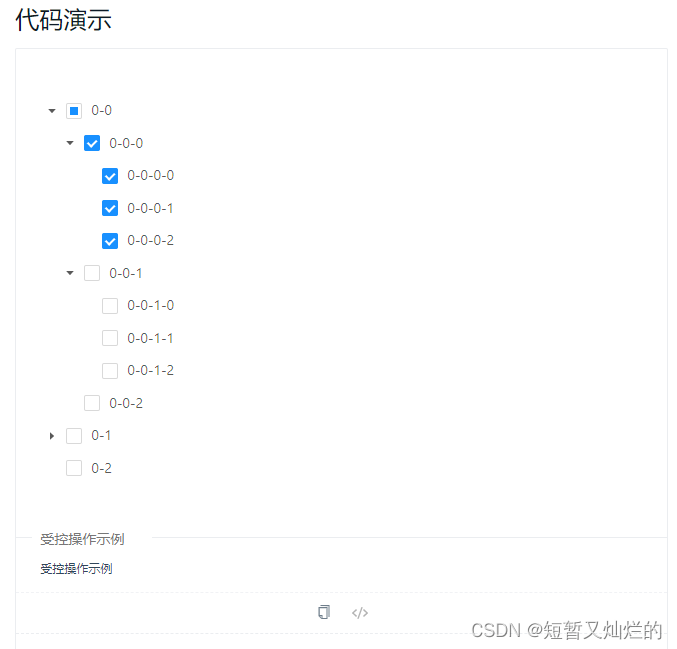

All expansion and collapse of a-tree

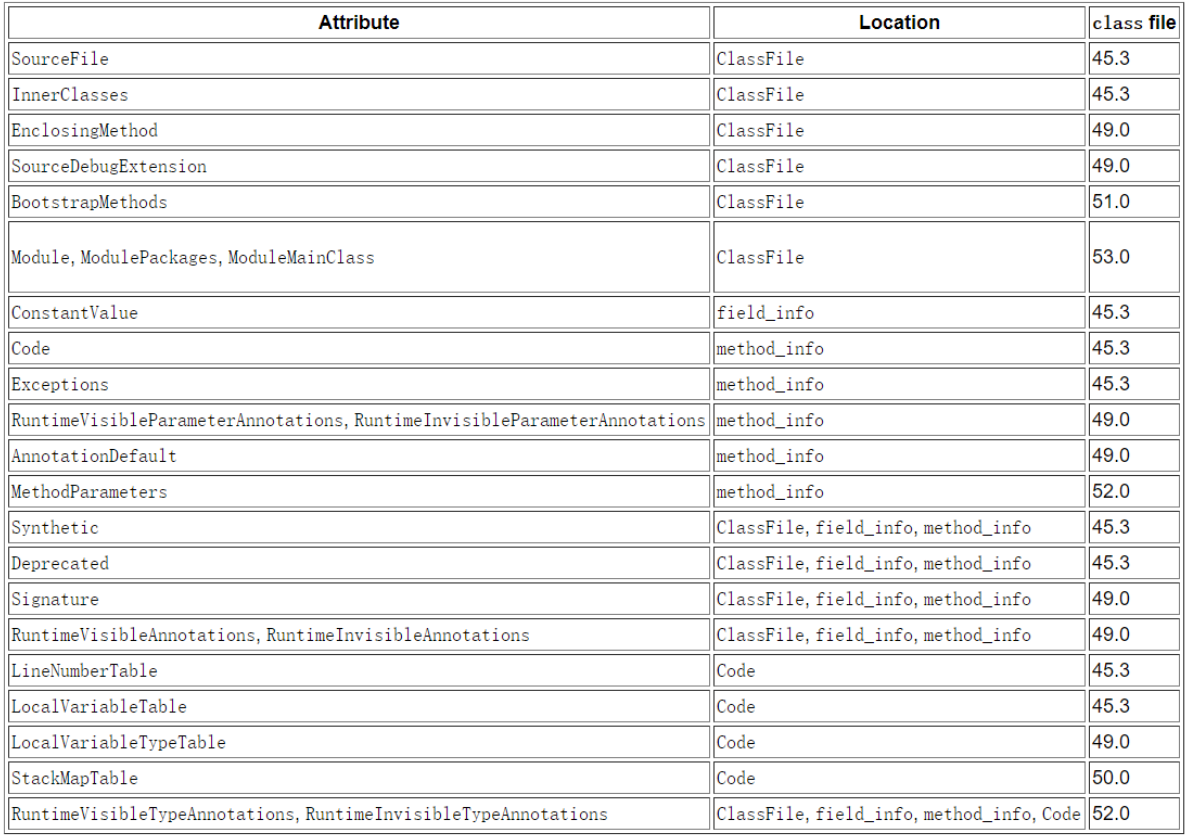

One article deals with the microstructure and instructions of class

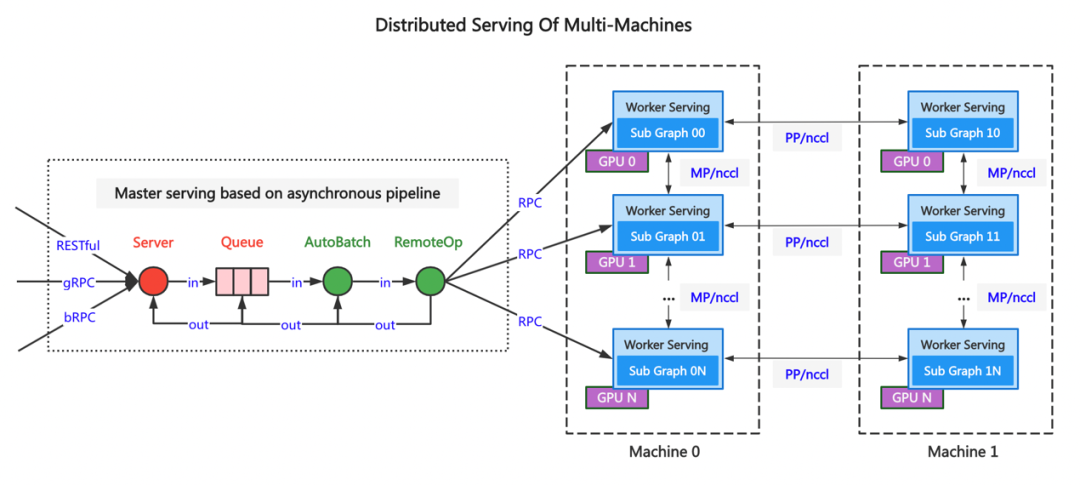

Paddy serving v0.9.0 heavy release multi machine multi card distributed reasoning framework

Postman核心功能解析-参数化和测试报告

随机推荐

Function default parameters, function placeholder parameters, function overloading and precautions

Distributed resource management and task scheduling framework yarn

[groovy] mop meta object protocol and meta programming (execute groovy methods through metamethod invoke)

First, redis summarizes the installation types

航海日答题小程序之航海知识竞赛初赛

抖音__ac_signature

Request preview display of binary data and Base64 format data

Opencv judgment points are inside and outside the polygon

终于搞懂什么是动态规划的

Character conversion PTA

30 optimization skills about mysql, super practical

基于STM32的ADC采样序列频谱分析

Editor extensions in unity

Paddy serving v0.9.0 heavy release multi machine multi card distributed reasoning framework

Metaverse Ape上线倒计时,推荐活动火爆进行

FBO and RBO disappeared in webgpu

New 3D particle function in QT 6.3

TCC of distributed solutions

解决thinkphp启动时“No input file specified”的问题

第一讲:蛇形矩阵