当前位置:网站首页>(4) UART application design and simulation verification 2 - TX module design (stateless machine)

(4) UART application design and simulation verification 2 - TX module design (stateless machine)

2022-07-05 23:10:00 【Shaoqing is not in Dali Temple】

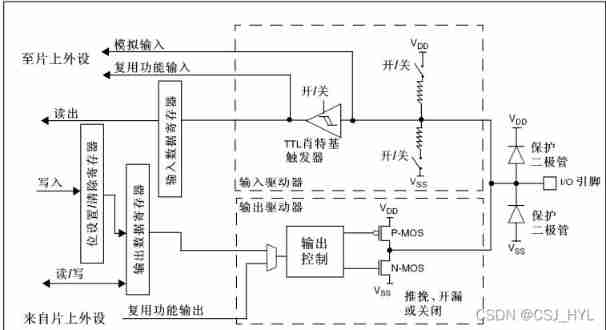

Preface : Looking back on this small project again, it has been a few months , In the follow-up study , The new teacher is constantly emphasizing , Try to use less state machines in practical work , When sorting out the article, I forgot what he said at that time . So I try to rewrite it myself UART, Organize a version without a state machine .

Here are a few basic logical points to review again :

1) The complete one frame data format contains : Start bit , Valid data bits , Check bit , Stop bit ;

2) Calculation sheet bit Data transmission time : utilize baoud( Baud rate ) and clk( The system clock ), Baud rate unit bit per second, The clock Hz Company time per second , So the clock divided by the baud rate is time per bit, That is, every bit Corresponding to how many clock cycles ;

3) Reference signal : Transmission signal baoud_cnt_half, Every time bit Half way through the count , To transfer data ; Switch the counting signal baoud_cnt_end, Every time bit When the count is finished , Enter the next counting cycle ; Bit count bit_cnt, Calculate the number of bits transferred in a frame of data ; Transmission process flag signal start_flag, Throughout every data transmission .

Code up :

//date:2022.6.30

//edgar.yao

//uart_tx block

module uart_tx(

input clk,

input rst_n,

input[7:0] cmd_data,

input data_valid,

output tx,

output tx_read边栏推荐

猜你喜欢

Finally understand what dynamic planning is

LeetCode102. Sequence traversal of binary tree (output by layer and unified output)

【Note17】PECI(Platform Environment Control Interface)

Error when LabVIEW opens Ni instance finder

February 13, 2022-4-symmetric binary tree

Getting started stm32--gpio (running lantern) (nanny level)

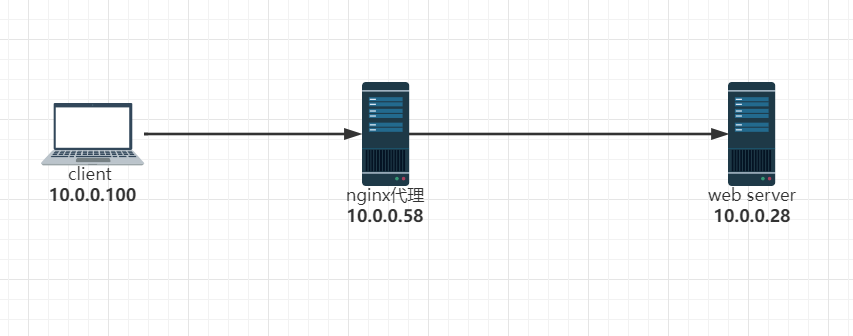

Realize reverse proxy client IP transparent transmission

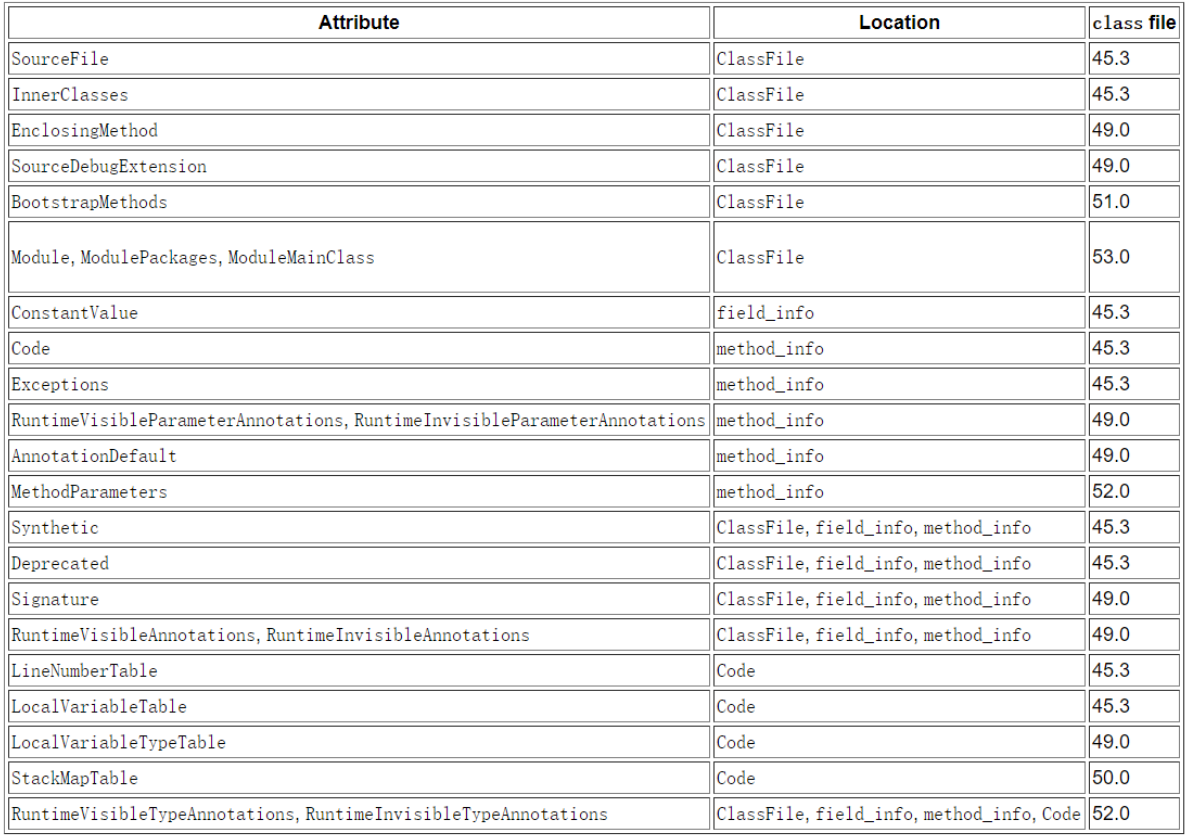

一文搞定class的微觀結構和指令

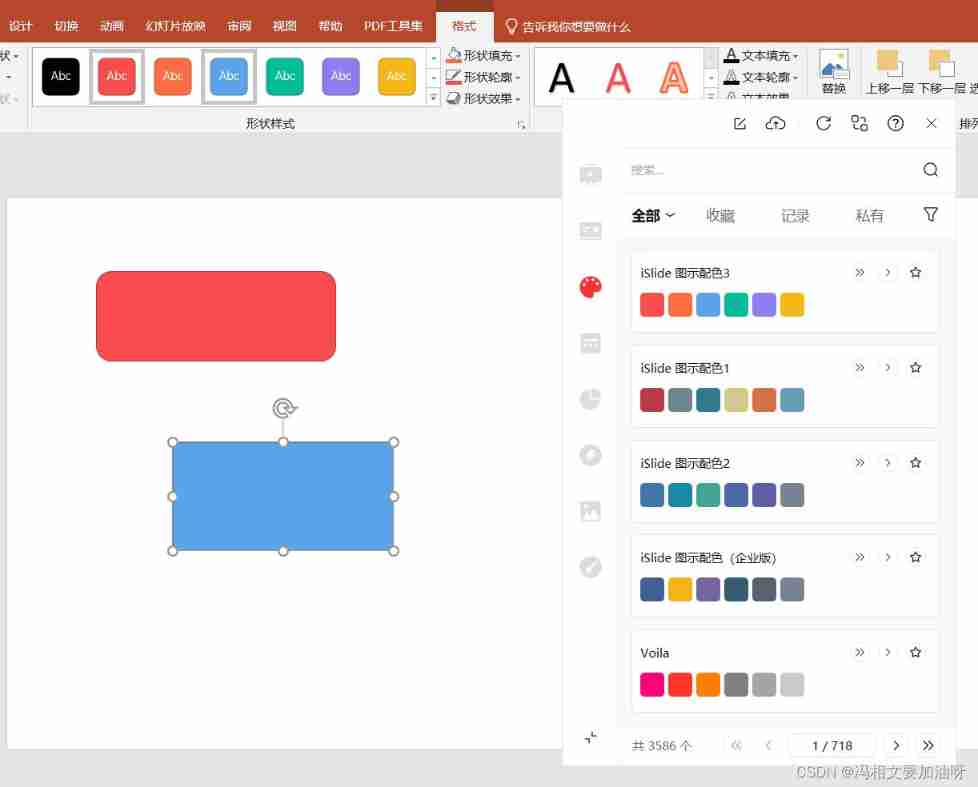

Simple and beautiful method of PPT color matching

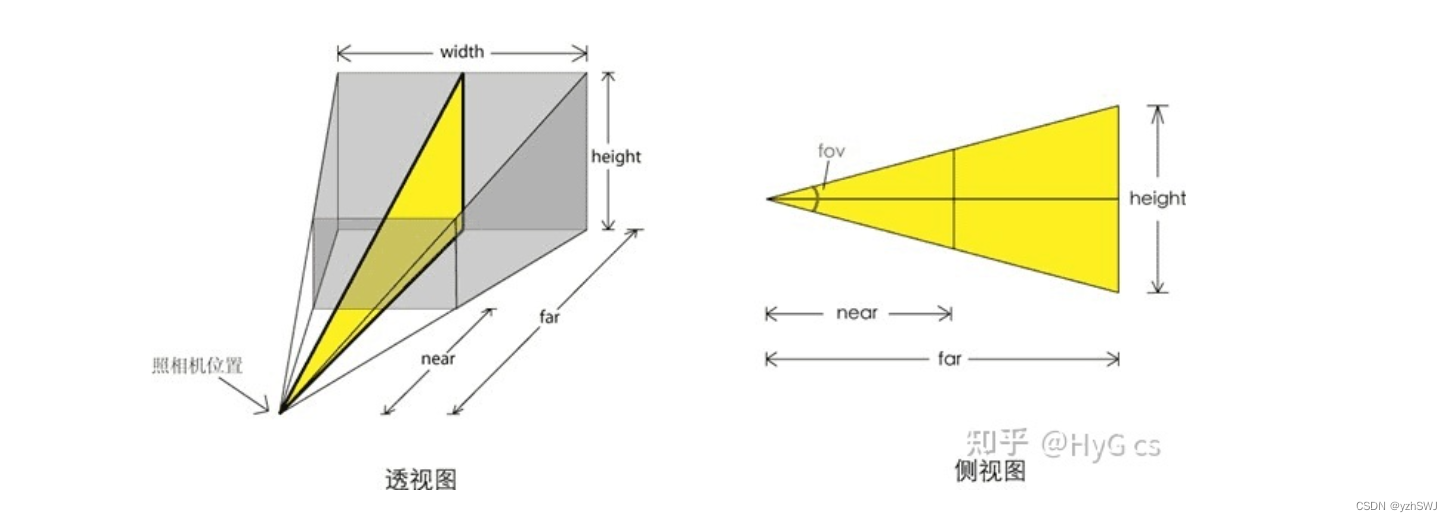

Three. Js-01 getting started

随机推荐

Openresty ngx Lua regular expression

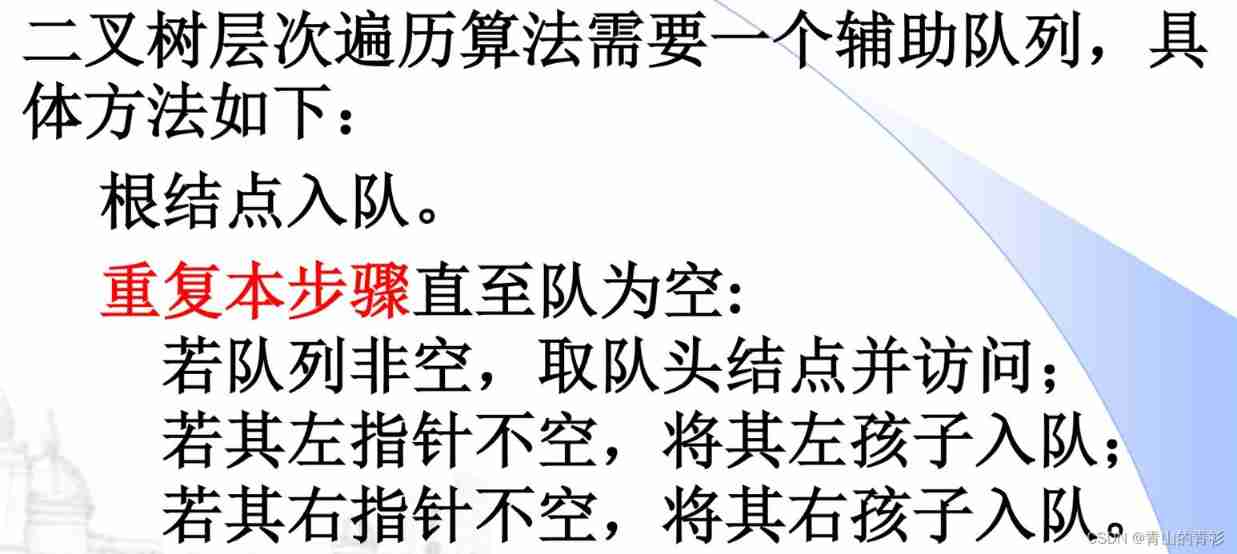

LeetCode102. Sequence traversal of binary tree (output by layer and unified output)

How to quickly understand complex businesses and systematically think about problems?

3:第一章:认识JVM规范2:JVM规范,简介;

Three.JS VR看房

Function default parameters, function placeholder parameters, function overloading and precautions

d3dx9_ What if 29.dll is missing? System missing d3dx9_ Solution of 29.dll file

3D reconstruction of point cloud

fibonacci search

14种神笔记方法,只需选择1招,让你的学习和工作效率提高100倍!

Vision Transformer (ViT)

Selenium+pytest automated test framework practice

Use the rewrite rule to rewrite all accesses to the a domain name to the B domain name

[speech processing] speech signal denoising and denoising based on Matlab GUI low-pass filter [including Matlab source code 1708]

媒体查询:引入资源

What is the process of building a website

openresty ngx_lua正則錶達式

Paddy serving v0.9.0 heavy release multi machine multi card distributed reasoning framework

First, redis summarizes the installation types

Marginal probability and conditional probability