当前位置:网站首页>VHDL implementation of arbitrary size matrix multiplication

VHDL implementation of arbitrary size matrix multiplication

2022-07-07 03:26:00 【QQ_ seven hundred and seventy-eight million one hundred and thi】

VHDL Realize matrix multiplication of any size

You can modify the size of the matrix through parameters ;

Use VHDL Language implementation ;

stay vivado Synthesis and Simulation on .

The code is as follows :

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

use work.DigEng.ALL;

entity Top_level is

------------set generic value for N,M,H,data_size--------------------

– Default values 23 matrix A and 32 matrix B to define the size of matrices

generic( M: natural := 3; – the number of columns of A and rows of B

N: natural := 5; – the number of columns of B

H: natural := 4; – the number of rows of A

data_size: natural := 5); – how many bits of binary number representing the data stored in ROM

---------------set inputs and outputs for the matrix multiplication--------

– Define ports in the circuits

Port ( CLK : in STD_LOGIC; – time sequence

RST :

边栏推荐

- Don't you know the relationship between JSP and servlet?

- Set WiFi automatic connection for raspberry pie

- Huawei and Xiaomi "copy each other"

- Open3D 网格滤波

- Cryptography series: detailed explanation of online certificate status protocol OCSP

- 体会设计细节

- 【无标题】

- Make (convert) ICO Icon

- 数学归纳与递归

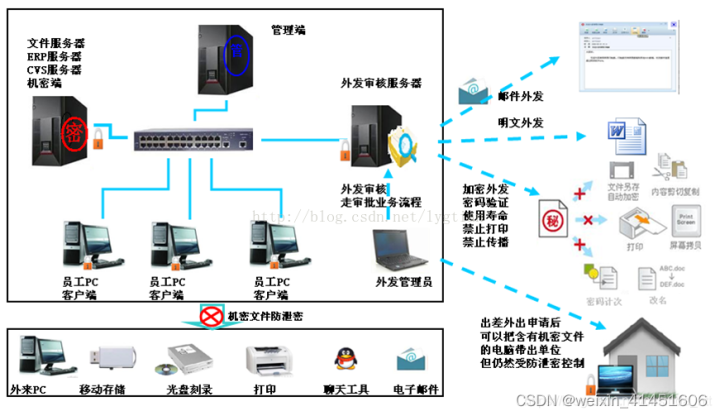

- Significance and measures of source code confidentiality

猜你喜欢

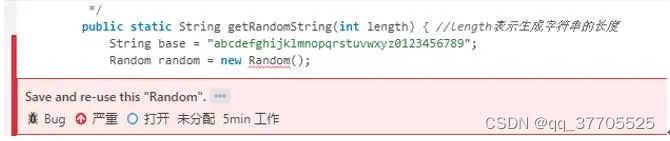

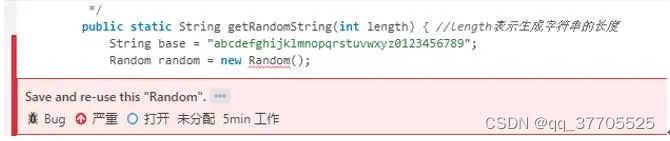

Code quality management

CVPR 2022 best paper candidate | pip: six inertial sensors realize whole body dynamic capture and force estimation

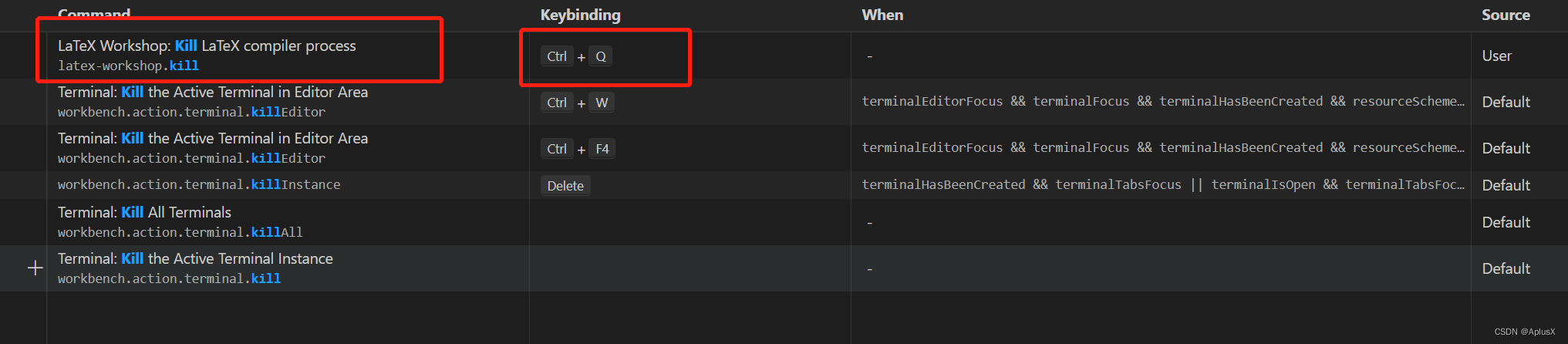

如何自定义Latex停止运行的快捷键

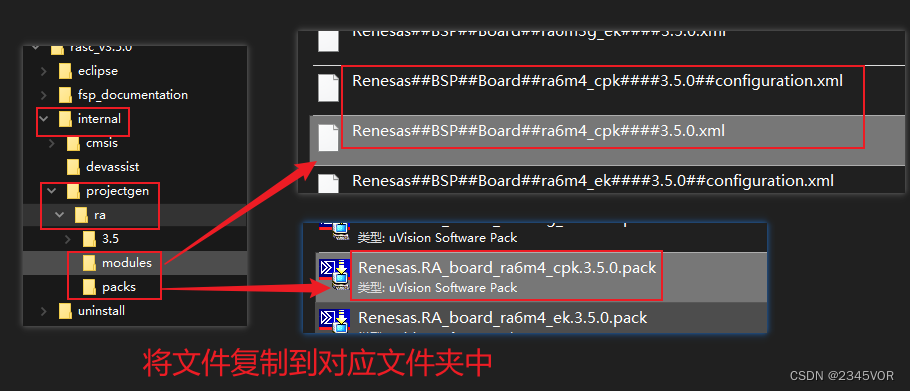

【基于 RT-Thread Studio的CPK-RA6M4 开发板环境搭建】

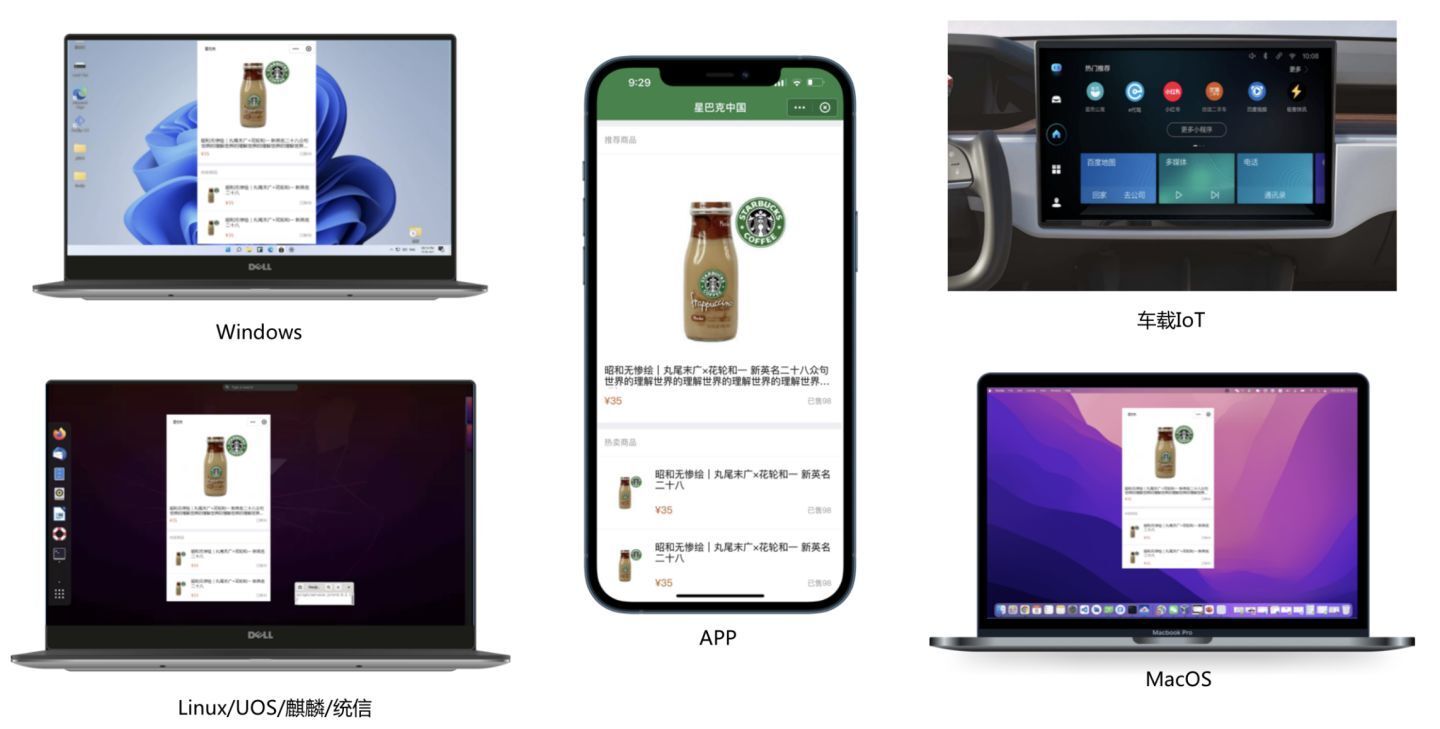

Flutter3.0了,小程序不止于移动应用跨端运行

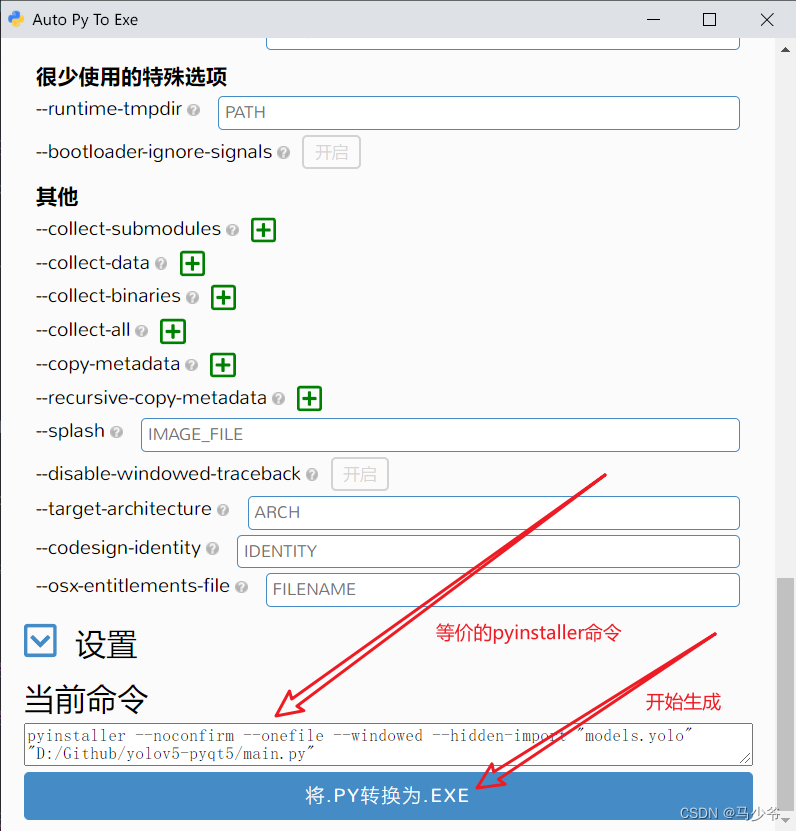

Graphical tools package yolov5 and generate executable files exe

代码质量管理

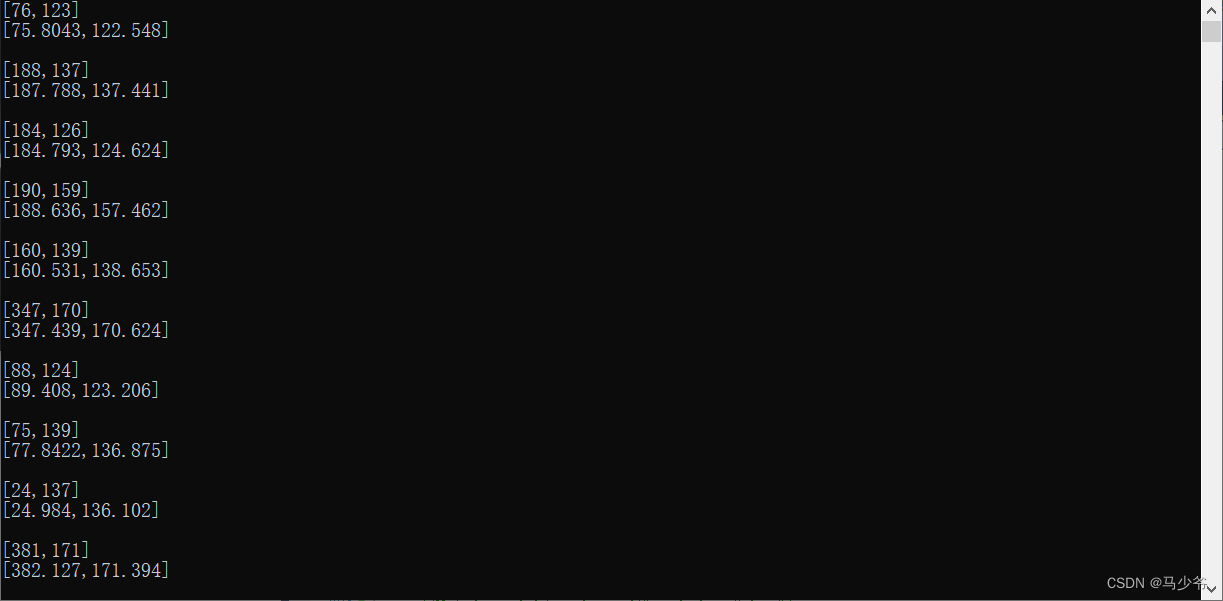

亚像素级角点检测Opencv-cornerSubPix

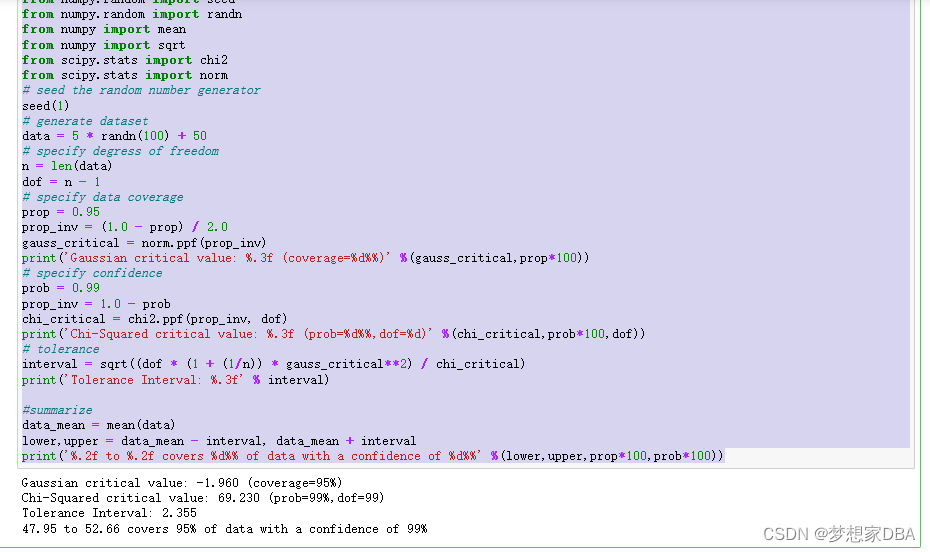

About Tolerance Intervals

源代码保密的意义和措施

随机推荐

About Tolerance Intervals

Cocos2d-x box2d physical engine compilation settings

Under the tide of "going from virtual to real", Baidu AI Cloud is born from real

How to replace the backbone of the model

Development of wireless communication technology, cv5200 long-distance WiFi module, UAV WiFi image transmission application

体会设计细节

【无标题】

pip只下载不安装

Set WiFi automatic connection for raspberry pie

哈夫曼树基本概念

[colmap] 3D reconstruction with known camera pose

Flink task exit process and failover mechanism

从0开始创建小程序

校招行测笔试-数量关系

Jericho is in non Bluetooth mode. Do not jump back to Bluetooth mode when connecting the mobile phone [chapter]

存储过程与函数(MySQL)

20.(arcgis api for js篇)arcgis api for js面采集(SketchViewModel)

编译常量、ClassLoader类、系统类加载器深度探析

源代码保密的意义和措施

1200.Minimum Absolute Difference