当前位置:网站首页>【数字IC/FPGA】检测最后一个匹配序列的位置

【数字IC/FPGA】检测最后一个匹配序列的位置

2022-06-27 20:44:00 【FPGA硅农】

题目描述

编写一个模块,输入一个64比特的比特流,识别匹配出101101的最后的位置,并输出位置信息。

代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/06/21 10:34:41

// Design Name:

// Module Name: top

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module top(

input logic clk,

input logic rst,

input logic valid,

input logic din,

output logic done,

output logic [5:0] pos

);

//101101

logic [5:0] shift_reg;

logic [5:0] cnt;

//cnt

[email protected](posedge clk,posedge rst)

if(rst)

cnt<=0;

else if(valid)

begin

if(cnt==64-1)

cnt<=0;

else

cnt<=cnt+1;

end

//shift_reg

[email protected](posedge clk,posedge rst)

if(rst)

shift_reg<=0;

else if(valid)

shift_reg<={

shift_reg[4:0],din}; //高位先输入

//pos

[email protected](posedge clk,posedge rst)

if(rst)

begin

pos<=64;

end

else if(shift_reg==6'b101101)

begin

pos<=cnt-6;

end

//done

[email protected](posedge clk,posedge rst)

if(rst)

done<=0;

else

done<=(cnt==64-1&&valid)?1:0;

endmodule

测试平台

module test;

logic clk;

logic rst;

logic valid;

logic din;

logic done;

logic [5:0] cnt;

logic [5:0] pos;

logic [63:0] data;

//

initial

begin

//data={12'b101101101101,52'd0};

data={

20'd0,12'b101101101101,32'd0};

end

//clk

initial

begin

clk=0;

forever

#5 clk=~clk;

end

//rst

initial

begin

rst=1;

#100

rst=0;

end

//valid,din

initial

begin

valid<=0;

cnt<=0;

wait(rst==1'b0);

@(posedge clk);

repeat(64)

begin

valid<=1;

din<=data[63-cnt];

cnt<=cnt+1;

@(posedge clk);

end

valid<=0;

end

top U(.*);

/* input logic clk, input logic rst, input logic valid, input logic din, output logic done, output logic [5:0] pos ); */

endmodule

结果

输入比特流为data={20’d0,12’b101101101101,32’d0},因此,最后匹配的序列的位置应该是20+6=26,符合预期。

边栏推荐

- 新加坡国立大学|采用无模型强化学习方法评估能源效益数据中心的节能情况

- pytorch基础(1)

- Consumer finance app user insight in the first quarter of 2022 - a total of 44.79 million people

- 在线JSON转PlainText工具

- Summary of various loams (laser SLAM)

- The choice and trade-off between vector recall and literal recall

- PE买下一家内衣公司

- 云辅助隐私集合求交(Server-Aided PSI)协议介绍:学习

- 个人TREE ALV 模版-加快你的开发

- 医美大刀,砍向00后

猜你喜欢

资深猎头团队管理者:面试3000顾问,总结组织出8大共性(茅生)

【蓝桥杯集训100题】scratch数字计算 蓝桥杯scratch比赛专项预测编程题 集训模拟练习题第16题

本机部署一个MongoDB单节点服务器,并启用auth验证、开启oplog

量化交易入门教程

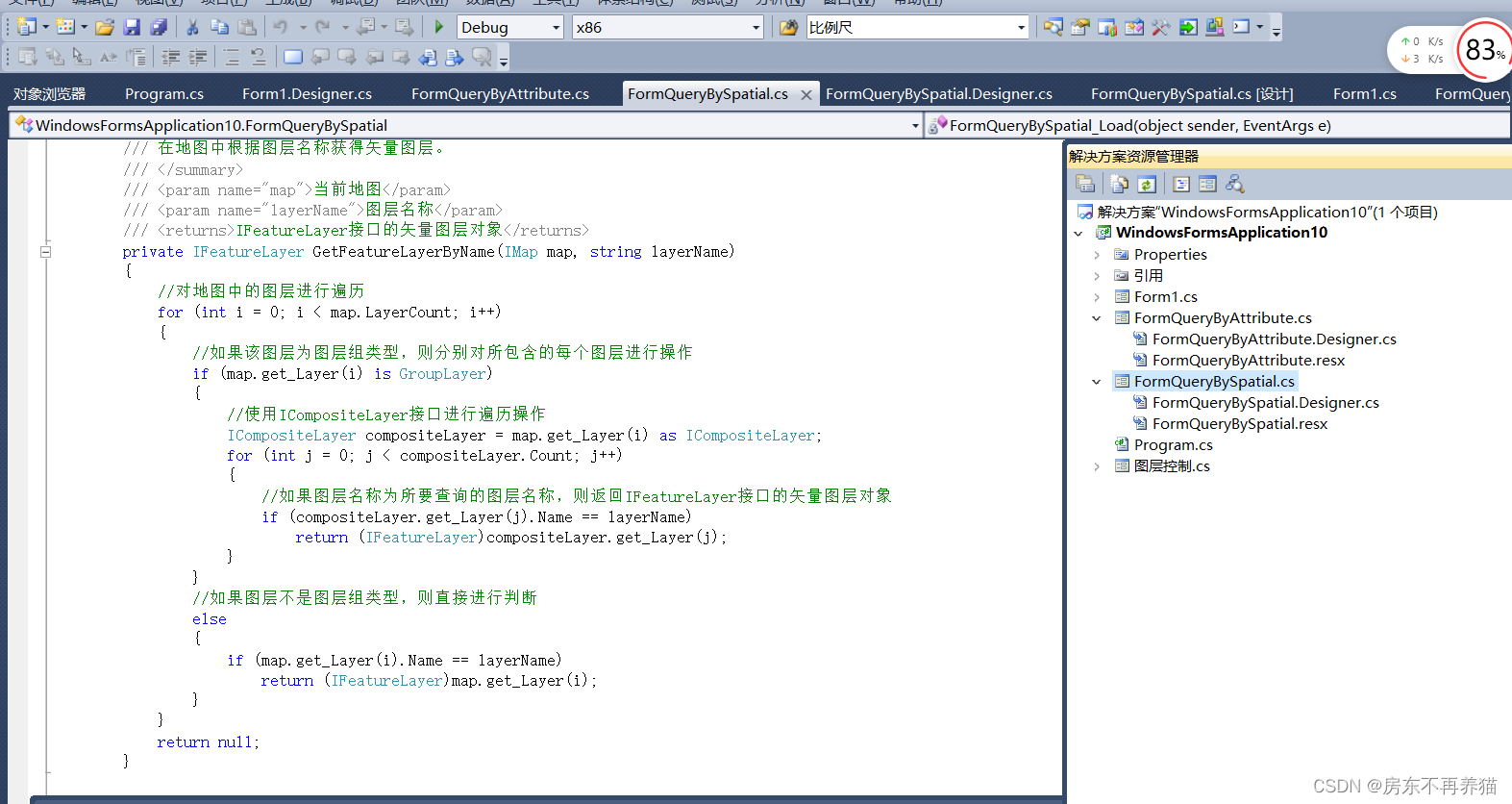

Spatial relation query and graph based query in secondary development of ArcGIS Engine

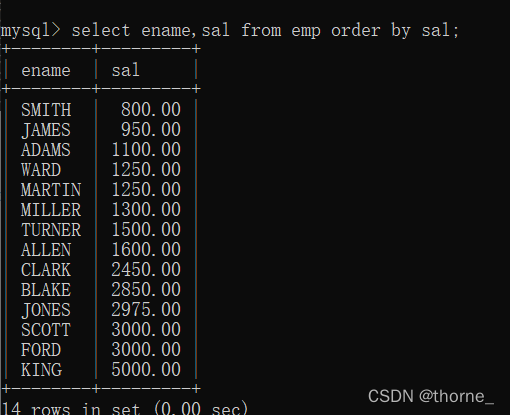

Introduction to MySQL operation (IV) -- data sorting (ascending, descending, and multi field sorting)

Senior headhunting team manager: interviewed 3000 consultants, summarized and organized 8 commonalities (Mao Sheng)

Vue+mysql login registration case

2022年第一季度“广州好人”刘磊峰:具有强烈的诚信意识和食品安全意识

Redis principle - string

随机推荐

99 multiplication table - C language

Re recognize G1 garbage collector through G1 GC log

雪糕还是雪“高”?

Typora 1.2.5等版本下载

PHP连接数据库实现用户注册登录功能

PHP connects to database to realize user registration and login function

PE买下一家内衣公司

PE buys a underwear company

跨系统数据一致性问题解决方案汇总

[microservices] (16) -- distributed transaction Seata

Spark bug practice (including bug:classcastexception; connectexception; NoClassDefFoundError; runtimeException, etc.)

如何设置企业微信群机器人定时发消息?

跟着存档教程动手学RNAseq分析(四):使用DESeq2进行DE分析的QC方法

pytorch 入门指南

Senior headhunting team manager: interviewed 3000 consultants, summarized and organized 8 commonalities (Mao Sheng)

【IDEA】IDEA 格式化 代码技巧 idea 格式化 会加 <p> 标签

移动端避免使用100vh[通俗易懂]

[js]var, let,const 的区别

Bibliothèque d'exploitation / de développement locale open source pour l'outil de dessin en ligne hiplot

批量处理-Excel导入模板1.1-支持多Sheet页