当前位置:网站首页>2022 Huashu Cup Mathematical Modeling Question A Optimization Design Ideas for Ring Oscillators Code Sharing

2022 Huashu Cup Mathematical Modeling Question A Optimization Design Ideas for Ring Oscillators Code Sharing

2022-08-05 10:02:00 【Xiaolei Mathematical Modeling_】

参考链接

https://jq.qq.com/?_wv=1027&k=3a2eSE4C

https://jq.qq.com/?_wv=1027&k=3a2eSE4C

https://jq.qq.com/?_wv=1027&k=3a2eSE4C

https://jq.qq.com/?_wv=1027&k=3a2eSE4C

A 题 Optimized Design of Ring Oscillators

A chip is a silicon chip that contains an integrated circuit,Mobile phones in our daily life、电脑、电视、家 It is used in electrical appliances and other fields,It is the core cornerstone of high-end manufacturing.The manufacturing process of chips is very complex, It has to go through thousands of processes and be processed and manufactured by complex processes.Especially digital chips,With process size no Broken down,The optimal design of digital chips becomes particularly important.

The ring oscillator is an important structure in the digital clock chip,There are three important things in its design Metrics need to be considered:速度、面积和功耗.Speed refers to the clock frequency at which a circuit operates,一般来说, 速度越快,The more data that can be processed,性能越好.Area refers to the physical implementation of the circuit needs to occupy Use the area of the silicon wafer,The smaller the area occupied,The lower the chip cost.Power consumption refers to the energy consumed by the operation of the circuit 量,功耗越低,The calorific value is also lower,Equipment works longer,longer life.速度、面 积、Power consumption is tied to each other,in the same manufacturing process (制程) and under the same circuit conditions,一 般来说,速度越快,The smaller the transistor size,功耗也越高,反之亦然.相关概念与参数 See appendix for introduction 1.

Please read the relevant documentation,回答下列问题.

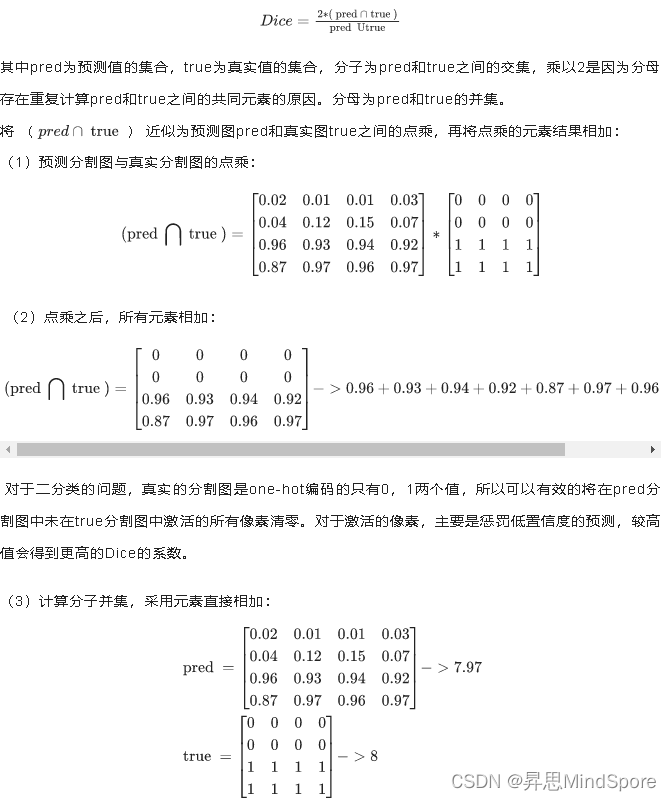

\1. The frequency formula for a ring oscillator is f = 1/ (2n t****pd ) ,其中nis the number of inverters,t****pd 为 Delay time of a single-stage inverter.The load capacitance of an inverter is proportional to the gate area of the next stage inverter, 为 2nF/ μm2 .The current formula when the inverter works can be divided into the following two stages:saturation region and linearity 区.The formula for the two stages is :

t****pd ) ,其中nis the number of inverters,t****pd 为 Delay time of a single-stage inverter.The load capacitance of an inverter is proportional to the gate area of the next stage inverter, 为 2nF/ μm2 .The current formula when the inverter works can be divided into the following two stages:saturation region and linearity 区.The formula for the two stages is :

I****d =〈 K

K

(VKg

(VKg

VdsV****gs<

VdsV****gs< VgsV****th

VgsV****th V****th

V****th

式中,V****gsrepresents the voltage between gate and source,V****dsIndicates the voltage between drain and source,V****threpresents the threshold voltage. Please refer to the above,计算表 1 Output frequency of ring oscillators in different designs.

表 1 Ring oscillator output frequency calculation table

| 序号 | 反相器 个数 | PMOS 宽 aspect ratio | NMOS 宽 aspect ratio | 电源电压/V | 输出频率 |

|---|---|---|---|---|---|

| 1 | 11 | 400n/ 100n | 200n/ 100n | 1 2 | |

| 2 | 11 | 800n/200n | 400n/200n | 1.2 | |

| 3 | 11 | 1.6u/0.4u | 0.8u/0.4u | 1.2 |

| 4 | 31 | 200n/ 100n | 400n/ 100n | 1.2 | |

|---|---|---|---|---|---|

| 5 | 31 | 400n/200n | 800n/200n | 1.2 | |

| 6 | 31 | 0.8u/0.4u | 1.6u/0.4u | 1.2 | |

| 7 | 51 | 500n/ 100n | 500n/ 100n | 1.2 | |

| 8 | 51 | 1000n/200n | 1000n/200n | 1.2 | |

| 9 | 51 | 1.8u/0.3u | 1.8u/0.3u | 1.2 | |

| 10 | 99 | 2u/0 5u | 1u/0 5u | 1 2 |

\2. The layout of the ring oscillator is shown in the appendix 1 .the output frequency of the ring oscillatorf为 10MHz ,反相 The number of devices is 51 时, 问NMOS和PMOS的W和LWhat is the size of ,The facet required for the ring oscillator The product will be minimized.

\3. Minimizing power consumption is the primary goal of ring oscillator design.Please reset the ring oscillator

计,the output frequency of the ring oscillatorf为 5MHz时, Ask the number of inverters and transistorsW及L尺寸 为多少时,Ring oscillators require minimal power consumption?

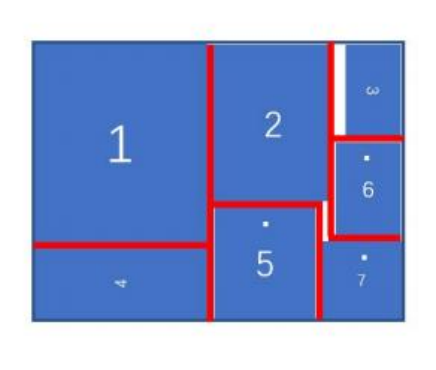

\4. When the chip is taped out, a multi-project wafer is generally selected (MPW) ,That is, multiple chips are in the same wafer Imposition on a circle,Share the cost of tape-out.The imposition rules are in a piece size 3mm*4mm的晶圆 Place all the chips on it as shown in the figure 1 所示,Dicing lanes pass between chips (红色实线) 隔离开 (Slicing Road 为 80um宽,And the number of scribing lanes should be as small as possible,Otherwise, it is easy to cause damage to other chips) . 现有 7 块芯片,其中6 The block chip area is fixed (见表2) ,The remaining chip area is to be determined.接 第 3 问,at the output frequency 2KHz时,How to size a ring oscillator,In pursuit of minimum power consumption

Under the premise of striving for the first 7 More ring oscillators are placed on each chip location?

图 1 Imposition diagram

表 2 芯片面积

| 序号 | 1 | 2 | 3 | 4 | 5 | 6 |

|---|---|---|---|---|---|---|

mm mm | 1.76 | 1.046 | 1.096 | 1.05 | 1.77 | 1.5 |

mm mm | 1.46 | 1. 146 | 0.846 | 2. 16 | 0.8 | 0.5 |

边栏推荐

- 2022.8.3

- Marketing Suggestions | You have an August marketing calendar to check! Suggest a collection!

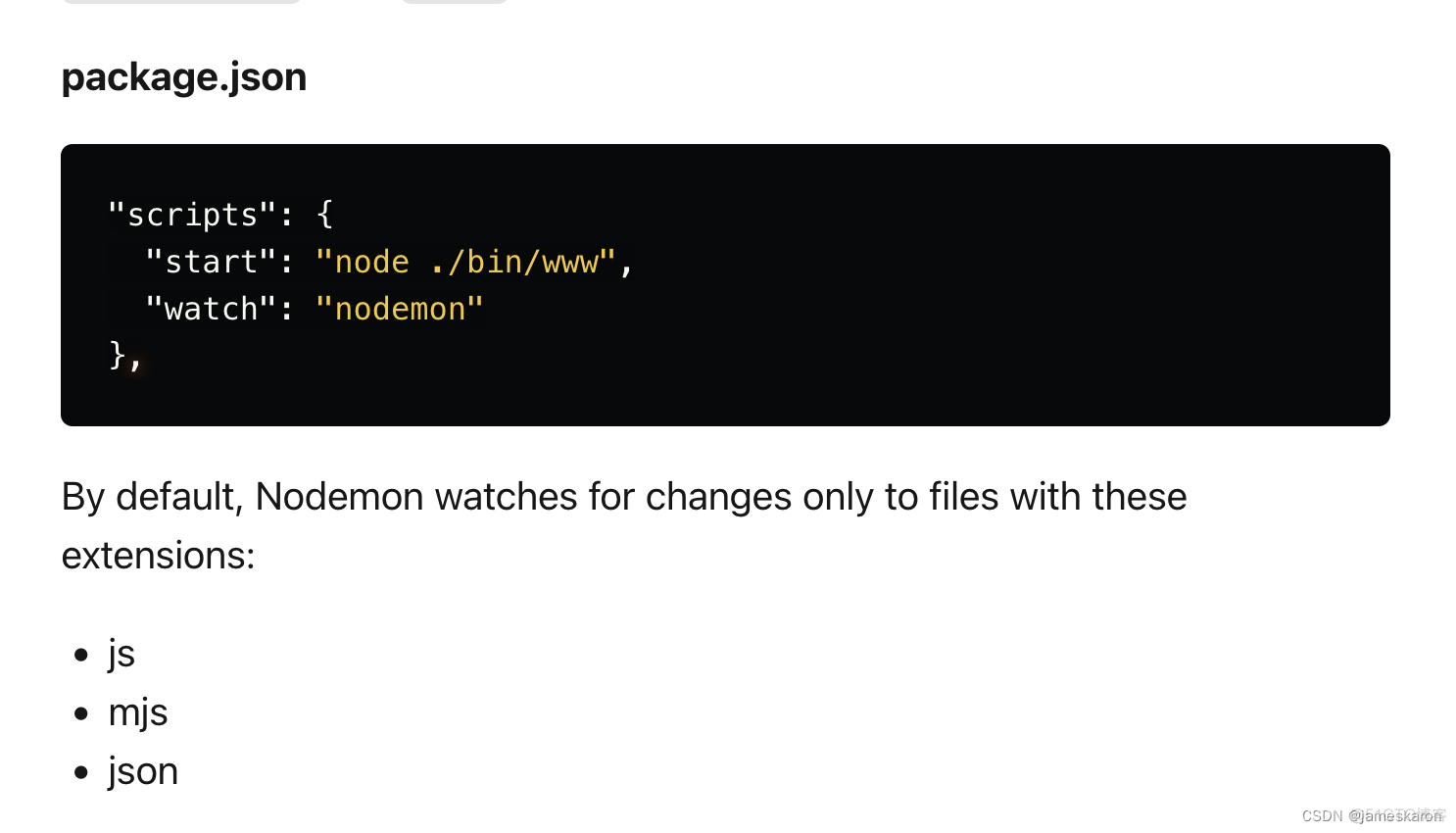

- egg框架使用(二)

- 【Unity】【UGUI】【在屏幕上显示文本】

- CPU的亲缘性affinity

- 仿SBUS与串口数据固定转换

- 韦东山 数码相框 项目学习(六)tslib的移植

- Egg framework usage (1)

- Wei Dongshan Digital Photo Frame Project Learning (6) Transplantation of tslib

- PAT乙级-B1019 数字黑洞(20)

猜你喜欢

随机推荐

无题十二

DFINITY 基金会创始人谈熊市沉浮,DeFi 项目该何去何从

CPU的亲缘性affinity

Dry goods!Generative Model Evaluation and Diagnosis

js劫持数组push方法

Meteorological data processing example - matlab string cutting matching and R language date matching (data splicing)

正则表达式replaceAll()方法具有什么功能呢?

EU | Horizon 2020 ENSEMBLE: D2.13 SOTIF Safety Concept (Part 2)

Voice conversion相关语音数据集综合汇总

自定义过滤器和拦截器实现ThreadLocal线程封闭

皕杰报表的下拉框联动

Science bosses say | Hong Kong rhubarb KaiBin teacher take you unlock the relationship between the matrix and 6 g

PAT乙级-B1020 月饼(25)

浅析WSGI协议

CCVR eases heterogeneous federated learning based on classifier calibration

hcip BGP enhancement experiment

egg框架使用(一)

dotnet OpenXML parsing PPT charts Getting started with area charts

技术干货 | 基于 MindSpore 实现图像分割之豪斯多夫距离

攻防世界-PWN-new_easypwn