当前位置:网站首页>Verilog grammar basics HDL bits training 06

Verilog grammar basics HDL bits training 06

2022-07-26 00:33:00 【Nanyou school slag】

Here's the catalog title

- Combinational Logic:Basic Gates

- One 、Wire

- Two 、GND

- 3、 ... and 、NOR

- Four 、Another gate

- 5、 ... and 、Two gates

- 6、 ... and 、More logic gates

- 7、 ... and 、7420 chip

- 8、 ... and 、Truh tables

- Nine 、Two-bit equality

- Ten 、Simple circuit A

- 11、 ... and 、Simple circuit B

- Twelve 、Combine circuits A and B

- 13、 ... and 、Ring or vibrate

- fourteen 、Thermostat

- 15、 ... and 、3-bit population count

- sixteen 、Gates and vectors

- seventeen 、Even longer vectors

Combinational Logic:Basic Gates

One 、Wire

- RTL Code

module top_module (

input in,

output out);

assign out = in;

endmodule

Two 、GND

- RTL Code

module top_module (

output out);

assign out = 1'b0;

endmodule

3、 ... and 、NOR

module top_module (

input in1,

input in2,

output out);

assign out = ~(in1 | in2);

endmodule

Four 、Another gate

- RTL Code

module top_module (

input in1,

input in2,

output out);

assign out = in1 & (~in2);

endmodule

5、 ... and 、Two gates

- RTL Code

module top_module (

input in1,

input in2,

input in3,

output out);

assign out = ~(in1 ^ in2) ^ in3;

endmodule

6、 ... and 、More logic gates

- RTL Code

module top_module(

input a, b,

output out_and,

output out_or,

output out_xor,

output out_nand,

output out_nor,

output out_xnor,

output out_anotb

);

assign out_and = a & b;

assign out_or = a | b;

assign out_xor = a ^ b;

assign out_nand = ~(a & b);

assign out_nor = ~(a | b);

assign out_xnor = ~(a ^ b);

assign out_anotb = a & (~b);

endmodule

- Simulation oscillogram

7、 ... and 、7420 chip

- RTL Code

module top_module (

input p1a, p1b, p1c, p1d,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

assign p1y = ~(p1a & p1b & p1c & p1d);

assign p2y = ~(p2a & p2b & p2c & p2d);

endmodule

- Simulation oscillogram

8、 ... and 、Truh tables

This problem can be hard solved , The box case Statement lists all Probably , Of course , What this topic wants to examine is the knowledge points of listing logical expressions according to the truth table , It is recommended to use Karnaugh map method to simplify

- case sentence RTL Code

module top_module(

input x3,

input x2,

input x1, // three inputs

output f // one output

);

always @(*)

case({

x3,x2,x1})

3'd2,3'd3,3'd5,3'd7:

f = 1'b1;

3'd0,3'd1,3'd4,3'd6:

f=1'b0;

default: f = 1'b0;

endcase

endmodule

- Logical expression RTL Code

module top_module(

input x3,

input x2,

input x1, // three inputs

output f // one output

);

assign f = ((~x3)&x2&(~x1))|((~x3)&x2&x1)|(x3&(~x2)&x1)|(x3&x2&x1);

endmodule

Nine 、Two-bit equality

- RTL Code

module top_module ( input [1:0] A, input [1:0] B, output z );

assign z = (A == B)? 1'b1:1'b0;

endmodule

Ten 、Simple circuit A

- RTL Code

module top_module (input x, input y, output z);

assign z = (x ^ y) & x;

endmodule

11、 ... and 、Simple circuit B

- RTL Code

module top_module ( input x, input y, output z );

assign z = (x == y)? 1'b1:1'b0;

endmodule

- Simulation oscillogram

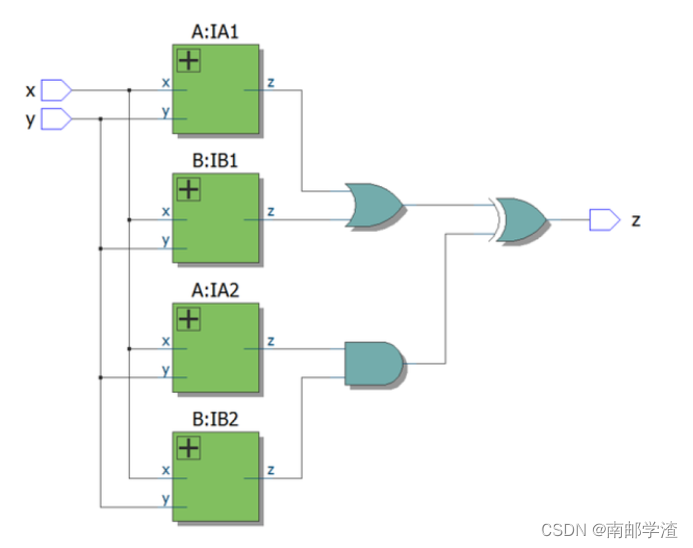

Twelve 、Combine circuits A and B

This question needs to use the sentences of the first two questions to pave the way

- RTL Code

module top_module (input x, input y, output z);

wire z_A;

wire z_B;

assign z_A = (x ^ y) & x;

assign z_B = (x == y)? 1'b1:1'b0;

assign z = (z_A | z_B) ^ (z_A & z_B);

endmodule

13、 ... and 、Ring or vibrate

You can see the code by looking at the simulation waveform

- RTL Code

module top_module (

input ring,

input vibrate_mode,

output ringer, // Make sound

output motor // Vibrate

);

always @(*)

if(ring & !vibrate_mode)begin

motor = 1'b0;

ringer = 1'b1;

end

else if(vibrate_mode & ring)begin

ringer = 1'b0;

motor = 1'b1;

end

else begin

ringer = 1'b0;

motor = 1'b0;

end

endmodule

- Simulation oscillogram

fourteen 、Thermostat

Make a thermostat control unit

- RTL Code

module top_module (

input too_cold,

input too_hot,

input mode,

input fan_on,

output heater,

output aircon,

output fan

);

assign heater = mode & too_cold & (!aircon);

assign aircon = (!mode) & too_hot & (!heater);

assign fan = heater | aircon | fan_on;

endmodule

- Simulation oscillogram

15、 ... and 、3-bit population count

- RTL Code

module top_module(

input [2:0] in,

output [1:0] out );

integer i;

always @(*)begin

out = 1'b0;

for(i=0;i<3;i=i+1)

if(in[i])

out = out + 1'b1;

else

out = out;

end

endmodule

- Simulation oscillogram

sixteen 、Gates and vectors

- RTL Code

module top_module(

input [3:0] in,

output [2:0] out_both,

output [3:1] out_any,

output [3:0] out_different );

integer i;

always @(*)begin

for(i=0;i<3;i=i+1)

begin

out_both[i] = in[i] & in[i+1];

out_any[3-i] = in[3-i] | in[2-i];

out_different[i] = in[i] ^ in[i+1];

end

end

assign out_different[3] = in[3] ^ in[0];

endmodule

- Simulation oscillogram

seventeen 、Even longer vectors

- RTL Code

module top_module(

input [99:0] in,

output [98:0] out_both,

output [99:1] out_any,

output [99:0] out_different );

integer i;

always @(*)begin

for(i=0;i<99;i=i+1)

begin

out_both[i] = in[i] & in[i+1];

out_any[99-i] = in[99-i] | in[98-i];

out_different[i] = in[i] ^ in[i+1];

end

end

assign out_different[99] = in[99] ^ in[0];

endmodule

边栏推荐

猜你喜欢

Private cloud disk setup

对比7种分布式事务方案,还是偏爱阿里开源的Seata(原理+实战)

牛血清蛋白修饰酚酸类及生物碱类小分子/偶联微球的蛋白/牛红细胞SOD的研究

FreeRTOS personal notes - mutex

【redis】③ 数据淘汰策略、pipeline 管道命令、发布订阅

Modeling and simulation analysis of online medical crowdfunding communication based on SEIR model

Thymeleaf view integration

sql(基础二)

为了拿捏 Redis 数据结构,我画了 40 张图(完整版)

MySQL - master-slave replication

随机推荐

Nodejs学习资源

Get JD product details original data API

In order to grasp the redis data structure, I drew 40 pictures (full version)

Flask发送验证码逻辑

Wechat applet for loop

What is software testing peer review?

Tid-mop: a comprehensive framework for security management and control under the scenario of data exchange

自动化测试之数据驱动DDT

Trial division -- power of 3

Markdown writing platform

Research on the influence of opinion leaders based on network analysis and text mining

Verilog语法基础HDL Bits训练 05

After using MQ message oriented middleware, I began to regret

【目录】mqtt、nodejs项目

Jd.com API for obtaining recommended product list

2022/7/25 考试总结

TID-MOP:面向数据交易所场景下的安全管控综合框架

Research on text classification of e-commerce comments based on mffmb

FreeMarker view integration

试除法--3的幂