当前位置:网站首页>(4)UART应用设计及仿真验证2 —— TX模块设计(无状态机)

(4)UART应用设计及仿真验证2 —— TX模块设计(无状态机)

2022-07-05 22:54:00 【少卿不在大理寺】

前言:再次回顾这个小项目已是几个月后了,在后续的学习中,新的老师在不断强调,实际工作中尽量少用状态机,整理文章时忘了当时他咋说的了。所以我试着自己重新写一下UART,整理一个不带状态机的版本。

这里有几个基础的逻辑点要再次回顾一下:

1)完整的一帧数据格式包含:起始位,有效数据位,校验位,停止位;

2)计算单bit数据的传输时间:利用baoud(波特率)和clk(系统时钟),波特率单位bit per second,时钟Hz单位time per second ,所以时钟除以波特率得到的就是time per bit,即每bit对应多少个时钟周期;

3)参考信号:传输信号baoud_cnt_half,每bit计数到一半的时候,传递数据;切换计数信号baoud_cnt_end,每bit计数完的时候,进入下一轮计数周期;位计数bit_cnt,计算一帧数据中传递到第几位了;传输过程标志信号start_flag,贯穿每一次的数据传输。

上代码:

//date:2022.6.30

//edgar.yao

//uart_tx block

module uart_tx(

input clk,

input rst_n,

input[7:0] cmd_data,

input data_valid,

output tx,

output tx_read边栏推荐

- 终于搞懂什么是动态规划的

- Getting started stm32--gpio (running lantern) (nanny level)

- VOT toolkit environment configuration and use

- 透彻理解JVM类加载子系统

- Paddy serving v0.9.0 heavy release multi machine multi card distributed reasoning framework

- 判斷二叉樹是否為完全二叉樹

- 媒体查询:引入资源

- Vcomp110.dll download -vcomp110 What if DLL is lost

- Methods modified by static

- SPSS analysis of employment problems of college graduates

猜你喜欢

How to quickly understand complex businesses and systematically think about problems?

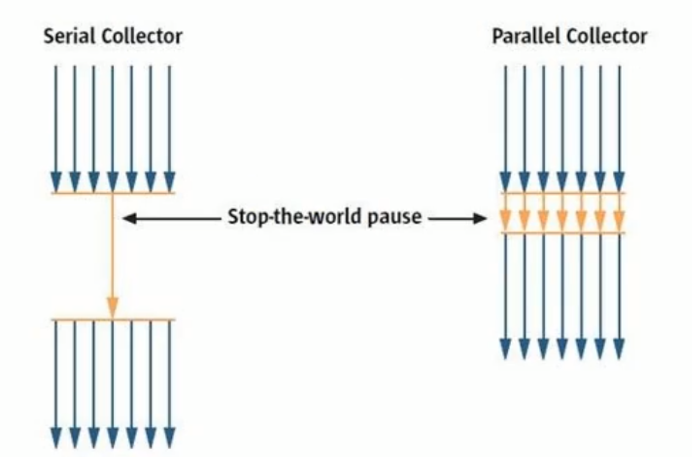

Yiwen gets rid of the garbage collector

Element operation and element waiting in Web Automation

![[digital signal denoising] improved wavelet modulus maxima digital signal denoising based on MATLAB [including Matlab source code 1710]](/img/b4/af689abb3ad4e25988f2d17152406e.jpg)

[digital signal denoising] improved wavelet modulus maxima digital signal denoising based on MATLAB [including Matlab source code 1710]

d3dx9_ How to repair 31.dll_ d3dx9_ 31. Solution to missing DLL

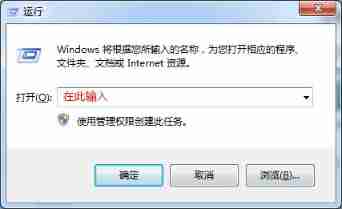

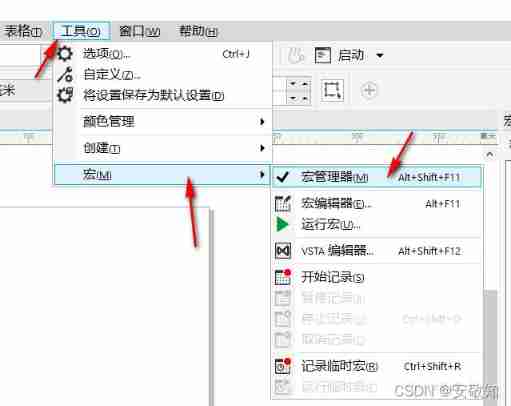

CorelDRAW plug-in -- GMS plug-in development -- new project -- macro recording -- VBA editing -- debugging skills -- CDR plug-in (2)

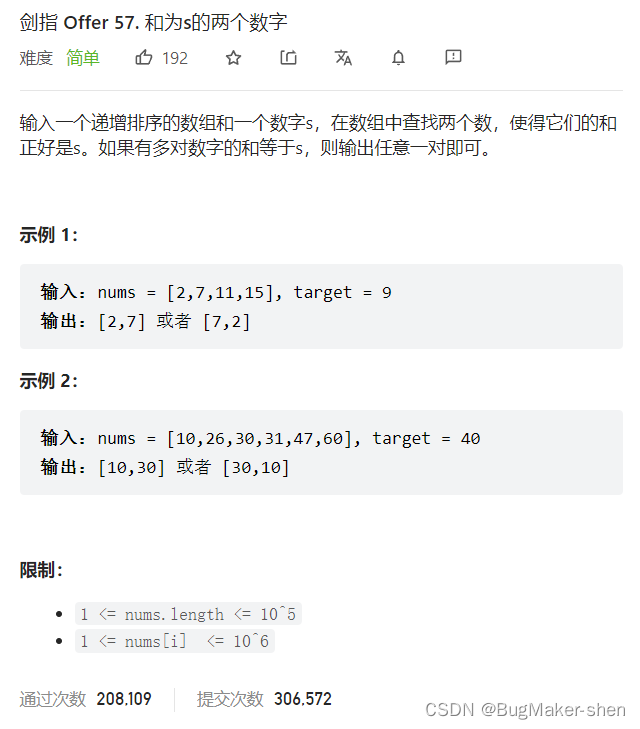

Sum of two numbers, sum of three numbers (sort + double pointer)

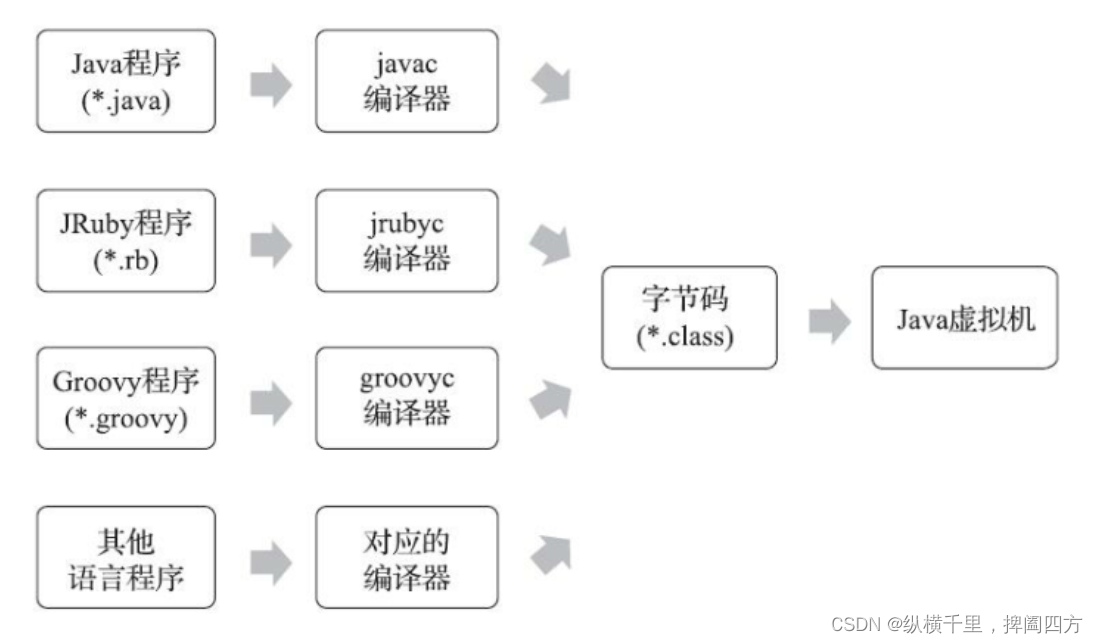

透彻理解JVM类加载子系统

Hcip day 12 (BGP black hole, anti ring, configuration)

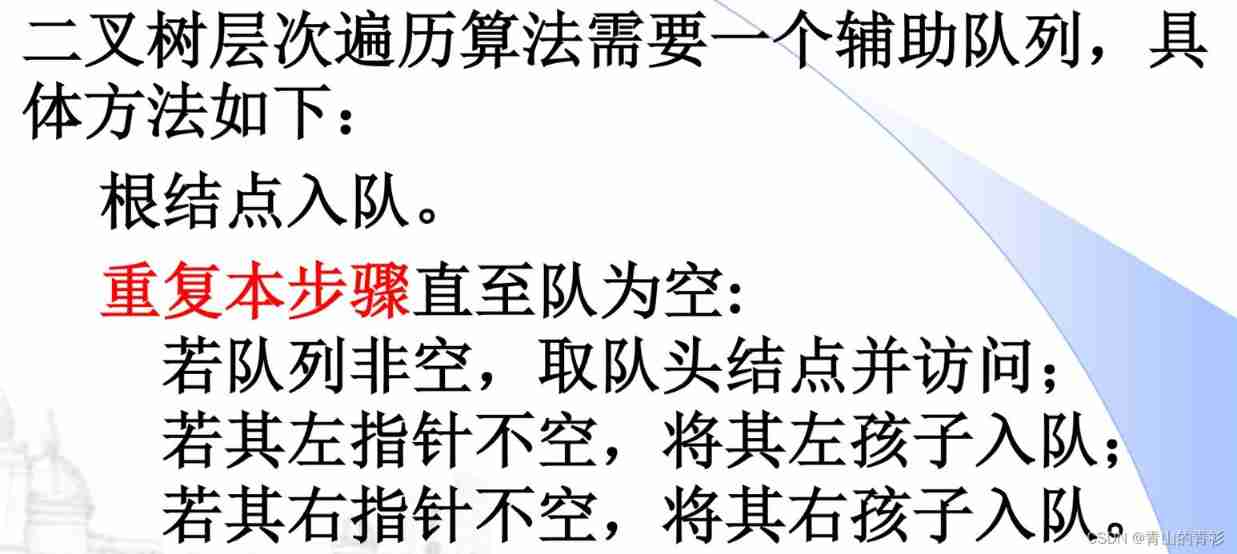

LeetCode102. Sequence traversal of binary tree (output by layer and unified output)

随机推荐

2022 G3 boiler water treatment simulation examination and G3 boiler water treatment simulation examination question bank

判断二叉树是否为完全二叉树

【Note17】PECI(Platform Environment Control Interface)

14种神笔记方法,只需选择1招,让你的学习和工作效率提高100倍!

3:第一章:认识JVM规范2:JVM规范,简介;

Non rigid / flexible point cloud ICP registration

The difference between MVVM and MVC

C Primer Plus Chapter 9 question 10 binary conversion

基于STM32的ADC采样序列频谱分析

Un article traite de la microstructure et des instructions de la classe

Déterminer si un arbre binaire est un arbre binaire complet

openresty ngx_lua请求响应

[screen recording] how to record in the OBS area

d3dx9_ How to repair 31.dll_ d3dx9_ 31. Solution to missing DLL

Hcip day 12 (BGP black hole, anti ring, configuration)

Metasploit (MSF) uses MS17_ 010 (eternal blue) encoding:: undefined conversionerror problem

Marginal probability and conditional probability

VOT toolkit environment configuration and use

6-axis and 9-axis IMU attitude estimation

Vcomp110.dll download -vcomp110 What if DLL is lost