当前位置:网站首页>[play with FPGA learning 2 in simple terms ----- design skills (basic grammar)]

[play with FPGA learning 2 in simple terms ----- design skills (basic grammar)]

2022-07-02 11:02:00 【Ape Zhou】

Play in depth FPGA Study 2---- Design skills ( Basic grammar )

Basic grammar ( Comprehensive Verilog A collection of methods )

The so-called comprehensive Verilog grammar , It refers to some grammars that can be implemented by hardware . frequently-used RTL The syntax is as follows :

Module declaration :module…endmodule.

Port declaration :input,output,inout(inout The usage of , We need to pay attention to ).

Signal type :wire,reg,tri etc. ,integer Commonly used in for In the sentence (reg,wire Is the most commonly used , commonly tri and integer Used in test scripts ).

Parameters are defined :parameter.

Operator : Various logical operators 、 Move operator 、 Arithmetic operators are mostly integrable ( notes :=== And !== It's not comprehensive )

Comparative judgment :if…else,case(casex,casez)…default…endcase.

Continuous assignment :assign, Question mark expression (?:).

always modular : The sensitive meter can be level 、 Along the signal posedge/negedge; Usually and @ Continuous use .

begin…end ( Popular said , It is C In the language “{}”).

Task definition :task…endtask.

Loop statement :for( And less , But using it in some specific designs will get twice the result with half the effort )

Assignment symbol := and <=( Blocking and non blocking assignment , It is very particular in the specific design ).

The comprehensive grammar is Verilog A small subset of available grammars , The essence of hardware design is to try to use the simplest sentences to describe the most complex hardware , This is the essence of hardware description language .

If…else And case analysis of sentences

The two structures are completely consistent

Two pieces of code ,EX1 Use if…else sentence ,EX2 Use case sentence .

//EX1

input clk;

input rst_n;

input[3:0] data;

output[2:0] add;

reg[2:0] add;

always @(posedge clk) begin

if(!rst_n) begin

add<=0;

end

else begin

if(data<4) add<=1;

else if (data<8) add<=2;

else if(data<12) add<=3;

else add<=4;

end

end

// EX2

input clk;

input rst_n;

input[3:0] data;

output[2:0] add;

reg[2:0] add;

always @(posedge clk) begin

if(!rst_n) begin

add<=0;

end

else begin

case(data)

0,1,2,3: add<=1;

4,5,6,7: add<=2;

8,9,10,11: add<=3;

12,13,14,15: add<=4;

default: ;

endcase

end

end

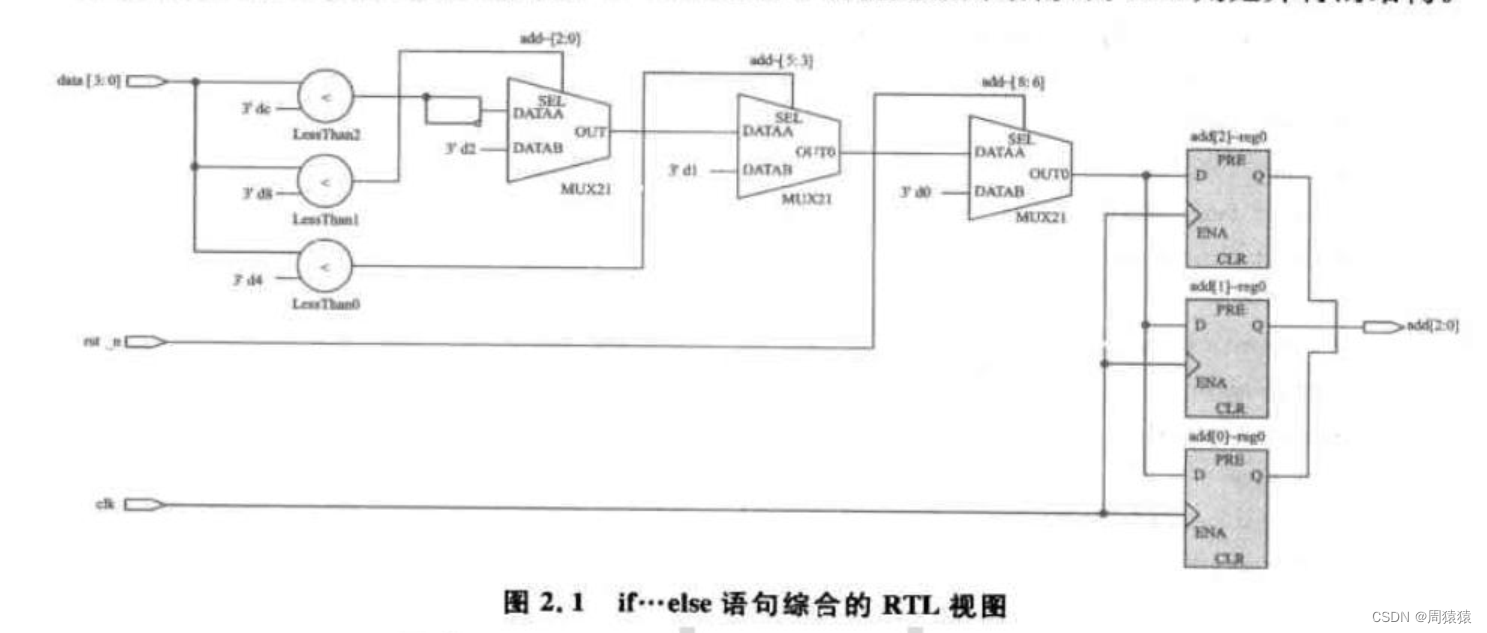

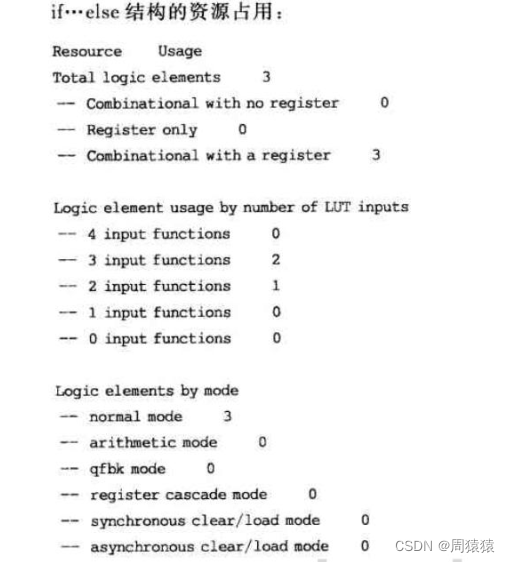

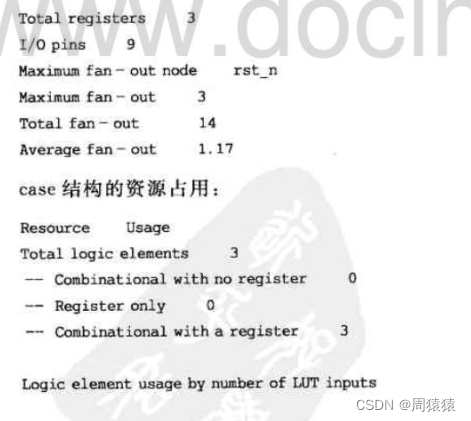

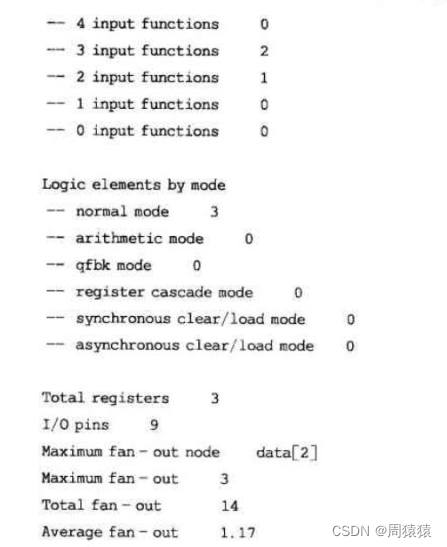

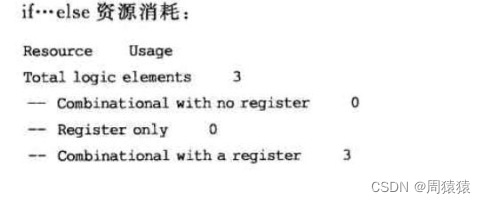

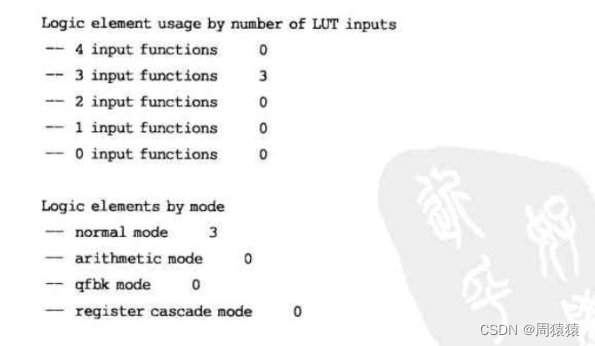

chart 2.1 Sum graph 2.2 Namely if…else Statement and case After sentence synthesis RTL View . Single from RTL View , There are obvious differences between the results of the two after synthesis .if…else Tends to have priority structures , and case Is a parallel structure .

Next, let's take a look at the resources they occupy . The resource occupation of the two is basically the same , Even the average fan out is the same .

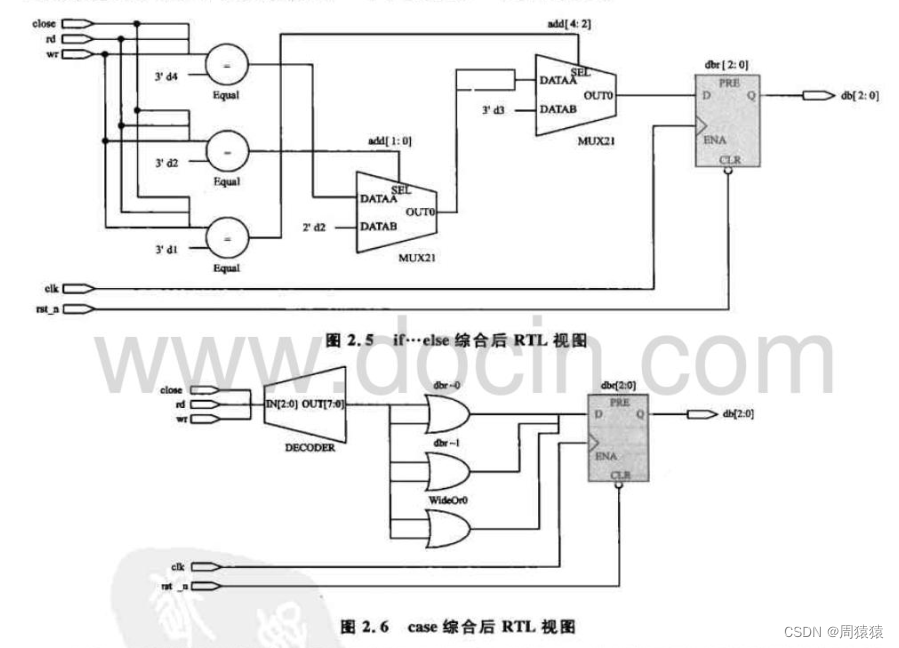

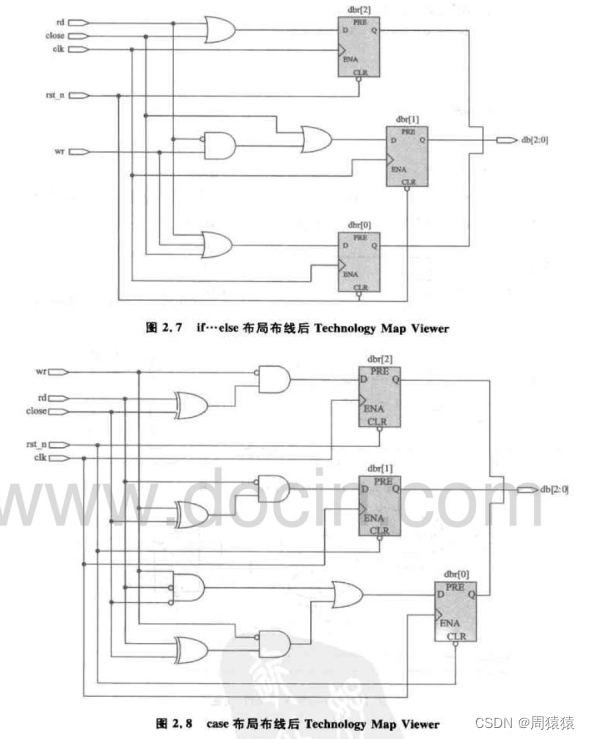

Look at their Technology Map Viewer, Separately shown 2.3 Sum graph 2.4 Shown . The two are exactly the same , therefore , To be clear , In this case ,if…else and else The final implementation of statements is parallel , And exactly the same .

The two structures are different

// if...else Sample code

input clk;

input rst_n;

input close ,wr, rd;

output[2:0] db;

reg[2:0] dbr;

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

dbr<=3'd0;

end

else begin

if(close) dbr <=3'b111;

else if(rd) dbr <=3'b101;

else if(wr) dbr <=3'b011;

else dbr <= 3'd0;

end

end

assign db =dbr;

// case Sample code

input clk;

input rst_n;

input close ,wr, rd;

output[2:0] db;

reg[2:0] dbr;

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

dbr<=3'd0;

end

else begin

case({close,rd,wr})

3'b100:dbr <= 3'b111;

3'b010: dbr <=3'b101;

3'b001: dbr <=3'b011;

default:dbr <= 3'do;

endcase

end

end

assign db =dbr;

For the above two codes , Analyze only from the code ,if…else It has priority ,case It's a parallel structure .

The resource consumption of the two is different , Then the final realization of the two is not necessarily different .

from RTL View view , The realization of the two is exactly as expected , One with priority , A parallel processing .

From the final layout and structure after wiring , and RTL The view is very close , These two sample codes are used if…else and case The structure of the final implementation is different .

From the previous strength analysis, this is not uncommon , The unexpected thing is to use if…else The structure resource consumption of the implementation is unexpectedly higher than case Less to come ( It is a relative term ). Such a result seems to refute the so-called “ multi-purpose case sentence , To use less if…else sentence , Because implementing a prioritized structure is more resource consuming than a parallel structure ” The verdict of .

in addition , In this example, multiple if…if… The result of statement implementation will be similar to case The result of the statement is consistent .

// if...if.... Sample code

input clk;

input rst_n;

input close ,wr, rd;

output[2:0] db;

reg[2:0] dbr;

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

dbr<=3'd0;

end

else begin

dbr <=3'd0;

if({close,rd,wr}==3'b100) dbr<=3'b111;

if({close,rd,wr}==3'b010) dbr <=3'b101;

if({close,rd,wr}==3'b001) dbr <=3'b011;

end

end

assign db =dbr;

Verilog Code optimization for sentence

Verilog Medium for Although the sentence is also comprehensive , But in RTL Level code is basically not used . On the one hand, it's because for The use of statements takes up a lot of hardware resources , On the other hand, sequential logic design is often used in design , be used for There are not many places to cycle .

Here is an example to illustrate for The result of the comprehensive implementation of circular statements .

module test_3(clk,rst_n,data,num);

input clk;

input rst_n;

input[12:0] data; // Input 13 Road data

output[15:0] num; //13 The number of channels with high data level

reg[3:0] i;

reg[15:0] num;

always @ (posedge clk) begin

if(!rst_n) begin

num <=0;

end

else begin

for(i=0;i<13;i=i+1) // use for Cycle through the calculation

if(data[i]) num<= num+1;

end

end

endmodule

The purpose of this code is to calculate 13 The number of high-level pulse signals , Most people will feel that this task is entrusted to for It's best to do it in a cycle , however for The loop cannot complete this task .

I believe you have found the problem , Why every clock cycle for The loop only executes this num<=num+1 Well ?always Statement using non blocking assignment “<=” when , Is in always After that, assign the value to the register on the left , Therefore, the above situation appears . Write the following code again with blocking statements :

module test_3(clk,rst_n,data,num);

input clk;

input rst_n;

input[12:0] data; // Input 13 Road data

output[15:0] num; //13 The number of channels with high data level

reg[3:0] i;

reg[15:0] num;

always @ (posedge clk) begin

if(!rst_n) begin

num =0;

end

else begin

for(i=0;i<13;i=i+1) // use for Cycle through the calculation

if(data[i]) num = num+1;

end

end

assign numout = num;

endmodule

The waveform simulated by the modified code is shown in the figure :

This waveform shows that the modified code has achieved the experimental purpose . It seems for In this case, the statement is relatively easy , If not for The sentence is more complicated . But then again ,for The efficiency of sentence synthesis is not high , On the premise of not requiring high speed , Or would you rather use multiple clock cycles than for sentence .

Besides , Generally, non blocking assignment statements are used in temporal logic "<=", The style of the following code is actually undesirable . Hardware language cannot be like C Language pursues the simplicity of code one sidedly .

inout usage

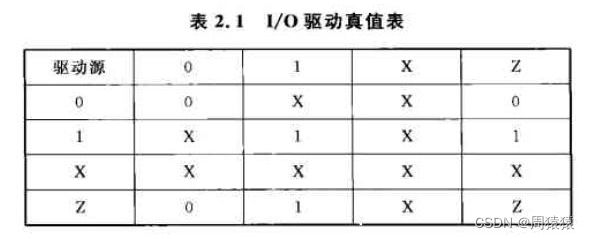

As shown in the table , It indicates that under the same driving intensity , Two driven wire The type and tri Truth table of type variable .

If at some point inout Port has input , At this time, I just want to take this inout Port for output , Then conflict is inevitable , Refer to the truth table for what results will appear .

Here's a typical inout How to use the port :

inout io_data; //inout mouth

reg out_data; // Data to be output

reg io_link; //inout Mouth direction control

assign io_data = io_link ? out_data : 1'bz; // This is the key

When inout When the port is used as an input port , Be sure to put it in the high resistance state , Let the io_link=0 that will do ; When inout When the port is used as an output , Then io_link =1, Yes out_data The assignment is OK .

边栏推荐

- [applinking practical case] share in app pictures through applinking

- 记录 AttributeError: ‘NoneType‘ object has no attribute ‘nextcall‘

- 【快应用】Win7系统使用华为IDE无法运行和调试项目

- 二叉树专题--AcWing 47. 二叉树中和为某一值的路径(前序遍历)

- Mysql database remote access permission settings

- 【付费推广】常见问题合集,推荐榜单FAQ

- Special topic of binary tree -- acwing 19 The next node of the binary tree (find the successor of the node in the tree)

- 二叉树专题--AcWing 19. 二叉树的下一个节点(找树中节点的后继)

- Luogu p5536 [xr-3] core city (greed + tree DP looking for the center of the tree)

- UVM——Callback

猜你喜欢

![[TS] 1368 seconds understand typescript generic tool types!](/img/2b/58a850b52ce8a9b2e6e7b6b72b0fe5.jpg)

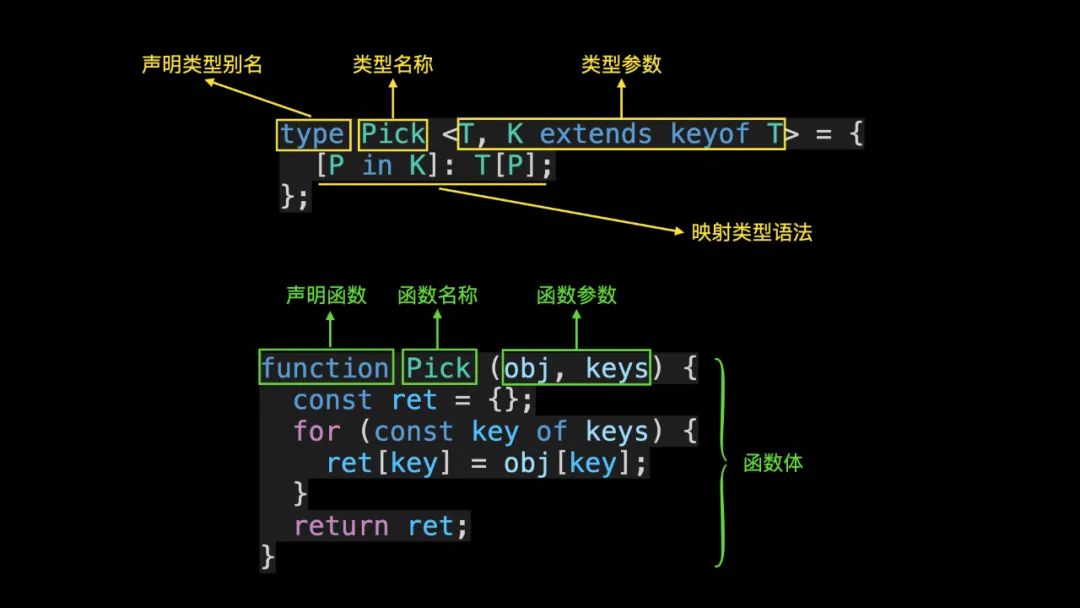

[TS] 1368 seconds understand typescript generic tool types!

二叉树专题--AcWing 1497. 树的遍历(利用后、中序遍历,构建二叉树)

Special topic of binary tree -- acwing 1497 Traversal of the tree (use post and mid order traversal to build a binary tree)

![[SUCTF2018]followme](/img/63/9104f9c8bd24937b0fc65053efec96.png)

[SUCTF2018]followme

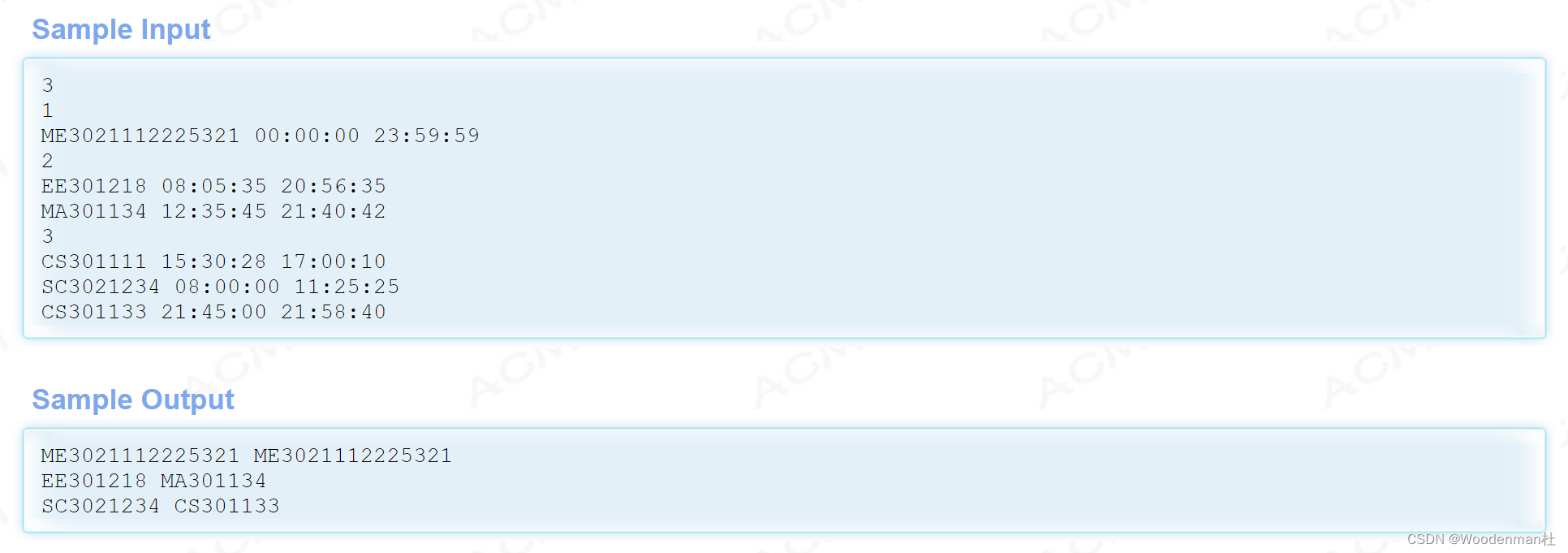

HDU1234 开门人和关门人(水题)

全网显示 IP 归属地,是怎么实现的?

【TS】1368- 秒懂 TypeScript 泛型工具类型!

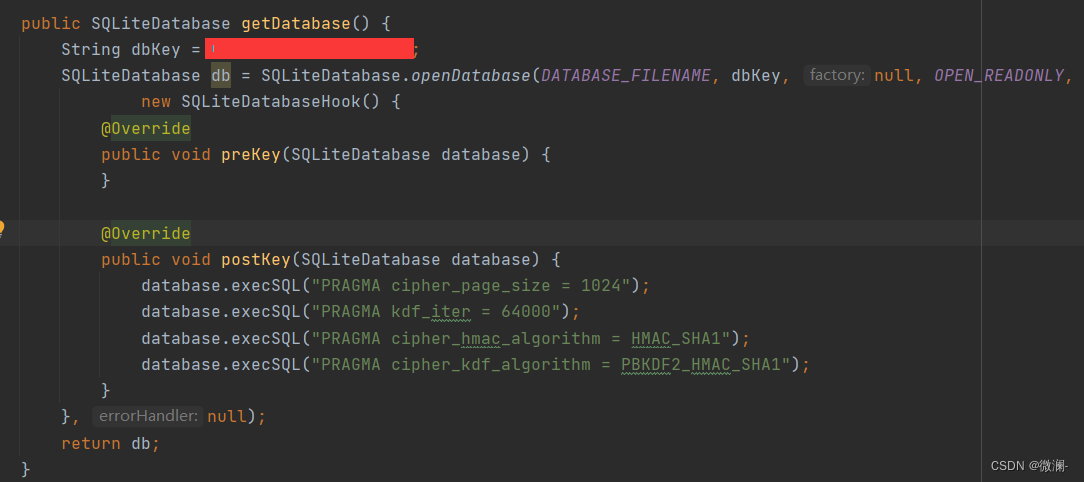

Open the encrypted SQLite method with sqlcipher

2022-06-17

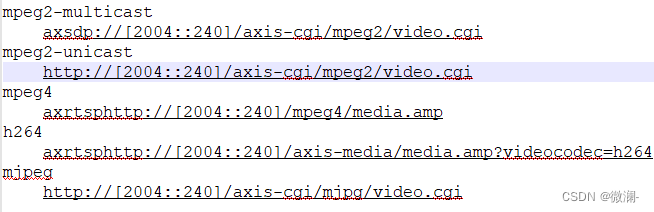

The URL in the RTSP setup header of the axis device cannot take a parameter

随机推荐

集成学习概览

Is the account above changtou school safe?

Uncover the secrets of Huawei application market application statistics

计算序列之和

From Read and save in bag file Jpg pictures and PCD point cloud

二叉树专题--AcWing 1497. 树的遍历(利用后、中序遍历,构建二叉树)

洛谷 P1892 [BOI2003]团伙(并查集变种 反集)

Logu p3398 hamster looks for sugar (double LCA on the tree to judge whether the two paths in the tree intersect)

二叉树专题--AcWing 3540. 二叉搜索树建树(实用板子 构建二叉搜索树 并输出前、中、后序遍历)

一招快速实现自定义快应用titlebar

PCL point cloud to depth image

Special topic of binary tree -- [deep base 16. Example 7] ordinary binary tree (simplified version) (multiset seeks the precursor and subsequent sentry Art)

[ark UI] implementation of the startup page of harmonios ETS

二叉树专题--AcWing 47. 二叉树中和为某一值的路径(前序遍历)

Special topic of binary tree -- acwing 47 Path with a certain value in binary tree (preorder traversal)

洛谷 P5536 【XR-3】核心城市(贪心 + 树形 dp 寻找树的中心)

Record attributeerror: 'nonetype' object has no attribute 'nextcall‘

JVM之垃圾回收器

UVM factory mechanism

洛谷 P3398 仓鼠找 sugar(树上倍增 lca 判断树中两条路径是否相交 结论)