当前位置:网站首页>IP core summary

IP core summary

2022-07-27 06:20:00 【Three assassins】

IP Nuclear Overview

IP(Intellectual Propery) That is, intellectual property . The semiconductor industry will IP Nuclear is defined as “ be used for ASIC or FPGA The pre designed circuit function module in ”. In short , there IP Namely circuit function module . In digital circuits , Common and complex functional modules are designed into modules with modifiable parameters , Let other users call these modules directly , This is it. IP nucleus . Popular speaking ,IP A kernel is a library function , You can call the function inside directly , Then modify the parameters by yourself .

Why use IP nucleus

With FPGA Getting bigger and bigger , Design is getting more and more complicated , The main task of the designer is to pass i Complete complex design within the time period of the top . To solve this problem , Some are commonly used in digital circuits , But the more complex function block , Such as FIR filter 、SDRAM controller 、PCI The interface is designed as a module that can modify parameters , This can avoid repeated work , Improve development efficiency .

IP Types of nuclei

IP Nuclear behavior (Behavior) level 、 structure (Structure) Level and Physics (Physical) Three levels of classification , There are three different forms of existence :HDL linguistic form 、 Net list form 、 Layout form . They correspond to the three categories we often say IP nucleus : Soft nucleus 、 Solid core hard core . This classification is mainly based on the way of product delivery .

- HDL linguistic form Soft nucleus

Hardware description language ; Parameters can be adjusted 、 Strong reusability ; Layout 、 Flexible wiring ; The design cycle is short 、 Less design investment , You can't see the internal wiring , Actually RTL Invisible to users .

- - Net list form Solid core

Complete the integrated function block ; Specific wiring resources can be allocated to specific pre wired signals . It's nothing but completion IP Soft core all the design , The design links such as gate level circuit synthesis and timing simulation are also completed . In a general way , It is provided to users in the form of gate level circuit net list .

- Layout form hardcore

Hard core is the final stage product to complete the design - A mask (Mask); inflexibility 、 Poor portability ; Easier to implement IP nuclear protection

IP The disadvantages of nuclear

1. Across platforms ,IP Nuclear is often not universal , Need to redesign .IP The nuclei are not completely transparent , Is each FPGA The developer can customize the chip according to their own adaptation IP, So if you used it before Xilinx Chip , One was used PLL, But for some reasons, the code needs to be ported to Altera On the platform , Then we must PLL Replace it again , This increases the complexity of code migration .

2. IP The core is a black box , It's opaque , We often don't see its core code .IP The nuclei are all big FPGA Specially designed by the manufacturer , Will be encrypted , The kernel code cannot be seen , If you use this IP In case of problems or need to know its internal structure for customized optimization for specific applications , You cannot modify . The above two problems are very thorny , So some companies insist that all integrable designs are not used IP nucleus , It is to make all the modules in your own hands .

3. Some customized IP Nuclear is not universal , There are often higher fees , This is also a huge expense .

Users have carefully evaluated and selected , bought IP Manufacturer's IP Postnuclear , Start designing your own chip . As I said before , A complex chip is usually purchased by IP The core is composed of circuit parts designed by users . The chip design process includes behavior level 、 Structure level and physical level . The work of behavior level and structure level design stage is generally called front-end design , The work in the physical level design stage is generally called back-end design .

Altera The company provides two types of functional modules : Free of charge LPM Macro function module (Megafunction/LPM) And those that need authorization IP intellectual property right (MegaCore), There are differences in the functions of the two , Use the same way . From the perspective of complexity , Support Altera series FPGA Of IP The core includes both injection logic and arithmetic operations IP nucleus , It also includes digital signal processors 、 Ethernet MAC、PCI/PCI Express Interface and other complex system level construction modules . According to its function ,Altera IP There are mainly the following types of nuclei :

1、 Logical operations IP nucleus . Include and 、 or 、 Not 、 Basic logic operation units such as XOR and multiplexers 、 Circular shifter 、 Relatively complex logic operation modules such as tristate buffer and decoder .

2、 Mathematical operations IP nucleus .Altera Mathematical operation of IP Cores are divided into two categories: integer operation and floating-point operation :(1) Integer operation IP nucleus . Include LPM library ( Parametric model IP library ) Provided IP Nuclear and Altera Specify the function IP nucleus .LPM In the library IP The core has an adder 、 Subtracter 、 Multiplier 、 A divider 、 The comparator 、 Counter and absolute value calculator ;Altera Specify the function IP The core includes an accumulator 、ECC Encoder / decoder 、 Multiplier 、 Constant coefficient multiplier based on storage 、 Multiply accumulator 、 Multiplier 、 Complex number multiplier and integer square root calculator .(2) Floating point operation IP The core includes a floating-point adder 、 Floating point number subtracter 、 Floating point multiplier 、 Floating point divider 、 Floating point square root calculator 、 Floating point index calculator 、 Floating point reciprocal calculator 、 Floating point number square root reciprocal calculator 、 Floating point natural logarithm calculator 、 Floating point sine cosine calculator and arctangent counter 、 Floating point matrix inverse sum multiplier and floating point absolute value calculator 、 Comparators and converters .

3、 Memory class IP nucleus . Including shift odd memory 、 trigger 、 Simple memory such as latches IP Nuclear and more complex ROM、RAM、FIFO and Flash Memory and other modules . in addition ,Altera It also includes RAM Initializer and for part FPGA Series application FIFO Divider and other auxiliary memory design IP nucleus .

4、 Digital signal processing IP nucleus . Including finite impulse response filtering (FIR) compiler 、 Cascade integral comb (CIC) Filter compiler 、 CNC oscillator (NCO) Compiler and fast Fourier transform (FFT) etc. IP nucleus , For digital signal system design .

5、 Digital communications IP Nuclear include RS Coder 、 be used for ひ Product code decoding Viterbi Decoder 、 Cyclic redundancy check (CRC) compiler 、8B/10B Ed / Decoder and SONET/SDH The physical layer IP Nuclear etc .

6、 The image processing IP nucleus . It mainly realizes the functions commonly used in video and image processing systems IP nucleus , Specific have 2D FIR Filter and 2D Median filter 、α Mixer 、 Video monitor 、 Chroma resampler 、 Image clipper 、 Video input and output module 、 Color panel sequencer 、 Color space converter 、 synchronizer 、 Video frame reading and buffer 、γ Corrector 、 Interlacing and deinterlacing scanners 、 Zoomer 、 Switcher 、 Test template generator and video tracking system module .

7、 Input / Output IP nucleus . Mainly including clock controller 、 PLL (PLL)、 Low voltage differential signal (LVDS) Transceiver 、 Dual data rate (DDR)I/O、 Accessing external memory DQ-DQS I/O、I/O Buffer, etc .

8、 Chip interface IP nucleus . Including for digital video broadcasting (DVB) Asynchronous serial interface (AS1)、10/100/1000Mbps Ethernet interface 、DDR and DDR2 SDRAM controller 、 Memory physical layer access interface 、PCI/PCI Exprsss compiler 、RapidIo And serial digital interface for digital TV signal transmission (SDI) etc. .

9、 Design and debugging IP nucleus . Including providing design and debugging functions SignalTap Logic analyzer 、 Serial and parallel Flash loader 、 Source and detection modules in the system and virtual JTAG etc. .

10、 other IP nucleus . There are also some specific parts Altera series FPGA Application specific IP nucleus , Let's not list one by one .

边栏推荐

- 学习软件测试时需要配备的运行环境需求搭建

- [Arduino] reborn Arduino monk (1)

- What is the difference between single line and three line when renting servers in Hong Kong?

- 机器人导航

- socket 长链接

- Acwing the number of square arrays of one question per day

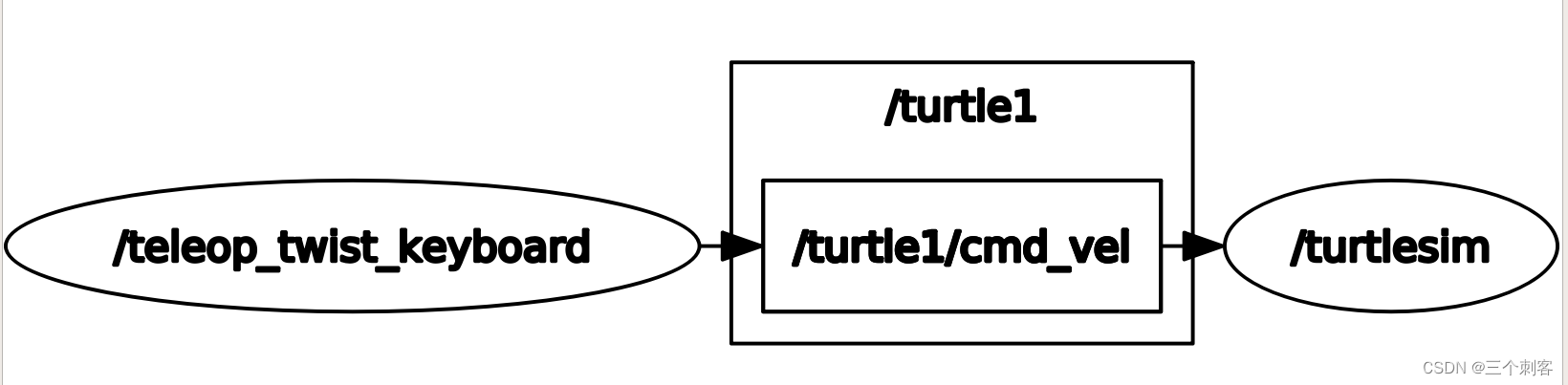

- ROS distributed communication

- ROS工作空间覆盖

- Strategies for common locks in multithreading

- 租用香港服务器时单线与三线有什么区别?

猜你喜欢

Strategies for common locks in multithreading

学习软件测试时需要配备的运行环境需求搭建

Unityshader depth texture (understanding and problems encountered)

ROS topic name setting

Li Kou 236. the nearest common ancestor of binary tree

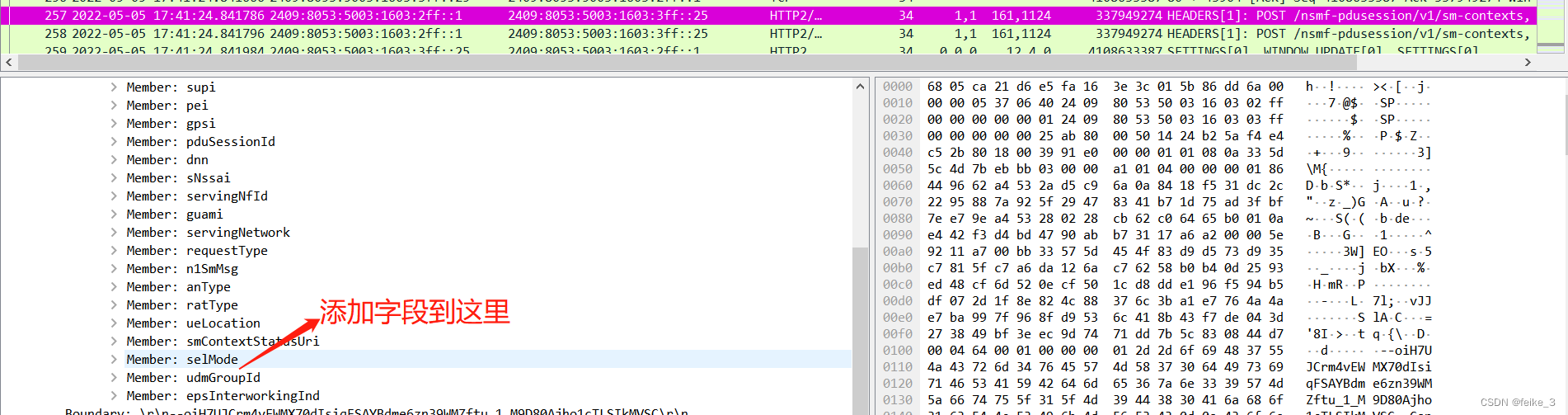

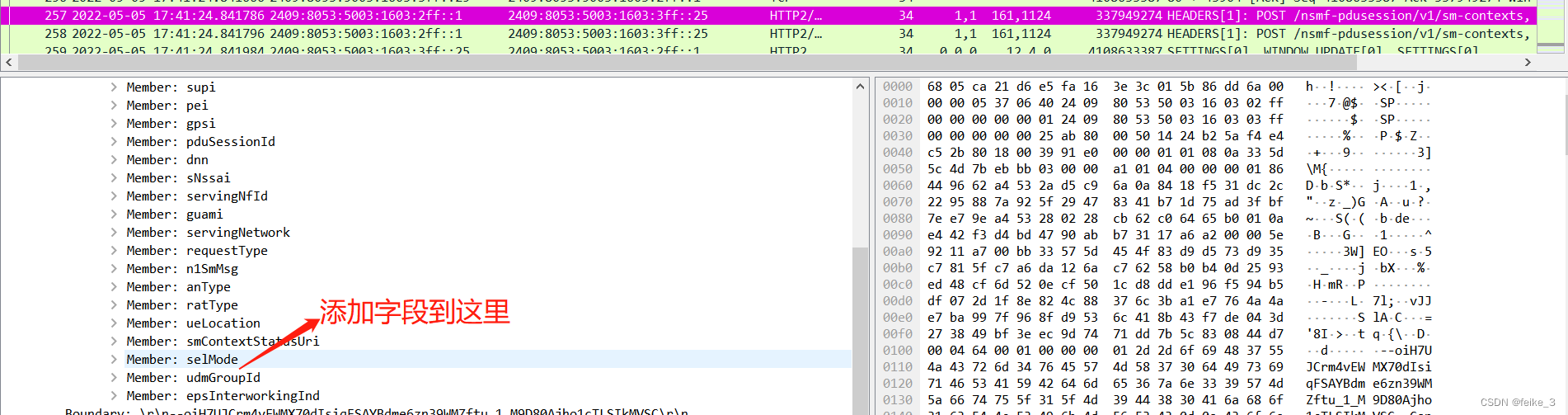

wireshark数据包修改--添加或修改消息字段(二)

Reading and writing of file content - data flow

遥感影像识别-成像合成

5g's past and present life -- a brief introduction to the development of mobile communication

Wireshark packet modification -- adding or modifying message fields (2)

随机推荐

Unity 菜单界面的简单介绍

wireshark图形界面介绍

Dynamic planning for solving problems (5)

Dynamic planning for solving problems (4)

How to distinguish an independent server from a VPS host?

The principle of hash table and the solution of hash conflict

Launch file of ROS operation management

力扣题解 二叉树(7)

学习软件测试时需要配备的运行环境需求搭建

Ulcl function --5gc

Leetcode one question per day 30. Concatenate substrings of all words

Wireshark packet modification -- adding or modifying message fields (2)

无法启动程序,拒绝访问?

IP核之ROM

Progress in remote sensing image recognition 2022/5/5

软件测试基础概念篇

Understand the pointer in a picture

Shell script if nested for loop script

IP核之PLL

Linear progression for face recognition