当前位置:网站首页>Cjc8988 Low Power Stereo codec with 2 stereo headphone drivers

Cjc8988 Low Power Stereo codec with 2 stereo headphone drivers

2022-07-01 05:48:00 【nanfeng775a】

Codec chip - CJC8988 It is a low power , High quality stereo codec , Can directly Pin to Pin replace WM8988, Designed for portable digital audio applications . The device integrates a complete interface to 2 Stereo headphones or line out ports . The requirements for external components are greatly reduced , Because you don't need a separate Headphone Amplifier . Advanced on-chip digital signal processing implements graphic equalizers , Microphone or line input for 3D sound enhancement and automatic level control .

CJC8988 It can operate as a master or a slave , It has various master clock frequencies , Include 12 or 24MHz, Or standard 256fs frequency , Such as 12.288MHz and 24.576MHz. Different audio sampling rates , Such as 96 kHz,48 kHz,44.1 kHz, Directly from the master clock , Without an external PLL.

CJC8988 When the supply voltage drops to 1.8V Work at the same time , Although the digital core can be reduced to 1.5V To save electricity , And the maximum voltage of all power supplies is 3.3 v . Different parts of the chip can also be powered off under software control .CJC8988 Provides a very small and thin 4x4mmCOL package , Ideal for handheld and portable systems .

Codec chip - CJC8988 Characteristics of :

DAC Signal-to-noise ratio 93 dB(“A” weighting ),T hd -87dB stay 48 kHz,1.8V

ADC Signal-to-noise ratio 91 dB(“A” weighting ),THD-81dB stay 48 kHz,1.8V

2 Headphone driver on a chip

-THD-78dB, Signal-to-noise ratio 93 dB,16Ω load Hz,1.8V

Digital graphic equalizer

Low power ( Microscope )

-7.8mW Stereo player (1.8V Power Supply )

-16.8mW Record and playback (1.8V Power Supply )

Low supply voltage

- simulation 1.8V to 3.3V

- Digital movement :1.5V To 3.3V

- Digital input I/O:1.8V to 3.3V

256fs/384fs or USB Master clock rate :12MHz,24MHz

Audio sampling rate :8、11.025、16、22.05、24、32、44.1、48

88.2,96 individual kHz Generated internally from the master clock

4x4mmCOL packing

边栏推荐

猜你喜欢

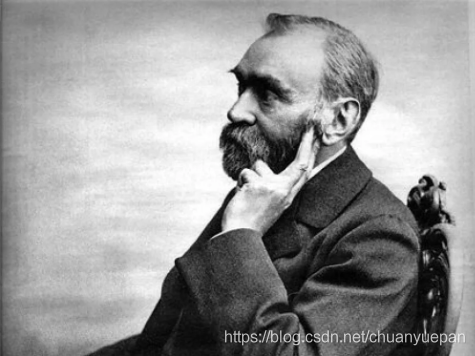

从诺奖知“边缘计算”的未来!

MySQL converts milliseconds to time string

el-table 动态表头渲染 固定第一列 高度问题

Crossing pie · pie pan + Mountain duck = local data management

My experience from technology to product manager

Through cooperation with the University of international trade, we can increase efficiency for college students

ssm+mysql二手交易网站(论文+源码获取链接)

uniapp树形层级选择器

为什么用葫芦儿派盘取代U盘?

扩展点系列之SmartInstantiationAwareBeanPostProcessor确定执行哪一个构造方法 - 第432篇

随机推荐

idea启动查看项目端口

C语言初阶——实现扫雷游戏

Ssm+mysql second-hand trading website (thesis + source code access link)

CentOS 7 installed php7.0 using Yum or up2date

Codeforces Round #803 (Div. 2)vp

ssm+mysql二手交易网站(论文+源码获取链接)

Summary of common components of applet

数据治理:元数据管理实施(第四篇)

Continue to learn MySQL

Why use huluer pie disk instead of U disk?

Educational administration management system (free source code)

HCM 初学 ( 一 ) - 简介

Qt编译时,出现 first defined here,原因及解决方法

论文学习记录随笔 多标签之LIFT

Vscode function annotation / file header annotation shortcut

Wild melon or split melon?

论文学习记录随笔 多标签之GLOCAL

It's not that you have a bad mind, but that you haven't found the right tool

数据治理:数据治理管理(第五篇)

SystemVerilog学习-07-类的继承和包的使用