当前位置:网站首页>[quick start for Digital IC Validation] 26. Ahb - sramc (6) for system verilog project practice (Basic Points of APB Protocol)

[quick start for Digital IC Validation] 26. Ahb - sramc (6) for system verilog project practice (Basic Points of APB Protocol)

2022-07-07 15:20:00 【Lugant TCC】

Guide de lecture:L'auteur a eu le privilège d'être à l'avant - garde du domaine de l'information électronique en Chine“University of Electronic Science and Technology”Pendant les études supérieures,En contact avec le FrontNombreICValidation des connaissances,J'ai entendu des choses commeHuawei haisi、Tsinghua Purple light、Mediated Science and TechnologyCours en personne pour les principales entreprises de l'industrie liées aux circuits intégrés,Pour les chiffresICVérifier qu'il y a une certaine accumulation de connaissances et d'expériences d'apprentissage.Pour vous aider à démarrer le Front EndICAmis validés,Après avoir réfléchi un, deux,En particulier cette colonne,Dans l'espoir de prendre le plus de temps possible,Prenez le moins de virages possible,Le plus apprisICValidation des connaissances techniques.

Catalogue des articles

- Un.、Aperçu du contenu

- 2.、APB Aperçu du bus

- 2.1、APBAvecAHBComparer

- 2.2、APBIntroduction du signal

- 2.3、APBInterprétation du signal

- 2.4、APB Slave Décodage d'adresse

- 2.5、APB Schéma d'interconnexion

- 2.6、APB Séries chronologiques(Important)

- 2.7、APB Bridge

- 2.8、APB Bridge FSM(Machine d'état)

- 2.9、APB Slave Schéma de bloc(Signal d'interface,J'ai besoin de savoir dessiner.)

- 2.10、APB À AHB Conversion temporelle de - Lire

- Trois、C'est différent. IP L'interconnexion entre

- Quatre、AMBA Review

- Cinq、Résumé

Un.、Aperçu du contenu

- APBIntroduction du signal

- APBCalendrier de transmission

- AHBAvecAPB La différence entre la séquence temporelle et la séquence temporelle

- C'est différent.IPL'interconnexion entre

2.、APB Aperçu du bus

2.1、APBAvecAHBComparer

AHB Principalement utilisé dans les périphériques haute vitesse et haute performance ,EtAPB Est principalement utilisé pour monter des périphériques à basse vitesse .

InAPB La plupart des périphériques montés sont Slave,Non.Master, Périphérique qui reçoit passivement des données .

Compris AHBAprès le bus,ApprendreAPBC'est normal..C'est bon,Ne dis pas de bêtises, Entrée rapide dans le texte .

2.2、APBIntroduction du signal

| Nom du signal | Description du signal |

|---|---|

| PCLK | APBHorloge de bus |

| PRESETn | APBRéinitialiser |

| PADDR[31:0] | APBBus d'adresse |

| PSELx | APB SlaveSélectionner le signal |

| PENABLE | APB Signal d'activation |

| PWRITE | APB Direction de transmission du bus |

| PRDATA | APB Lire le bus de données |

| PWDATA | APB Écrivez le bus de données |

Note::APB Les signaux peuvent être combinés AHB Le signal comprend la mémoire .

2.3、APBInterprétation du signal

- PADDR[31:0]

- Bus d'adresse, Par le bus d'équipement bridge Entraînement de l'unit é

- PSELx

- Le signal du décodeur , Vers un périphérique esclave bus x

- PENABLE

- Utilisé pour effectuer tous les accès par étapes dans le temps sur le bus d'équipement

- PWRITE

- Haut niveau:Écris.

- Faible niveau:Lire

- PRDATAEtPWDATA

- La plupart32Largeur du BIT

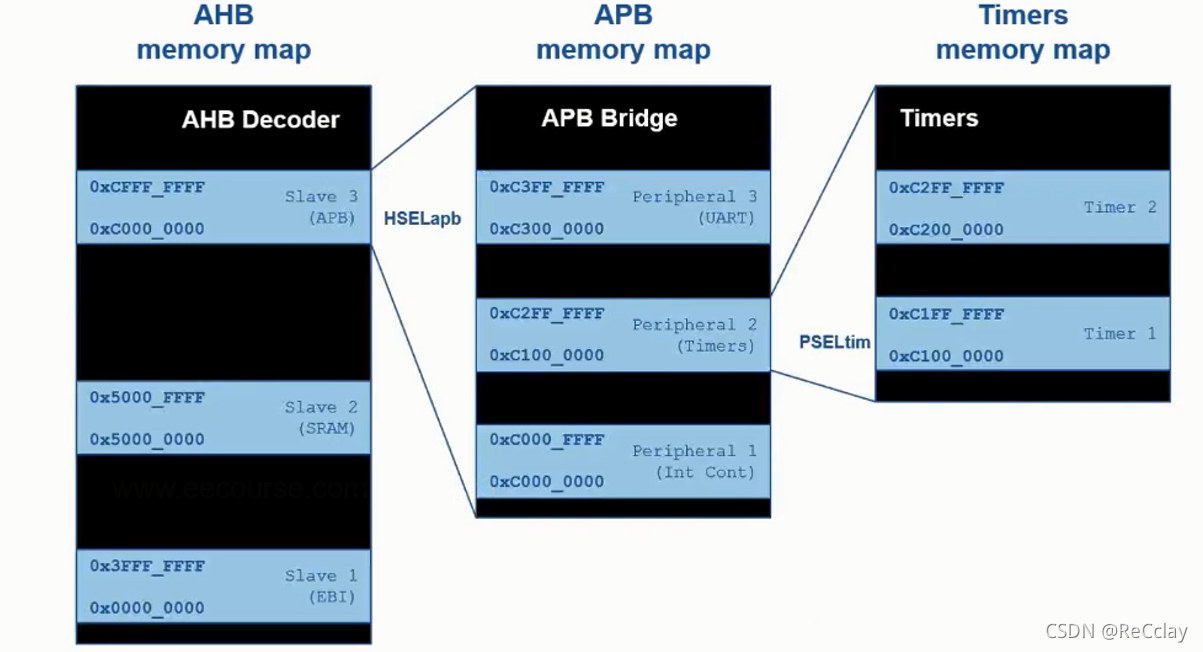

2.4、APB Slave Décodage d'adresse

- AHB-APB Bridge On peut l'interpréter comme AHB Slave

- La partie noire de l'image ci - dessus est Default Slave

- Le décodage des adresses est un niveau

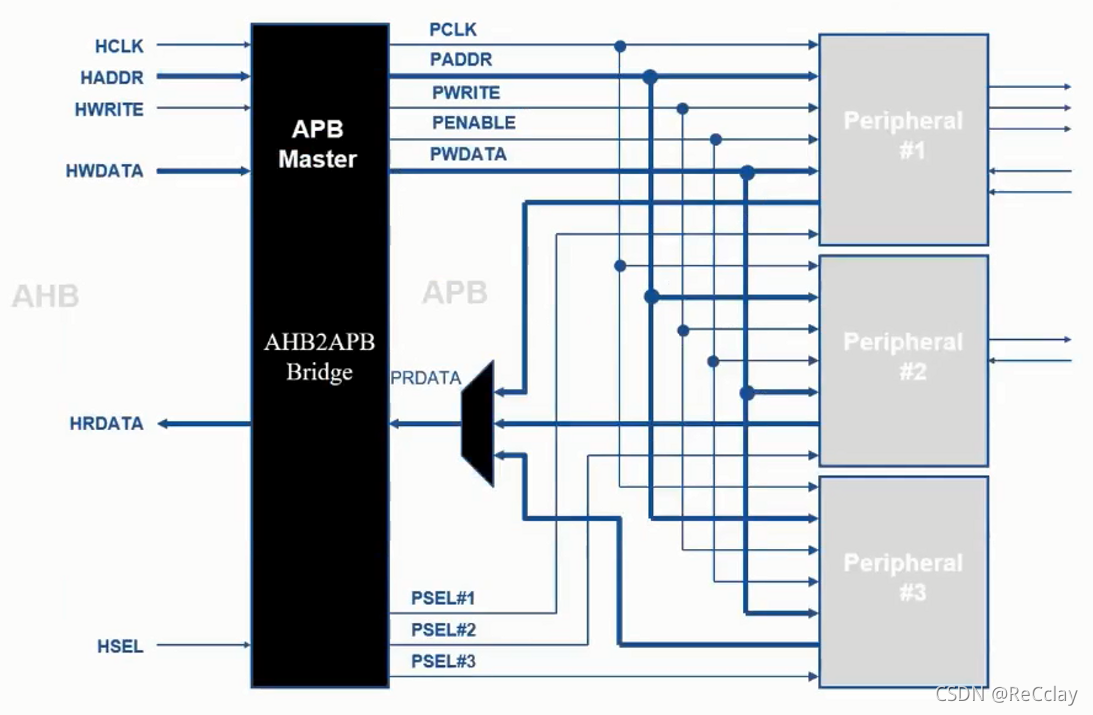

2.5、APB Schéma d'interconnexion

- Bridge La fonction est: AHB À APB Conversion temporelle de

2.6、APB Séries chronologiques(Important)

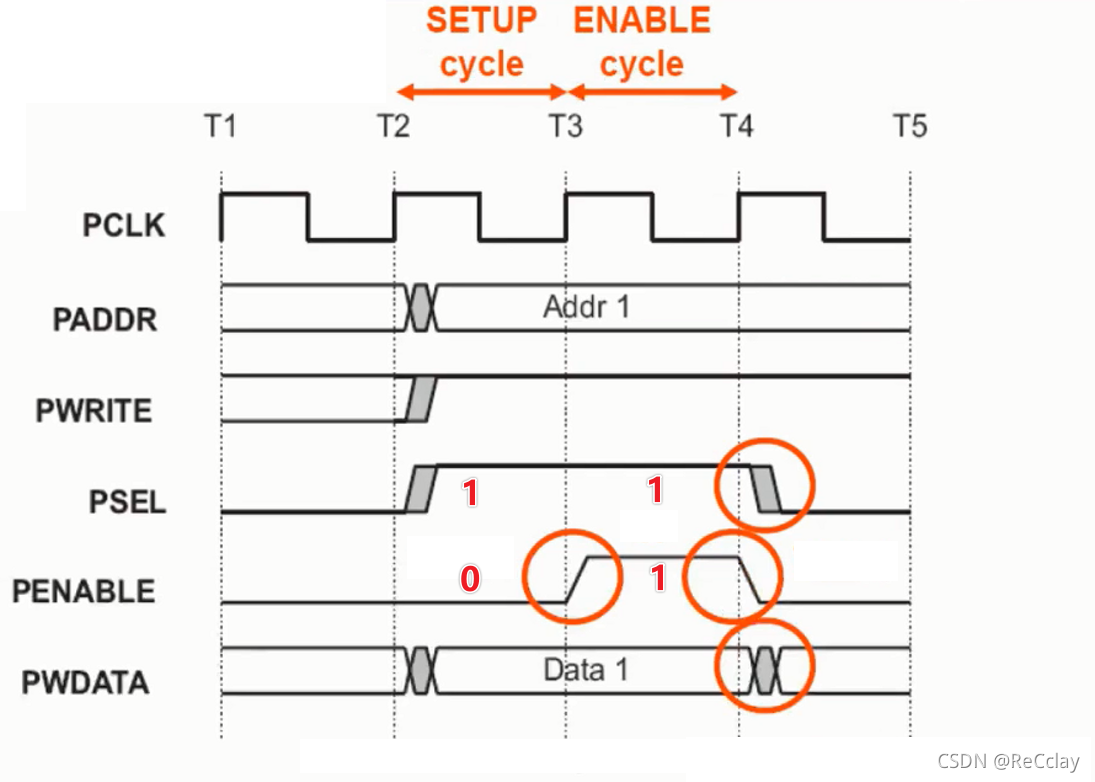

2.6.1、Écrire la transmission

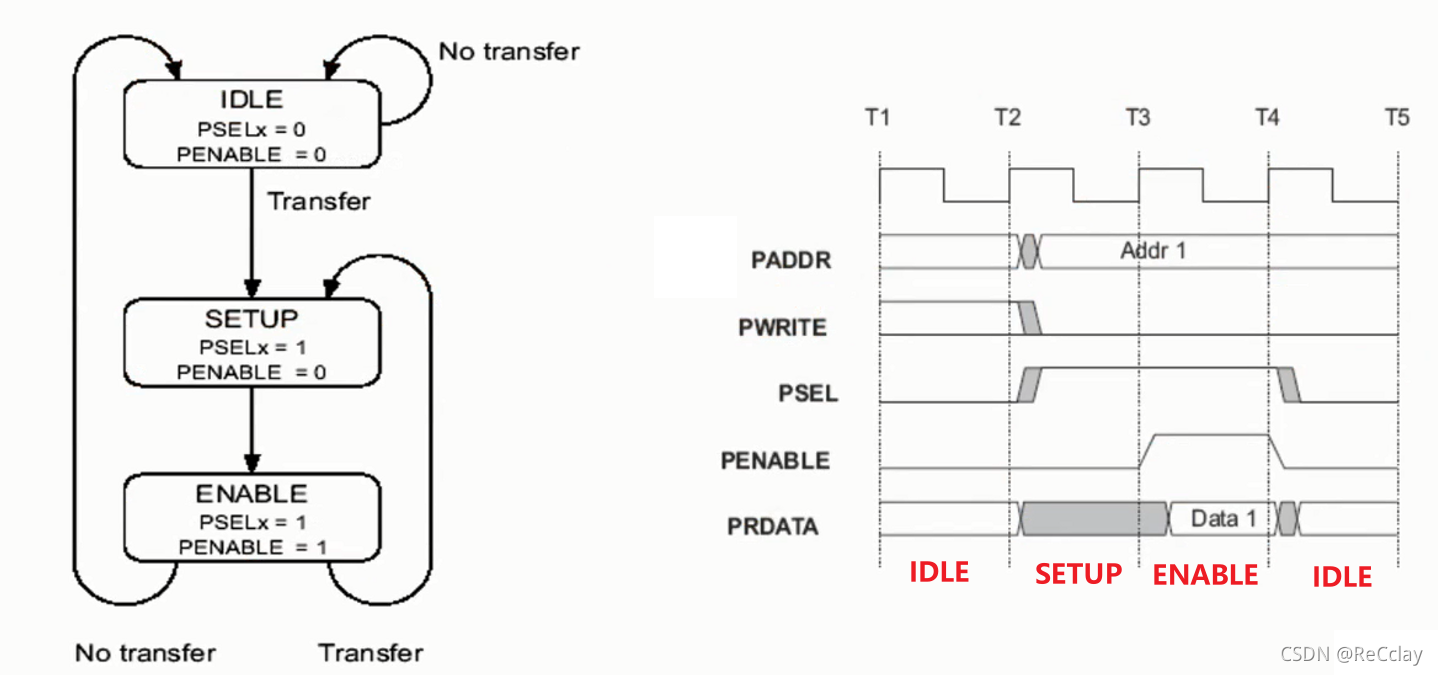

APB Relativement AHB Dis - le. Pas d'eau courante , Chaque commande est fixée Au moins 2 Cycles d'horlogeTerminé.!

- APBDivisé en deux étapes,Première phase- Oui.

SETUPPhase, Il n'y a qu'un seul cycle d'horloge .En ce momentPSELSignal élevé,PENABLELe signal est faible.Analogique AHB Phase de transfert d'adresse dans ! - La deuxième étape est

ENBALEPhase.En ce momentPSELSignal élevé,PENABLESignal élevé.Lire/ Écrire un signal de données valide ,Analogique AHB Phase de transmission des données dans !

- APBDivisé en deux étapes,Première phase- Oui.

La séquence ci - dessus est simplement AMBA 1.0/2.0Chronologie, La fixation n'est que de deux coups .Mise à jour versAMBA 3.0 Peut être utilisé après HREADYExtension

ENABLEPhase,EtSETUPC'est encore un cycle d'horloge .

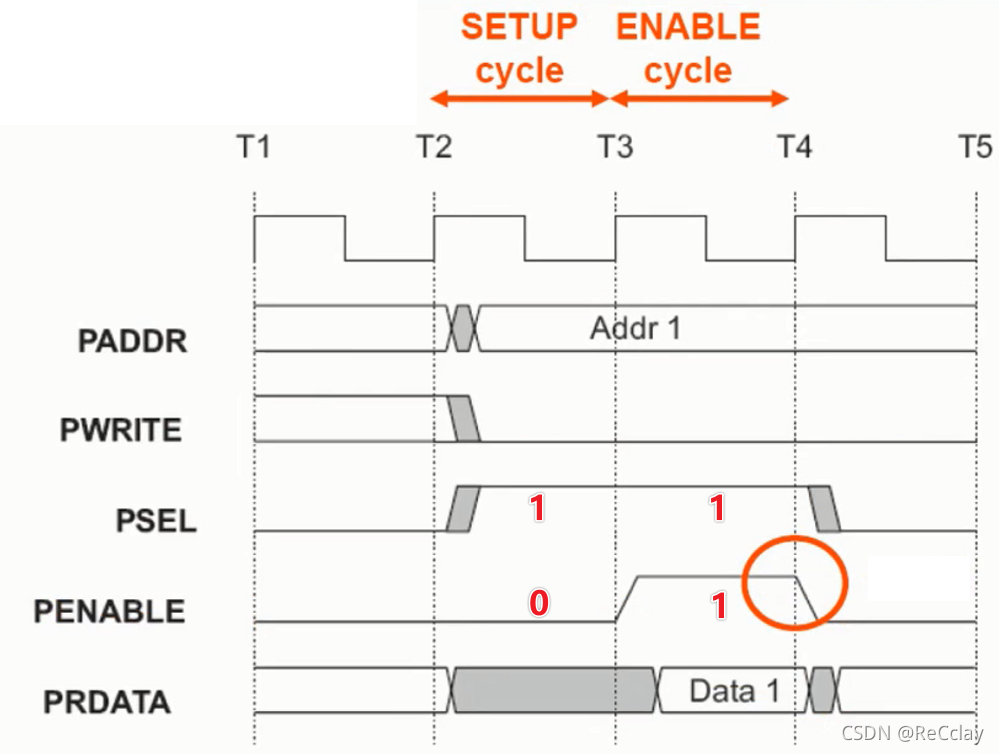

2.6.2、Lire la transmission

- La plus grande différence entre la lecture et l'écriture est

PWRITESignal, Le signal est maintenant faible . - La séquence ci - dessus est simplement AMBA 1.0/2.0Chronologie, La fixation n'est que de deux coups .Mise à jour versAMBA 3.0 Peut être utilisé après HREADYExtension

ENABLEPhase,EtSETUPC'est encore un cycle d'horloge .

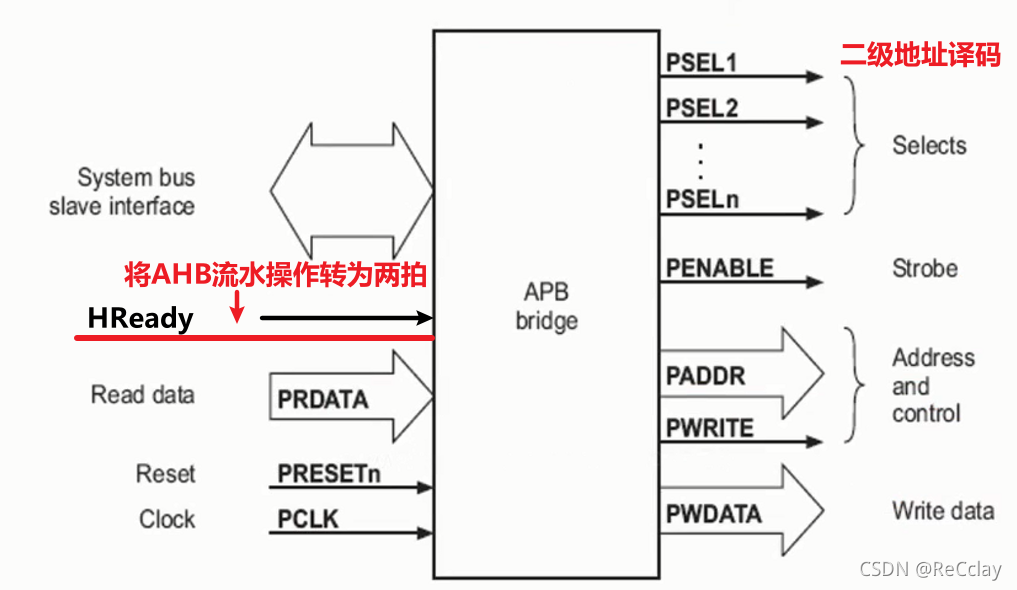

2.7、APB Bridge

- AHB C'est de l'eau courante ,PourBridgeDis - le., La fonction principale est de briser l'eau courante ,C'est - à - direAHB La séquence temporelle de APB,SiAHB Si c'est de l'eau courante ,Ça va passerBridgePour interrompre.!

- Principalement par

HREADYUn signal pour que l'eau coule en deux temps. .

- Principalement par

- APB Bridge Une autre fonction est de faire un décodage secondaire

2.8、APB Bridge FSM(Machine d'état)

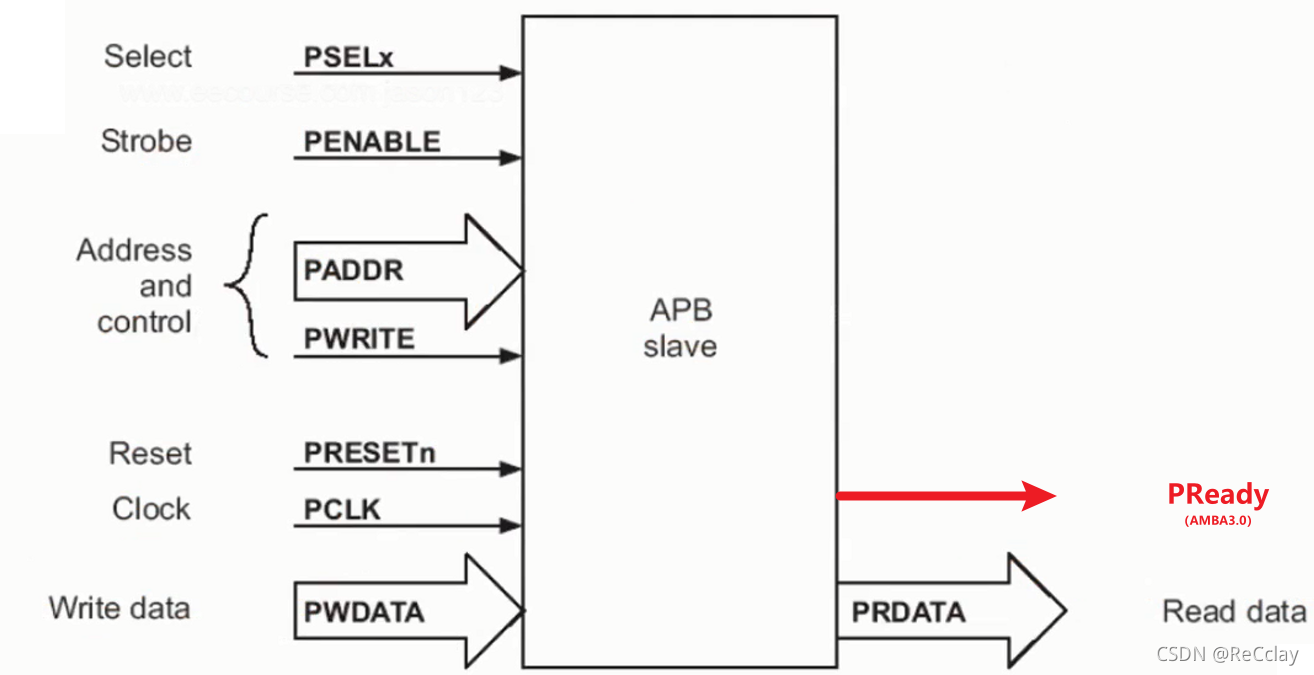

2.9、APB Slave Schéma de bloc(Signal d'interface,J'ai besoin de savoir dessiner.)

- Control Signal plus élevé AHB Beaucoup moins !

- ABMA 3.0 Soutien

PReadySignal Oh ~!

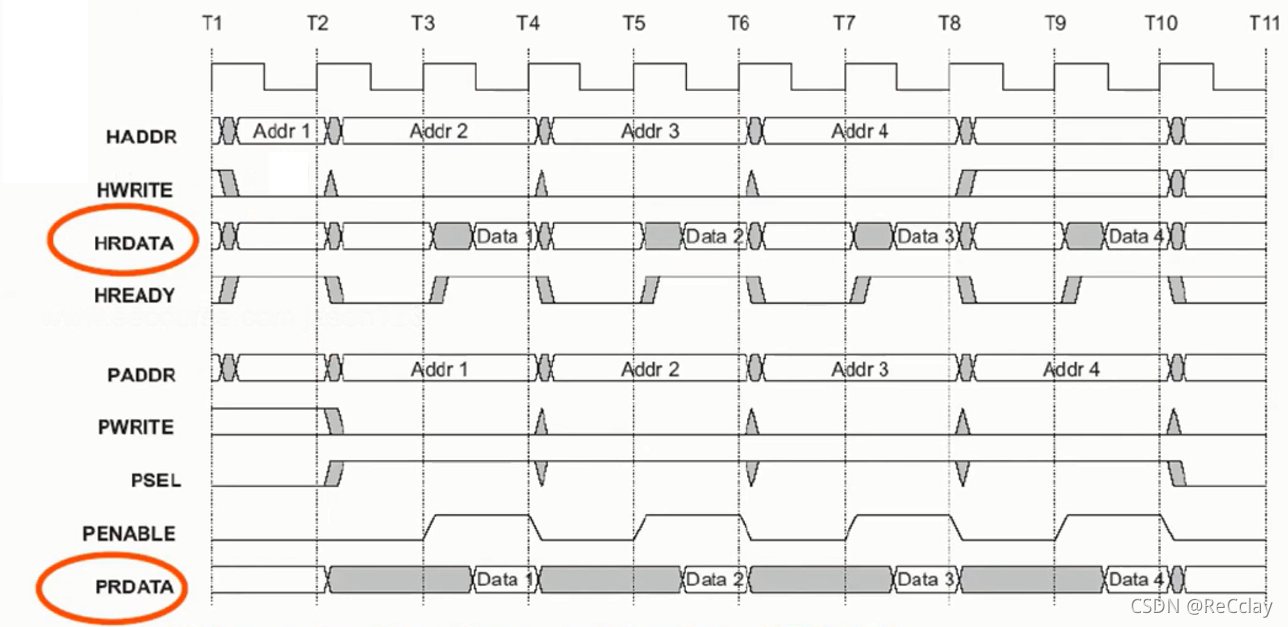

2.10、APB À AHB Conversion temporelle de - Lire

- L'image ci - dessus est AHB Lire APB Slave Fonctionnement séquentiel de,Vous pouvez voir à travers

HReadyLe signal interrompt le fonctionnement de l'eau couranteT1-T2EntreHREADYEst élevé,AdoptionHADDRTransmission du signal d'adresse ,AdoptionHWRITEFaible, Transmission du signal de commande de lecture .T2-T3EntreHREADYFaible,Excusez - moi.AHB Lecture de l'eau courante .En même temps,APBDePSELEst élevé,PENABLEFaible,APBEntréeSETUPPhase, Lire l'adresse et lire le signal de commande .T3-T4Entre,APBDePSELEst élevé,PENABLEEst élevé,APBEntréeENABLEPhase,AdoptionPRDATALireAPB SlaveDonnées.En même tempsHREADYEst élevé,Lire àAPB SlaveDonnées,Retour àHRDATA.- Jusqu'à ce que l'opération de lecture soit terminée .

PRDATAPeut être donné directement àHRDATA( Au même moment ),Si tu veuxHRDATASi tu frappes ,Ça pourrait être dansAPBENABLELa phaseHREADYBaissez.,Voilà.HRDATASera plus tard quePRADTAUn coup .

Trois、C'est différent. IP L'interconnexion entre

3.1、Mode de communication

- CPU (Master) < – > IP (Slave)

- IP(Master) < – > IP (Slave)

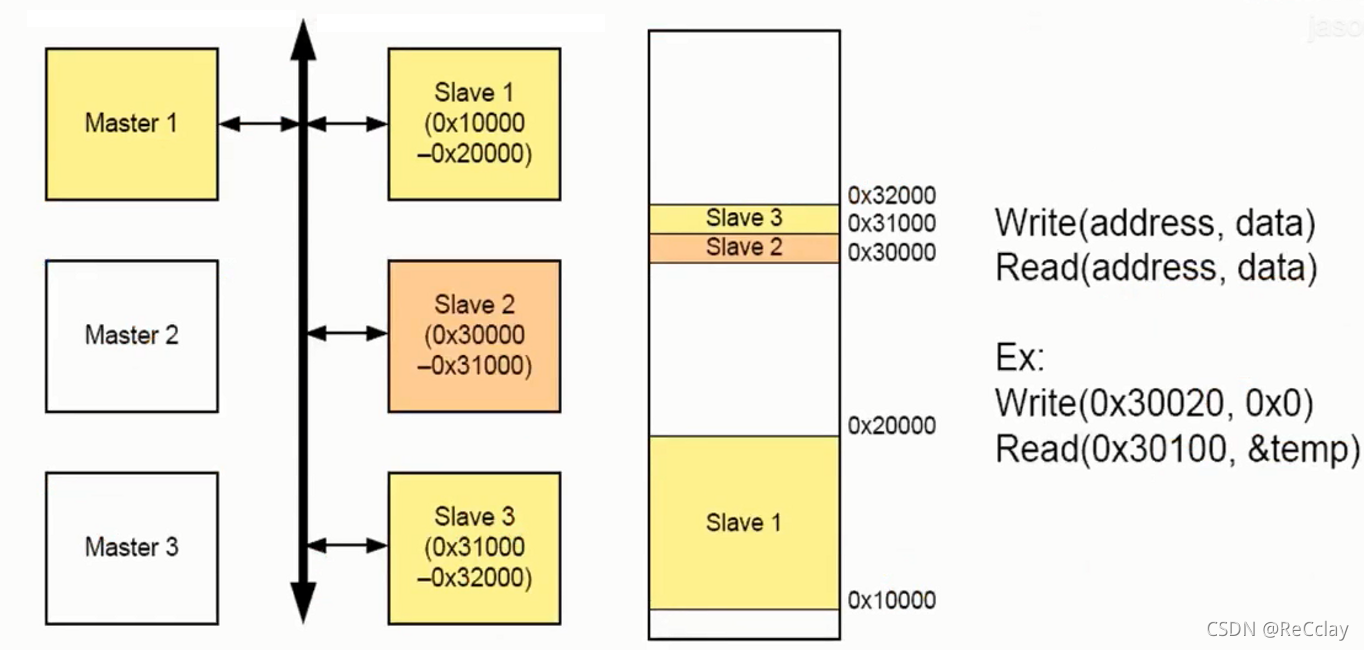

3.2、Memory Mapped IO

- Chaque esclave occupe une partie de l'espace d'adresse du système

- Tous les esclaves sont adressables

- Registres/ Le stockage est accessible en mode carte mémoire

- CPU/IP Lire et écrire autre IP Les données de

3.3、IP Interconnexion des communications entre

- L'équipement principal est arbiter grant Après, Accès à tous les périphériques esclaves sur le bus

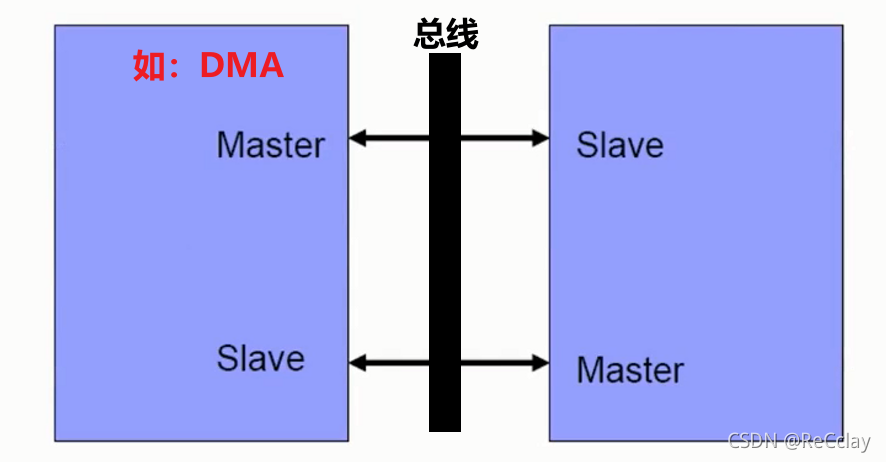

3.4、 UnIP Peut avoir à la fois des interfaces maître et esclave

- Master Lire et écrire des données

- Slave Configurer comme registre

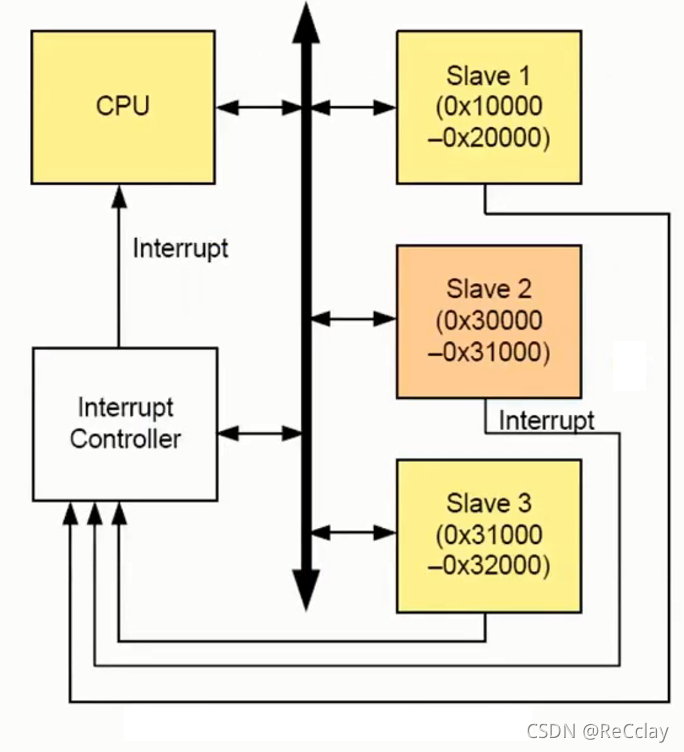

3.5、CPU Avec IP Communication entre

- CPU Toujours comme équipement principal

- IP Toujours comme esclave

- IP Une demande d'interruption peut être faite

- Seulement Slave InterfaceIP, Pour prendre l'initiative d'informer CPU Peut être interrompu

- Il ne doit pas y avoir trop d'informations à l'intérieur de l'interruption

- CPUEn mode interruption,Parinterrupt service routine(ISR)Pour gérer les interruptions

Quatre、AMBA Review

- AMBA Introduction

- AMBA2.0:AHB、ASB、APB

4.1、AHB

AHBLes composantes de

- AHB Master、AHB Slave、AHB Aribiter、AHB Decoder

AHB Signal

- HCLK、HRESETn、HADDR、HTRANS、HWRITE、HSIZE、HBURST、HWDATA、HSELx、HRDATA、HREADY、HRESP

AHB Les deux étapes de la transmission

- Période d'adresse 、Cycle de données

État actuel de la transmission HTRANS

- IDLE、BUST、NOSEQ、SEQ

Type de transmission d'éclatement HBURST(Compris.)

- SINGLE、INCR( Comment commencer une nouvelle INCRTransmission?)

- Burst Transmission impossible à traverser 1KFrontière

HSEL:ParAHB Decoder Par carte d'adresse

AHB Slave Signal de réponse

- HREADY Transmission terminée、HRESPTransmission de la réponse(OK、ERROR、RETRY)

- AHB Slave Pas de réponse pour une courte période (HREADY)? Pas de réponse depuis longtemps (HRESP)【 L'utilisation réelle ne peut pas définir ce qu'est un court laps de temps , Qu'est - ce qu'un long , Il n'y a donc pas beaucoup de !】

32 Octets valides pour le bus de données côté taille de bit

AHB Signal d'arbitrage (Compris.)

- HBUSREQ、HGRANT、HMASTER

- Équipement principalx Conditions dans lesquelles le bus peut être contrôlé

AHB Master、AHB Slave、AHB Arbiter、AHB DecoderSignal d'interface pour

AHB-Lite

4.2、APB

APBLes composantes de

- AHB2APB Bridge、APB Slave

APB Signal

- PCLK、PRESETn、PADDR、PSEL、PENABLE、PWRITE、PRDATA、PWDATA

APB Slave Carte d'adresse pour

APB Transmission(AMBA 1.0/2.0)

- Always two cycle transfer:Setup cycle、Enable Cycle

- No wait cycle and response signal(AMBA 3.0Oui, c'est vrai.)

APB Bridge Et APB SlaveSignal d'interface pour

Cinq、Résumé

Jusqu'ici. AMBA Dans l'AccordAPB La théorie des bus est terminée. ,APBPlusAHB La caractéristique la plus importante est qu'il n'y a pas de fonctionnement à l'eau courante ,EtAPBInAMBA 2.0Moyenne, L'exécution de la commande fixe deux cycles d'horloge . Ce n'est pas si difficile à trouver. ,APBEtAHB Beaucoup de signaux sont similaires ,EtAPBPlusAHB Il manque beaucoup de signaux de commande , Il suffit de comprendre AHB,APBC'est normal.. Nous passerons par AHB-SRAMCProjets opérationnels, Continuer à approfondir la compréhension AHBEtAPB.

PostScript:En raison de mon niveau limité,Les lacunes sont inévitables, Je vous prie de bien vouloir nous faire part de vos commentaires. . À propos des blogueurs 《NombreIC Valider le démarrage rapide 》Série d'articles,En ce momentCSDN Mise à jour en série ,Bienvenue à l'abonnement!

边栏推荐

- Compile advanced notes

- 【服务器数据恢复】戴尔某型号服务器raid故障的数据恢复案例

- 知否|两大风控最重要指标与客群好坏的关系分析

- Connecting FTP server tutorial

- Concurrency Control & NoSQL and new database

- Stream learning notes

- 大表delete删数据导致数据库异常解决

- HW初级流量监控,到底该怎么做

- [server data recovery] data recovery case of raid failure of a Dell server

- Spatiotemporal deformable convolution for compressed video quality enhancement (STDF)

猜你喜欢

![[data mining] visual pattern mining: hog feature + cosine similarity /k-means clustering](/img/a4/7320f5d266308f6003cc27964e49f3.png)

[data mining] visual pattern mining: hog feature + cosine similarity /k-means clustering

Bye, Dachang! I'm going to the factory today

Apache multiple component vulnerability disclosure (cve-2022-32533/cve-2022-33980/cve-2021-37839)

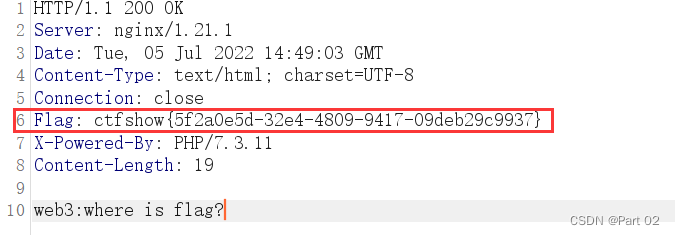

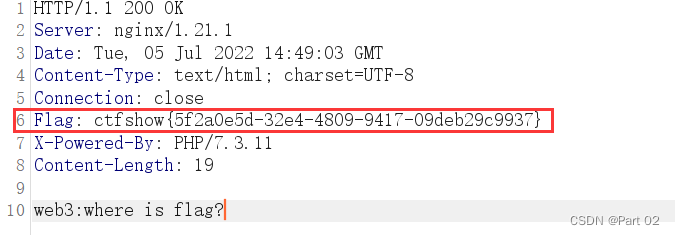

Ctfshow, information collection: Web3

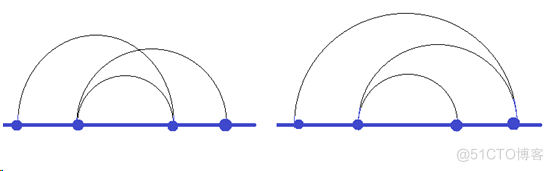

Yyds dry goods inventory # solve the real problem of famous enterprises: cross line

什么是数据泄露

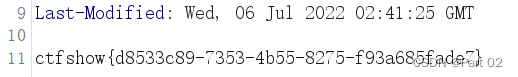

CTFshow,信息搜集:web9

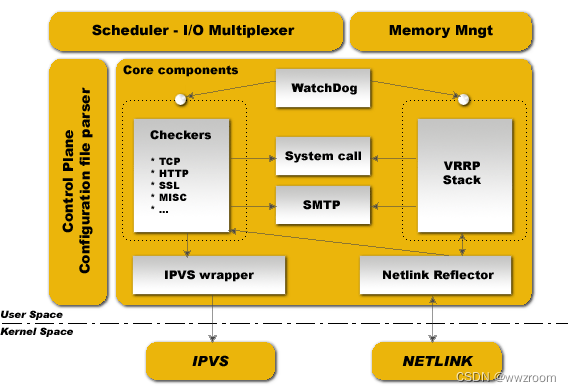

Briefly describe the working principle of kept

CTFshow,信息搜集:web3

银行需要搭建智能客服模块的中台能力,驱动全场景智能客服务升级

随机推荐

知否|两大风控最重要指标与客群好坏的关系分析

【服务器数据恢复】戴尔某型号服务器raid故障的数据恢复案例

leetcode 241. Different Ways to Add Parentheses 为运算表达式设计优先级(中等)

Ctfshow, information collection: web12

Notes HCIA

【原创】一切不谈考核的管理都是扯淡!

IDA pro逆向工具寻找socket server的IP和port

Comparable and comparator of sorting

2. Heap sort "hard to understand sort"

2. 堆排序『较难理解的排序』

Yyds dry goods inventory # solve the real problem of famous enterprises: cross line

Stm32f103c8t6 PWM drive steering gear (sg90)

Andriod --- JetPack :LiveData setValue 和 postValue 的区别

Ctfshow, information collection: web10

Ffmpeg --- image processing

Do you know the relationship between the most important indicators of two strong wind control and the quality of the customer base

Classification of regression tests

2022年5月互联网医疗领域月度观察

Novel Slot Detection: A Benchmark for Discovering Unknown Slot Types in the Dialogue System

【OBS】RTMPSockBuf_ Fill, remote host closed connection.