当前位置:网站首页>The design method of integral operation circuit is introduced in detail

The design method of integral operation circuit is introduced in detail

2022-07-27 15:16:00 【Desert fall】

This paper introduces the design of integral operation circuit .

Characteristic analysis of integral operation circuit

The figure below shows the basic inverse integral operation circuit with the integrated operational amplifier as the core component , Input voltage uI Via resistance R Add to the inverting input of the operational amplifier ,C Is the feedback capacitance , Introduce voltage parallel negative feedback ,R‘ To balance the resistance ,uO Is the output voltage .

Input signal uI Is the duty cycle q=50%、 The magnitude is ±Um、 The period is T The output signal is triangular waveform , The input and output signal waveforms are shown in the figure below .

The circuit principle is analyzed as follows . By ideal op amp's virtual short 、 The concept of virtual break and virtual ground of circuit , Establish the circuit equation

Solution (1) The general expression of the integral operation relationship is

Circuit time constant

When the integrating circuit enters the steady state , capacitance C The initial voltage on the is not zero , For convenience , On the circuit 0≤t≤T During the analysis and discussion of definite integral . stay 0~T/2 period , Input signal uI=UIm、 capacitance C The initial voltage on the is +UOm, By the type (2) Yes

By the type (7) You know , By choosing the time constant RC The numerical , It can make the amplitude of output voltage UOm And the amplitude of the input voltage is UOm>UIm、UOm=UIm And UOm<UIm3 One of the relationships . Because the maximum output voltage of the integrated operational amplifier is close to the power supply voltage ±VCC The finite value of , Therefore, the amplitude of the output voltage of the integral operation circuit UOm Satisfy

Input resistance of inverse integral operation circuit

To prevent integral saturation or cutoff caused by integral drift , Often a resistor is connected into the circuit RF( The figure below ).

Integral operation circuit to prevent integral saturation or cut-off

But access RF It will divert the charge and discharge current of the capacitor , This leads to integral error , To reduce the error , Generally, it should meet

Usually selected

Design of inverse integral operation circuit

Design of inverse integral operation circuit , It is known that the input duty cycle of the input terminal is 50% The frequency or period of a rectangular signal T、 amplitude ±UIm、 Amplitude of output voltage ±UOm And input resistance RI, determine RC Component parameters of integrating circuit . The design steps are :

By the type (8) Determine the time constant of the circuit , By the type (9) Determine the resistance R, Then solve the capacitance C The numerical .

Design examples : Design an inverse integral operation circuit , The frequency of the signal of the input rectangular wave is known f=1kHz、 amplitude UIm=±2V, Amplitude of output voltage UOm=±8V, Input resistance RI=10kΩ, Power supply voltage of operational amplifier ±VCC=±12V.

The design process is as follows .

UOm=±8V,±VCC=±12V, Satisfaction (9) Linear operating conditions .

By the type (8), The time constant of the circuit

Multisim10 The simulation software simulates, analyzes and verifies the designed inverse integral operation circuit [7,8], The simulation circuit constructed is shown in the figure below . Where the input signal uI Is the duty cycle q=50%、 amplitude UIm=±2V、 frequency f=1kHz( cycle T=0.001s) Rectangular wave , The dual trace oscilloscope is used to observe the input signal uI And the voltage at both ends of the capacitor uC Waveform of .

Integral operation simulation circuit

The simulation waveform is shown in the figure below , Among them, from top to bottom is the input rectangular wave signal uI、 Voltage at both ends of the capacitor uO Waveform of . Move the two cursor pointers to the voltage uO The peak of the waveform - Peak position , Peak of output voltage can be read - The peak value is 15.727V, Then the amplitude of the output voltage UOm=15.727V/2=7.8635V, Slightly smaller output voltage value of theoretical design , The capacitance can be appropriately reduced C The capacity of . From the figure 5 It can be seen that , The output voltage waveform is a triangular waveform with good linearity .

Simulation waveform of integral operation circuit

边栏推荐

- DevEco Studio2.1运行项目报错

- OBS advanced DXGI acquisition screen process, and how to modify it to its own cursor

- 谷歌团队推出新Transformer,优化全景分割方案|CVPR 2022

- 【云享读书会第13期】多媒体处理工具 FFmpeg 工具集

- TCC

- 3.3-5v转换

- Getting started with DirectX

- Internship: compilation of other configuration classes

- 网络设备硬核技术内幕 路由器篇 7 汤普金森漫游网络世界(下)

- ad7606与stm32连接电路介绍

猜你喜欢

谷歌团队推出新Transformer,优化全景分割方案|CVPR 2022

Principle of MOS tube to prevent reverse connection of power supply

Understand the evolution of redis architecture in one article

谷粒商城配置CorsWebFilter后,报错:Resource sharing error:MultipleAllowOriginValues

反射

Zhou Hongyi: if the digital security ability is backward, it will also be beaten

Do you really understand CMS garbage collector?

adb命令 (安装apk包格式:adb install 电脑上apk地址包名)

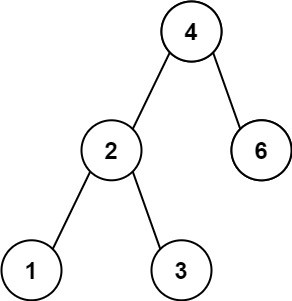

LeetCode 783. 二叉搜索树节点最小距离 树/easy

generic paradigm

随机推荐

Unity mouse controls the first person camera perspective

TCC

魔塔项目中的问题解决

微信小程序实现音乐搜索页面

STM32 can -- can ID filter analysis

网络设备硬核技术内幕 路由器篇 21 可重构的路由器

网络设备硬核技术内幕 路由器篇 17 DPDK及其前传(二)

网络设备硬核技术内幕 路由器篇 6 汤普金森漫游网络世界(中)

Hdu3117 Fibonacci numbers [mathematics]

The mobile terminal uses the list component of vantui. When multiple tab items are switched back and forth, the list is loaded many times, resulting in the failure of normal display of data

Unity3D学习笔记10——纹理数组

光电隔离电路设计方案(六款基于光耦、AD210AN的光电隔离电路图)

谷歌团队推出新Transformer,优化全景分割方案|CVPR 2022

DIY制作示波器的超详细教程:(一)我不是为了做一个示波器

仅做两项修改,苹果就让StyleGANv2获得了3D生成能力

网络设备硬核技术内幕 路由器篇 15 从鹿由器到路由器 (下)

网络设备硬核技术内幕 路由器篇 20 DPDK (五)

周鸿祎:数字安全能力落后也会挨打

Sword finger offer cut rope

《剑指Offer》剪绳子