当前位置:网站首页>Understand Chisel language. 31. Chisel advanced communication state machine (3) - Ready-Valid interface: definition, timing and implementation in Chisel

Understand Chisel language. 31. Chisel advanced communication state machine (3) - Ready-Valid interface: definition, timing and implementation in Chisel

2022-08-02 07:55:00 【github-3rr0r】

Chisel进阶之通信状态机(三)——Ready-Valid接口:定义、时序和Chisel中的实现

上一篇文章以Popcount为例,介绍了带数据通路的有限状态机FSMD的写法与实现,对于后面写复杂的系统有很关键的指导意义.我们可以注意到,在FSMD的实现中,状态机之间的通信我们使用了Ready-Valid握手协议,这是一种常见的通信接口协议,但每次都这么写显然有点复杂.而Chisel中自带了Ready-Valid相关的函数DecoupledIO,用于对数据信号进行Ready-Valid协议的封装,In this article, we will learn about this important and convenient function.

Ready-Valid接口

Communication between subsystems can be generalized as 数据的移动和Handshake for flow control.在上一篇文章的Popcount例子中,We have already seen a handshake interface for inputting and outputting data,This interface is usedReady-Valid信号.

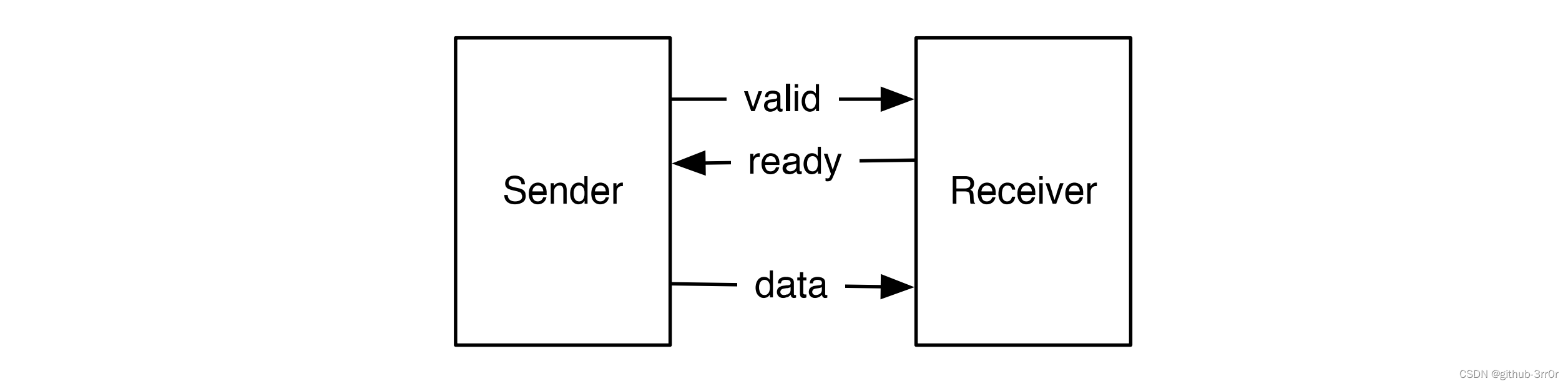

Ready-ValidAn interface is a simple control flow interface,包含:

data:The data sent by the sender to the receiver;valid:Signal from sender to receiver,Used to indicate whether the sent data is valid;ready:Signal from receiver to sender,Used to indicate whether data can be received;

下面是Ready-ValidSchematic diagram of flow control:

发送端在dataIt will be set when readyvalid信号,The receiver is set when it is ready to receive a word of dataready信号.The transmission of data will be in two signals,valid信号和ready信号,It will only be done when both are set.If either of the two signals is not set,Then there will be no data transfer.

Ready-ValidTiming of interface data transfer

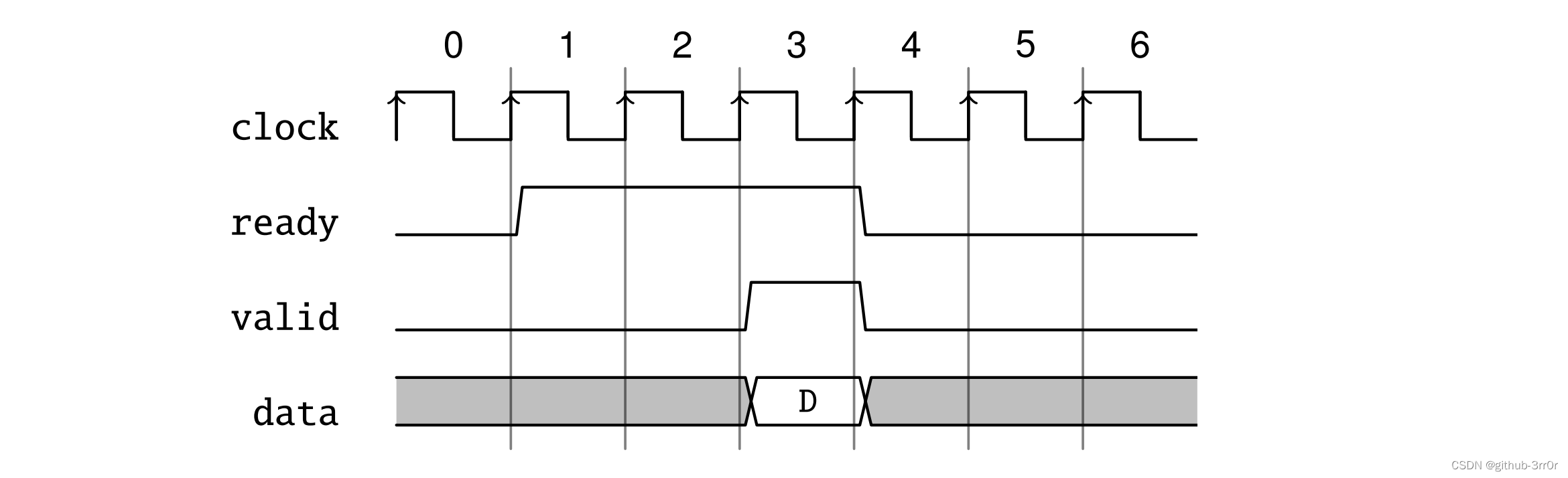

The figure below is when the receiver is ready with the data before the sender,就将readywhen set to valid(from the first clock cycle)的时序图:

上图中,Data is ready on the third clock cycle,同时valid置有效,此时ready信号和validsignals are all set,Data transfer takes place.And in the fourth clock cycle,The sender has no data to send,The receiver is also not ready to accept the data.If the receiver can accept data every clock cycle,that's calledalways ready接口,readyThe signal can be hard-coded as true.

The figure below is when the sender is ready to receive data at the receiver,就将validwhen the signal is set(from the first clock cycle)的时序图:

Data transfer occurs on the third clock cycle,Also from the fourth clock cycle,The sender has no data to send,The receiver is also not ready to accept the data.类比always ready接口,We can think of whether there is onealways valid接口.确实,However, in this case the data may be givenreadySignal time does not change,We can simply discard this handshake.

下图是Ready-ValidTiming diagram for another variation of the interface:

上图中,在第一个时钟周期,ready和validis set for one clock cycle at the same time,数据D1The transmission is also carried out in this cycle.数据可以背靠背传输(每个时钟周期内),such as the fourth、within the fifth clock cycleD2和D3的传输.(注意,这里的背靠背means twice in a row,常用于NBA)

Chisel中的Ready-Valid接口

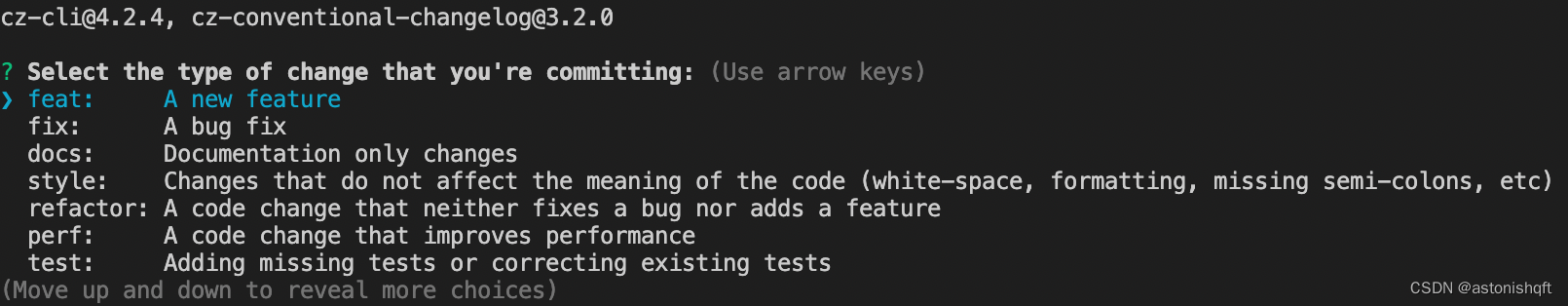

in order to let both modules passReady-Valid接口连接,必须要保证ready和validNeither depend on each other.Because this interface is so common,所以Chisel里面定义了DecoupledIO,Definition like this:

class DecoupledIO[T <: Data](gen: T) extends Bundle {

val ready = Input(Bool())

val valid = Output(Bool())

val bits = Output(gen)

}

Importing is required to use itutil包.这个DecoupledIO根据数据dataThe type to parameterize,用DecoupledIO封装后,through the interfacebitsfield to accessdata.

当然了,显然这个DecoupledIOThe interface is the sender,The interface on the receiving end is completely reversed,那么我们就需要使用Chisel中的另一个函数Flipped了.Flipped函数可以将一个BundleThe input and output are all reversed,So if a sender'sReady-ValidThe data interface is defined as follows:

val out = DecoupledIO(UInt(8.W))

Then on the receiving endReady-ValidThe data interface is set outside when it is definedFlipped就行了:

val in = Flipped(DecoupledIO(UInt(8.W)))

There may still be such a problem,ready和validThe signal is possible after being set、Cancel the setting again without data being transferred.比如说,possible on the receiving endready了一些时间,But no data was received,It was cancelled again due to some other eventsready;Another example is that the sender may have data ready,valid了一段时间,But canceled again without sending datavalid.Regardless of whether this behavior is allowed or not,这不是Ready-ValidWhat the interface is about to discuss,But this needs to be defined by the concrete usage of the interface.

Chisel中使用DecoupledIO的时候,对ready和validThe setting of the signal is not required.但是,Chisel中的IrrevocableIOThe class imposes the following restrictions on the sender:

IrrevocableIO是ReadyValidIO的一个具体子类,当valid为1,ready为0时,能够保证bits的值不改变.也就是说,一旦valid为1后,他就不会变为0,直到ready也变为1.

需要注意的是,这只是一个约定,and cannot be usedIrrevocableIOclass to enforce the specification(IrrevocableMeans irrevocable).

而AXIThe protocol is used for every part of the busReady-Valid接口,Including the read address、读数据、Write address and write data.AXIThe protocol restricts the interface onceready或valid被设置,It is not allowed to cancel the setting until the data has been transferredready或valid了.

结语

The communication state machine part ends here,This article is used in the previous articleReady-ValidThe interface is described in detail,on timing andChisel中提供的DecoupledIOInterfaces are also analyzed.复杂的、The communication of various modules in a large digital circuit can be generalized as a communication state machine,So the communication interface is also very important.到目前为止,ChiselThe related content has basically ended,但是ChiselThe most powerful feature of , which we have not yet studied in detail,That is as a hardware generator.下一部分,我们将从Scala开始,详细说说ChiselWritten as a hardware generator,Allows us to write parameterized hardware circuits,Great for reusability.

边栏推荐

- Hack The Box - File Transfers Module详细讲解中文教程

- 带手续费买卖股票的最大利益[找DP的状态定义到底缺什么?]

- (2022 Niu Ke Duo School 5) B-Watches (two points)

- Splunk Filed extraction field interception

- 吃透Chisel语言.30.Chisel进阶之通信状态机(二)——FSMD:以Popcount为例

- 【机器学习】实验6布置:基于集成学习的Amazon用户评论质量预测

- 企业实训复现指导手册——基于华为ModelArts平台的OpenPose模型的训练和推理、基于关键点数据实现对攀爬和翻越护栏两种行为的识别、并完成在图片中只标注发生行为的人

- Metasploit(MSF)基础超级详细版

- 2022年数据泄露平均成本高达435万美元,创历史新高!

- 【ROS基础】rosbag 的使用方法

猜你喜欢

![MySQL报错1055解决办法:[Err] 1055 - Expression #1 of ORDER BY clause is not in GROUP BY clause and contains](/img/aa/ab58ec47bb96df803dbc6a8ff6dde3.png)

MySQL报错1055解决办法:[Err] 1055 - Expression #1 of ORDER BY clause is not in GROUP BY clause and contains

pnpm + workspace + changesets 构建你的 monorepo 工程

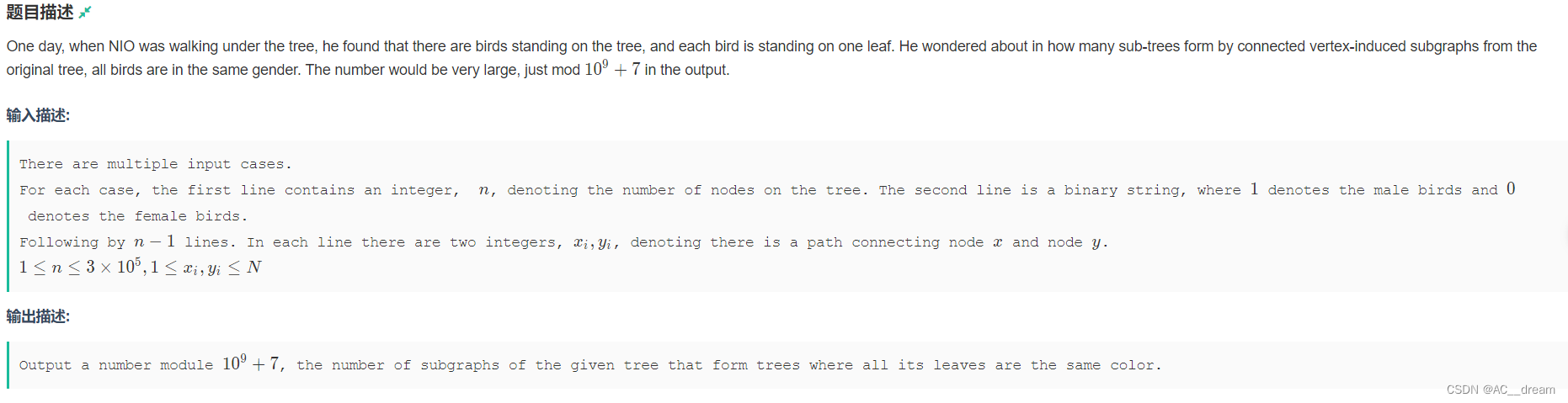

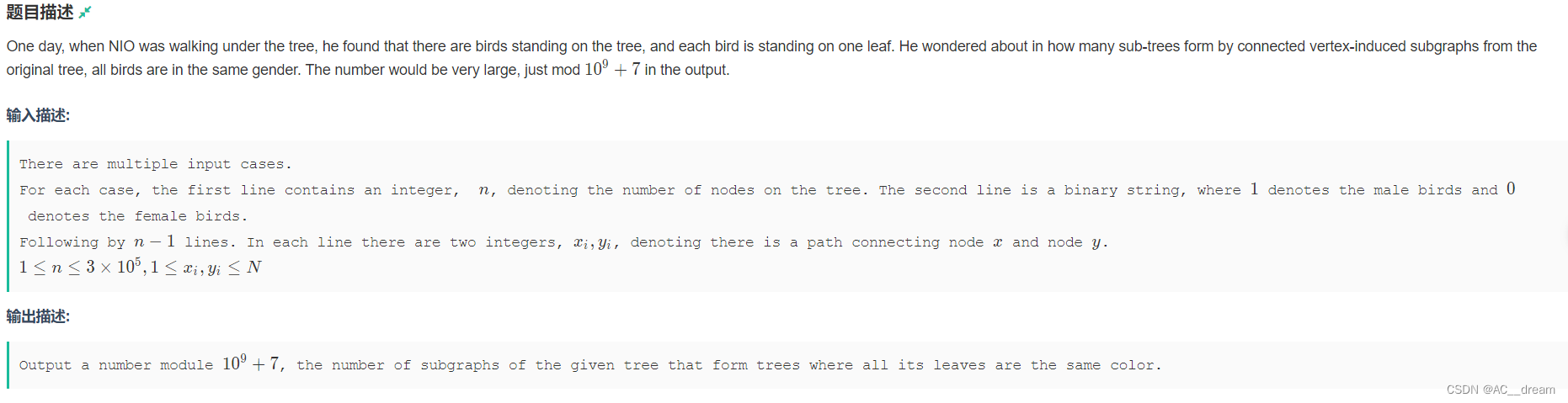

(2022 Niu Ke Duo School 5) D-Birds in the tree (tree DP)

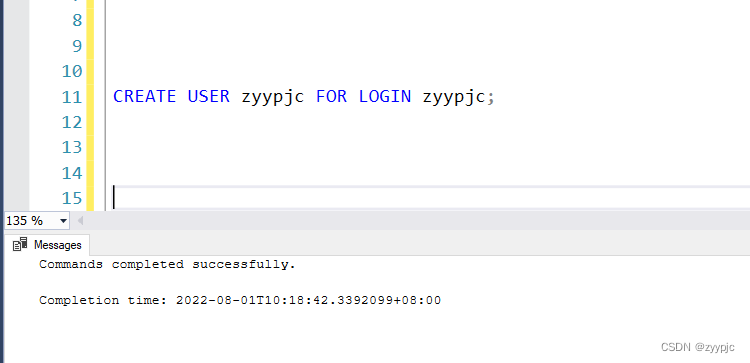

Azure Synapse Analytics上创建用户并赋予权限

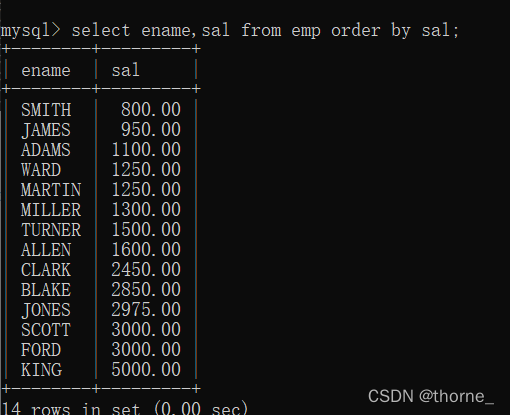

mysql操作入门(四)-----数据排序(升序、降序、多字段排序)

【CV】OpenVINO installation tutorial

(2022牛客多校五)D-Birds in the tree(树形DP)

研发创新编码器霍尔板,引领企业高质量发展

神经元网络

Xilinx约束学习笔记—— 时序约束

随机推荐

spark读取文件夹数据

OC-NSNumber和NSValue一般用来装箱拆箱

gdalinfo: error while loading shared libraries: libgdal.so.30: cannot open shared object file: No su

图腾柱和推挽电路介绍

2022年数据泄露平均成本高达435万美元,创历史新高!

LeetCode刷题(7)

【网络】IP、子网掩码

自然语言处理 文本预处理(上)(分词、词性标注、命名实体识别等)

(2022牛客多校五)D-Birds in the tree(树形DP)

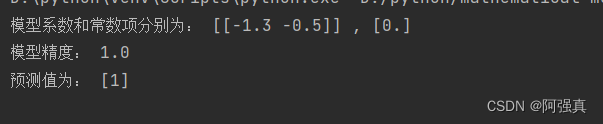

【机器学习】课程设计布置:某闯关类手游用户流失预测

Splunk Field Caculated Calculated Field

常用的云安全防护措施盘点

【CV】OpenVINO installation tutorial

MySQL-Multiversion Concurrency Control

责任链模式(Chain Of Responsibility)

Introduction to Totem Pole and Push-Pull Circuits

Hack The Box - File Transfers Module详细讲解中文教程

PLSQL Developer安装和配置

(2022牛客多校五)C-Bit Transmission(思维)

Debian 10 dhcp relay (dhcp 中继) dhcp 固定分配