当前位置:网站首页>门级建模—课后习题

门级建模—课后习题

2022-07-01 23:21:00 【江南小作坊】

习题

利用双输入端的nand门,用Verilog编写自己的与或非门,并用激励模块验证这些门的功能。

与门,verilog实现,用三个与非门

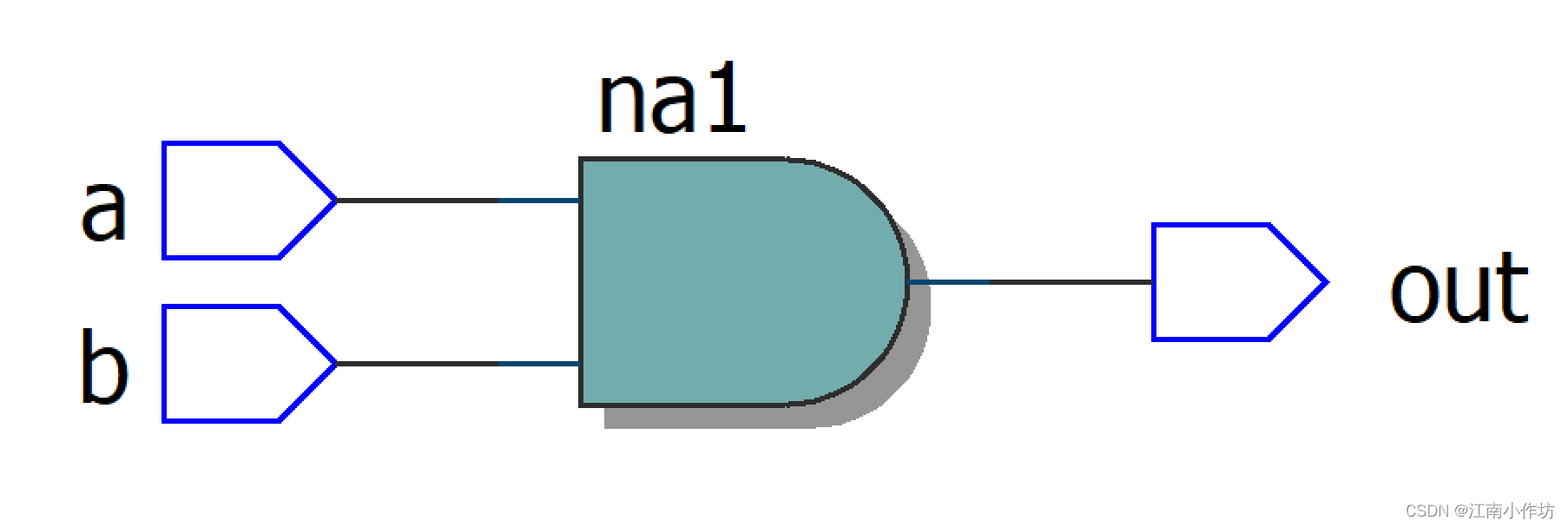

module my_add( output out, input a, input b ); wire w1,w2; nand na1(w1,a,b); nand na2(w2,a,b); nand na3(out,w1,w2); endmoduleRTL视图

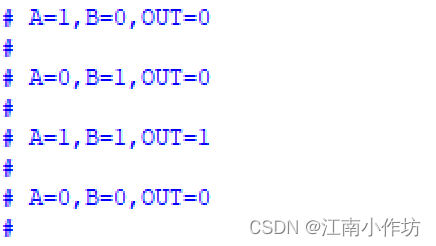

仿真实现

仿真结果满足与门逻辑。

与门(第二种方式),Verilog实现,两个与非门

module my_and( output out, input a, input b ); wire w1; nand na1(w1,a,b); nand na2(out,w1,w1); endmoduleRTL视图

仿真结果

或门,verilog实现

//构建或门 module my_or( output out, input a, input b ); //输入短接 wire w1,w2; nand (w1,a,a); nand (w2,b,b); nand (out,w1,w2); endmodule仿真验证

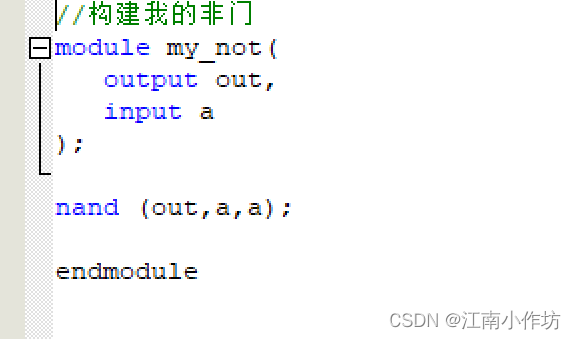

非门,就很简单啦,把与非门输入短接就行啦,就不一一验证了。本来不想写my_not的,结果第二题要用到,贴上其代码。

利用上题所定义的my_and,my_or,my_not,来构建一个异或门(xor),功能计算 z = x ˉ y + x y ˉ z=\bar{x}y+x\bar{y} z=xˉy+xyˉ,编写仿真信号对其测试。

verilog实现

//综合my_and,my_or,my_not module my_xor( output out, input a, input b ); //声明内部线网 wire w1,w2,w3,w4; my_not my_not_1(w1,a); my_not my_not_2(w2,b); my_and my_and_1(w3,w1,b); my_and my_and_2(w4,w2,a); my_or my_or_1(out,w3,w4); endmoduleRTL视图

仿真设计

// 仿真定义 module my_xor_tb(); reg x,y; wire z; my_xor my_xor_inst(z,x,y); initial begin x=1'b0; y=1'b1; #10 x=1'b0; y=1'b0; #1 $display("x=%b,y=%b,z=%b\n",x,y,z); #10 x=1'b0; y=1'b1; #1 $display("x=%b,y=%b,z=%b\n",x,y,z); #10 x=1'b1; y=1'b0; #1 $display("x=%b,y=%b,z=%b\n",x,y,z); #10 x=1'b1; y=1'b1; #1 $display("x=%b,y=%b,z=%b\n",x,y,z); end endmodule仿真结果,满足异或门逻辑

懒得打字拉,题目如下

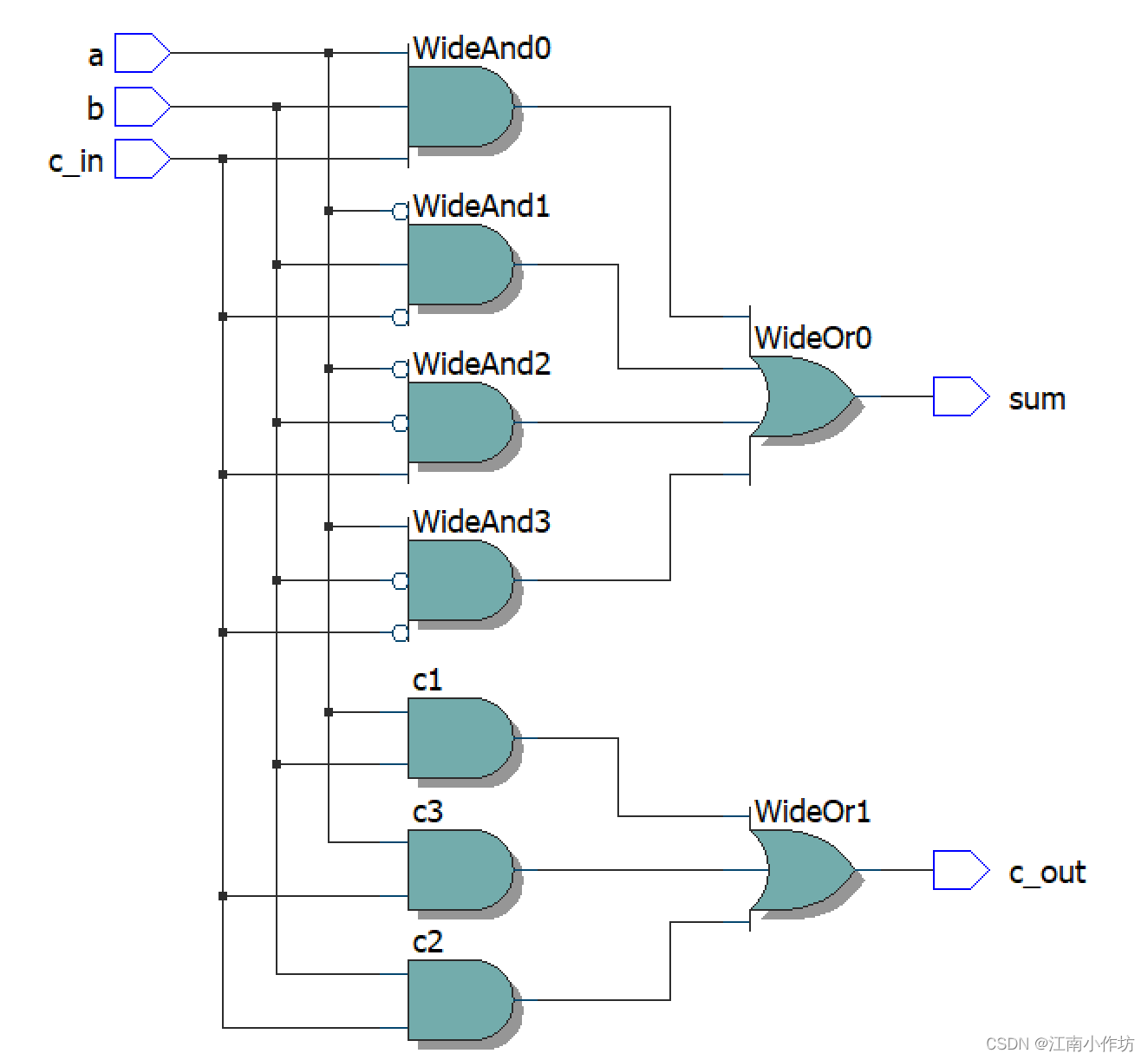

Verilog实现

module my_fulladder( output sum, output c_out, input a, input b, input c_in ); wire a_1, b_1, c_in_1; wire s1, s2, s3, s4; wire c1, c2, c3; // 先实现等式中的非门,且用上面定义的线网连接 not (a_1, a); not (b_1, b); not (c_in_1, c_in); // 实现等式中的sum and (s1,a,b,c_in); and (s2,a_1,b,c_in_1); and (s3,a_1,b_1,c_in); and (s4,a,b_1,c_in_1); or (sum,s1,s2,s3,s4); // 实现等式中的c_out and (c1,a,b); and (c2,b,c_in); and (c3,a,c_in); or (c_out,c1,c2,c3); endmoduleRTL视图

仿真实现

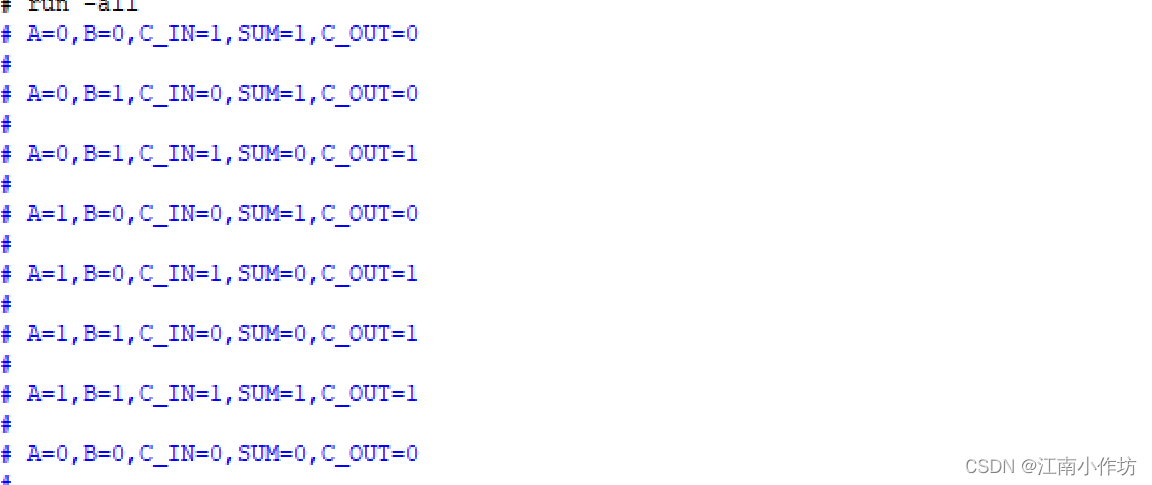

module my_fulladder_tb(); reg A,B,C_IN; wire C_OUT,SUM; my_fulladder my_fulladder_inst(SUM, C_OUT, A, B, C_IN); initial begin A = 1'b0; B = 1'b0; C_IN = 1'b0; #10 A = 1'b0; B = 1'b0; C_IN = 1'b1; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b0; B = 1'b1; C_IN = 1'b0; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b0; B = 1'b1; C_IN = 1'b1; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b1; B = 1'b0; C_IN = 1'b0; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b1; B = 1'b0; C_IN = 1'b1; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b1; B = 1'b1; C_IN = 1'b0; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b1; B = 1'b1; C_IN = 1'b1; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b0; B = 1'b0; C_IN = 1'b0; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); end endmodule仿真结果,满足设计要求

直接上图

verilog实现

module my_rs_latch( output q, output qbar, input set, input reset ); nor #(1) (q,reset,qbar); nor #(1) (qbar,q,set); endmodule仿真

module my_rs_latch_tb(); reg SET,RESET; wire Q,QBAR; my_rs_latch my_rs_latch_inst(Q,QBAR,SET,RESET); initial begin SET=1'b0; RESET = 1'b0; #10 SET=1'b0; RESET = 1'b1; #10 SET=1'b1; RESET = 1'b0; #10 SET=1'b1; RESET = 1'b1; end endmodule仿真结果,经过两个时间单位(2 ps),q发生改变

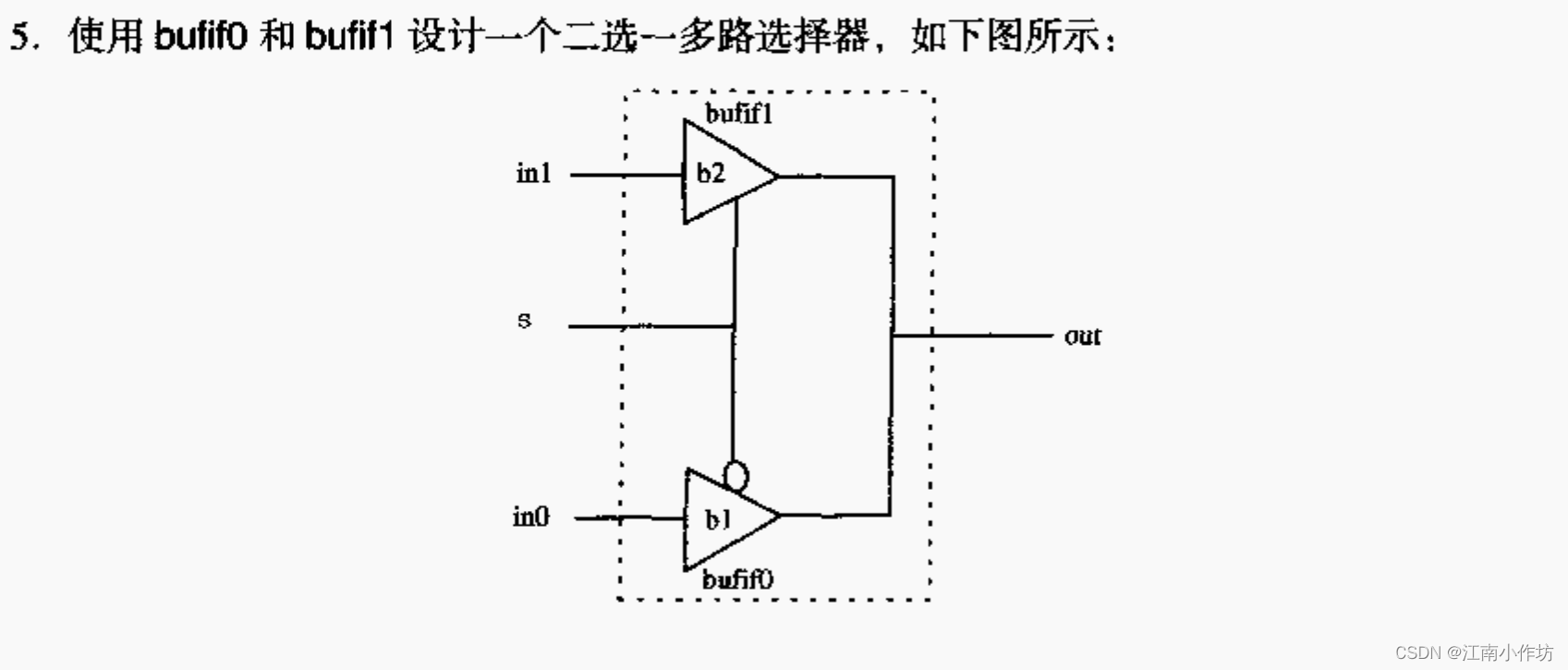

上图

此多路选择器,当s为1的时候,输出in1;s为0的时候,输出in2。

verilog实现

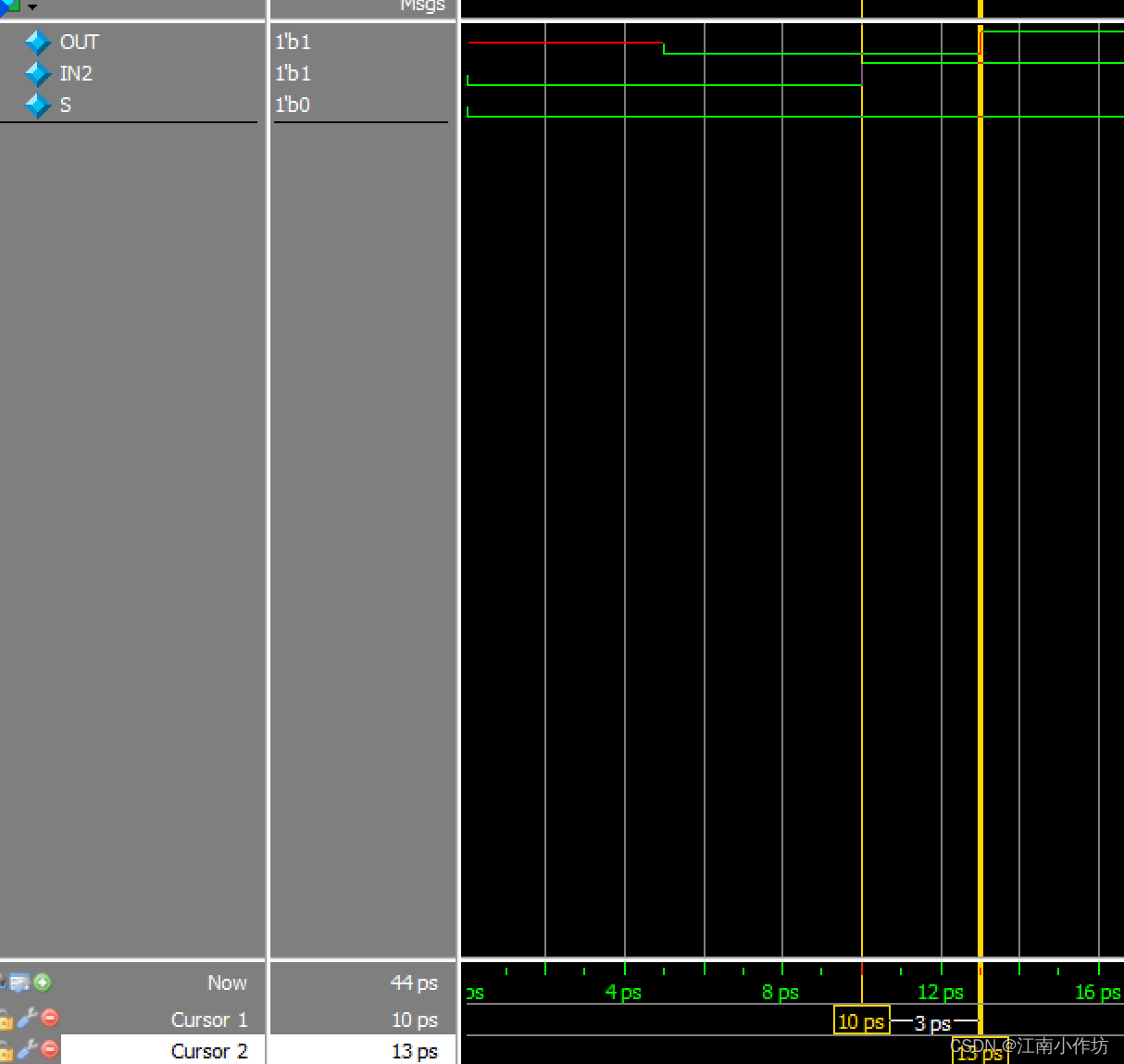

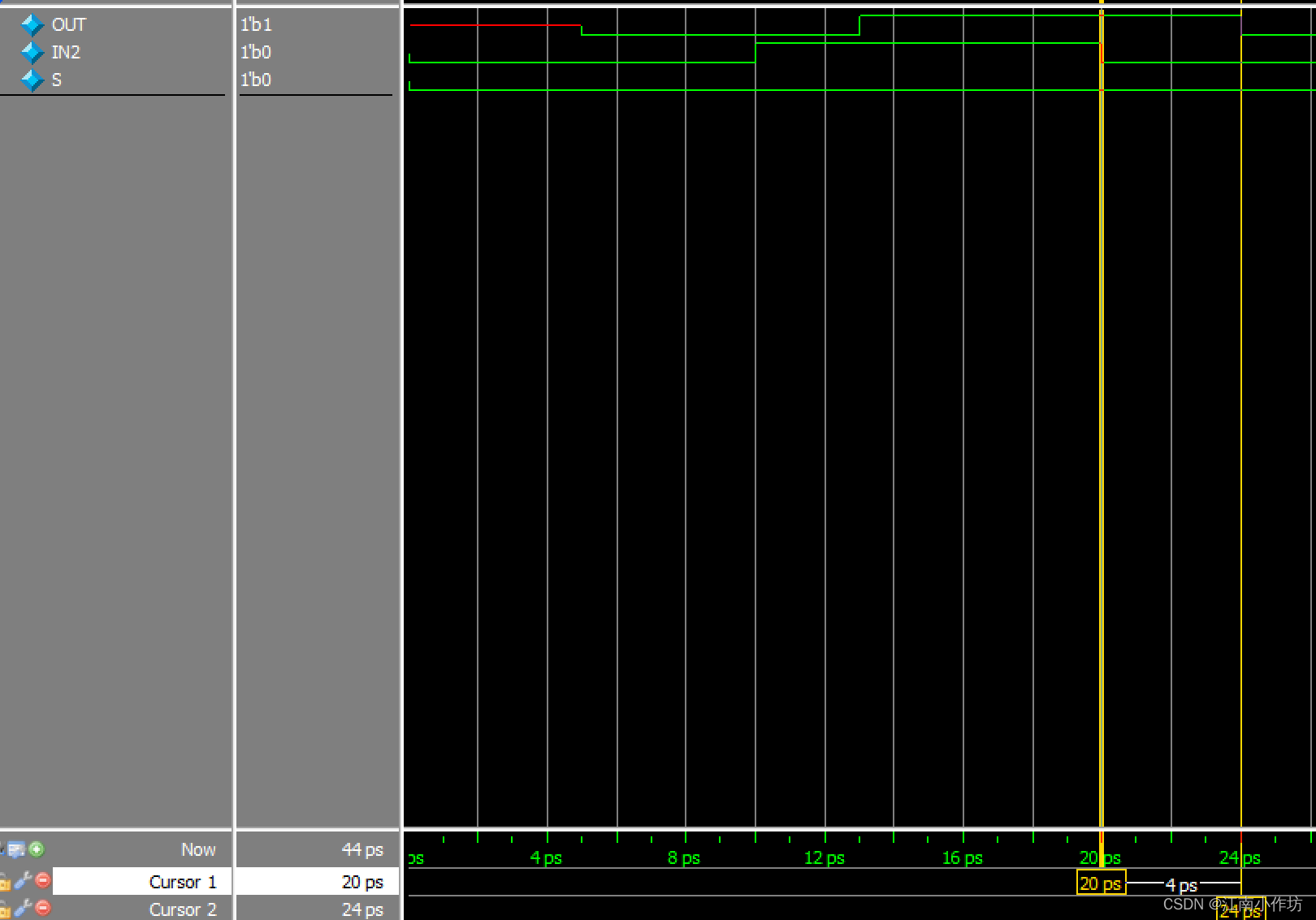

module my_mux2_to_1( output out, input in1,in2, input s ); bufif1 #(1:3:5,2:4:6,3:5:7) buf1(out,in1,s); bufif0 #(1:3:5,2:4:6,3:5:7) buf0(out,in2,s); endmodule仿真结果

- 当s为0时,输出in2,当in2为1时,延时了3个时间单位后,in2为1

- 当s为0时,输出in2,当in2为0时,延时了4个时间单位后,in2为0

- 当s为1时,同理。

- 当s为0时,输出in2,当in2为1时,延时了3个时间单位后,in2为1

边栏推荐

- 2022 crane driver (limited to bridge crane) examination questions and simulation examination

- What is the mosaic tailgate?

- [applet] realize the left and right [sliding] list through the scroll view component

- Matplotlib common settings

- 内存泄露和内存溢出的区别是什么?

- SWT/ANR问题--SWT 导致 kernel fuse deadlock

- Practical application and extension of plain framework

- 通过Go语言创建CA与签发证书

- Redis AOF log

- Wechat personal small store one click opening assistant applet development

猜你喜欢

Wechat personal small store one click opening assistant applet development

CKS CKA ckad change terminal to remote desktop

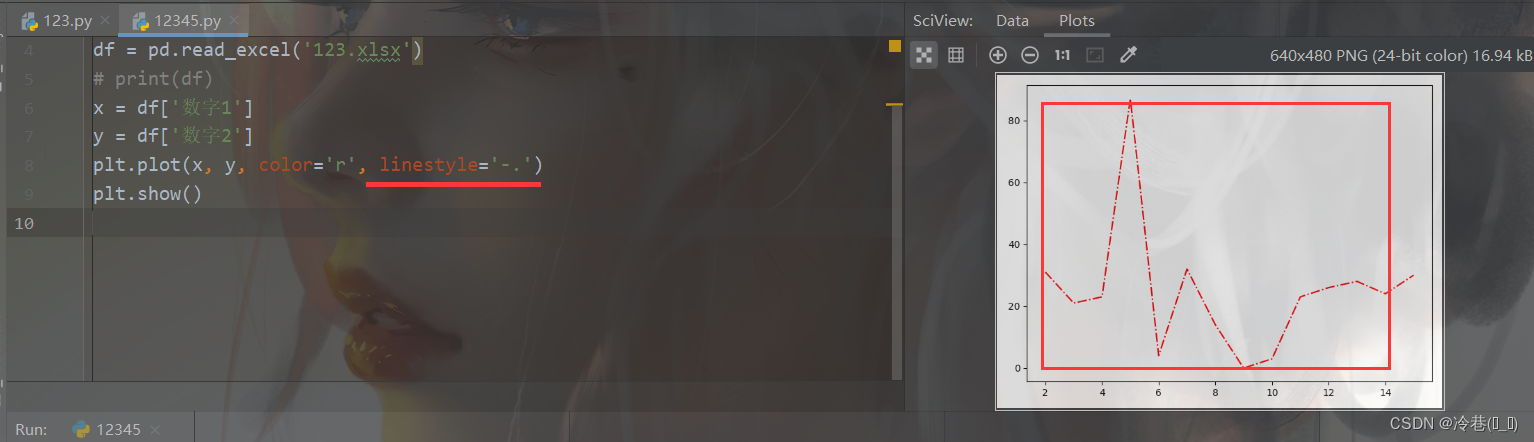

Matplotlib常用设置

flutter Unable to load asset: assets/images/888. png

Notblank and notempty

2022 examination questions and online simulation examination for safety management personnel of hazardous chemical business units

Practical application and extension of plain framework

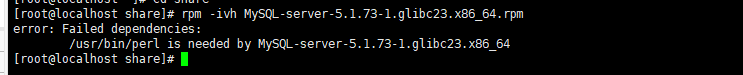

Notes on problems - /usr/bin/perl is needed by mysql-server-5.1.73-1 glibc23.x86_ sixty-four

SWT/ANR问题--SWT 导致 kernel fuse deadlock

Yunxin small class | common cognitive misunderstandings in IM and audio and video

随机推荐

Three development trends of enterprise application from the perspective of the third technological revolution

[micro service sentinel] sentinel integrates openfeign

Know --matplotlib

SWT/ANR问题--SWT 导致 low memory killer(LMK)

Switch to software testing, knowing these four points is enough!

力扣今日题-241. 为运算表达式设计优先级

问题随记 —— /usr/bin/perl is needed by MySQL-server-5.1.73-1.glibc23.x86_64

plain framework的实际应用和扩展

[micro service sentinel] @sentinelresource details

Daily three questions 6.28

Practical application and extension of plain framework

Practical application and extension of plain framework

The third part of the construction of the defense system of offensive and defensive exercises is the establishment of a practical security system

mysql binlog的清理

from pip._internal.cli.main import main ModuleNotFoundError: No module named ‘pip‘

物联网应用技术专业是属于什么类

为什么PHP叫超文本预处理器

Win 10 mstsc connect RemoteApp

Experience of practical learning of Silicon Valley products

Daily three questions 6.29