当前位置:网站首页>学内核之四:关于内核与硬件的衔接

学内核之四:关于内核与硬件的衔接

2022-08-02 04:19:00 【龙赤子】

要理解软件的行为,特别是底层的行为,比如内核的实现,就需要对硬件有所了解。

最近在学习内核时,遇到了一些理解上的问题,思考后发现,在硬件层面做一些工作,特别有助于对内核的学习,更有助于对上层软件工作过程的理解。

即便计算机技术以日新月异的速度发展到今天,其内在本质的体系结构仍未有脱离图灵机模型,强调这一点,是为了进一步强调,计算机的那些基础技术仍然是管用的,特别是中央控制器和内存的基本工作原理。要想理解操作系统层面软件的很多行为(比如原子操作、各种锁、每CPU变量、各种类型的栈、中断异常、各种上下文、系统调用、Cache一致性等等),最重要的就是理解CPU和内存的工作过程。

那怎么去掌握这些内容呢?这里讲讲我的方法。

实际上,现代CPU已经不是几年、甚至十几年前的样子了,很多新特性在不断地融入进来。其中涉及的细节,绝对让人望而生畏。随便一个现代CPU的手册都有上千页,这实实在在是一个系统工程。

所以,我们需要舍去一些细节的东西,一步一步来,逐渐的将自己的黑盒变成白盒。否则,陷入很多细节中就会出现只见树木不见森林的结果。

为了更好的掌握上面几个点,经过思考,我重新梳理了之前的一些东西,将其整理到一幅图中,通过这幅图,来辅助理解之前遇到的几个问题。

这幅图是原理性的,有很多简化之处,不过,目前这幅图可以帮助我们理解很多东西。

首先,简单说说图中的内容。上图左边一个大块,表示了CPU。该CPU内部有4个核心。右边那条代表了内存。

CPU里的每个核心,基本构成都是一样的,包括控制单元,算术运算单元,寄存器以及L1 Cache。

L2 Cache由部分核心共享,L3 Cache,则由所有核心共享。同时CPU内部还有内存管理单元MMU。MMU为了缓存表目,还有一个TLB。

当然,前面说了,上图中只是原理性的,很多东西没有体现出来。这包括一部分暂时还不清楚的东西。比如,对于MMU来讲,是每个核心一个还是所有核心共享。或者说,不同的CPU设计,两种可能都有。从有些资料上可以看到,TLB现在都是每CPU一个。如果可以独享,那么各个核心就可以并行访问内存。当然,共享也可以,无非就是多一些条目,每个核心分一点。

对于Cache和TLB,谁在前谁在后,也是一个问题。有的可能是先Cache再TLB,有的可能反过来。这就涉及VIVT/PIPT/VIPT等了。

还有Cache一致性协议MESI,也没有体现出来。这些东西,遇到了再补充。

好了,现在就以上图为基准,看看一些问题的处理,该如何理解。

边栏推荐

- 列表总结

- 6个月测试经验,面试跳槽狮子大开口要18K,只会点点点,给我整无语了。。

- CaDDN paper reading of monocular 3D target detection

- 轮询和长轮询的区别

- 跑通CogView教程

- Use the advanced timer of GD32F207 to generate hidden bugs in PWM waves

- 【每日一题】1374. 生成每种字符都是奇数个的字符串

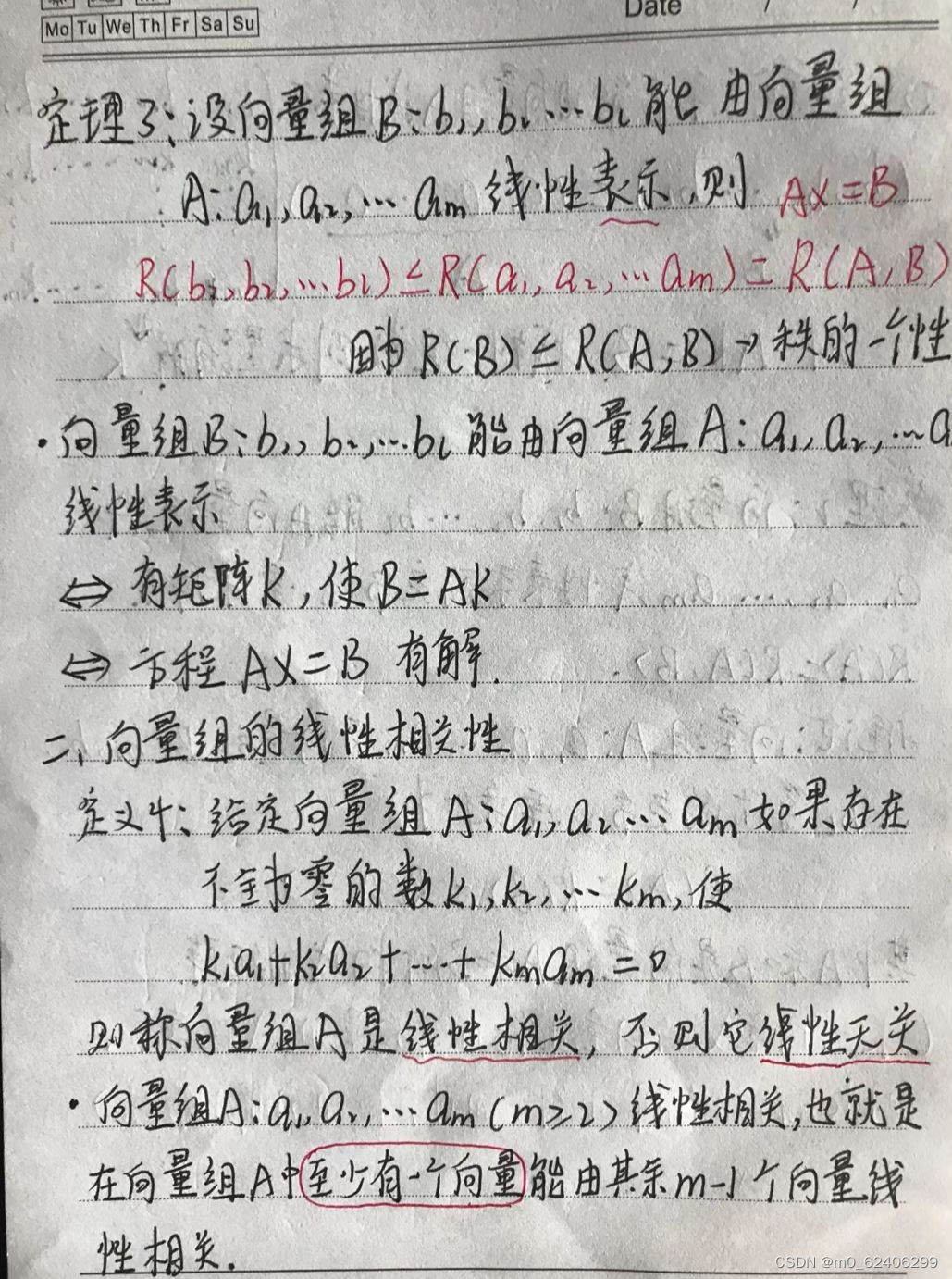

- 数学建模学习(76):多目标线性规划模型(理想法、线性加权法、最大最小法),模型敏感性分析

- P1012 [NOIP1998 提高组] 拼数

- 高等数学(第七版)同济大学 总习题三(后10题) 个人解答

猜你喜欢

随机推荐

2022 Huawei Software Elite Challenge (Preliminary) - Summary

MapFi paper structure organization

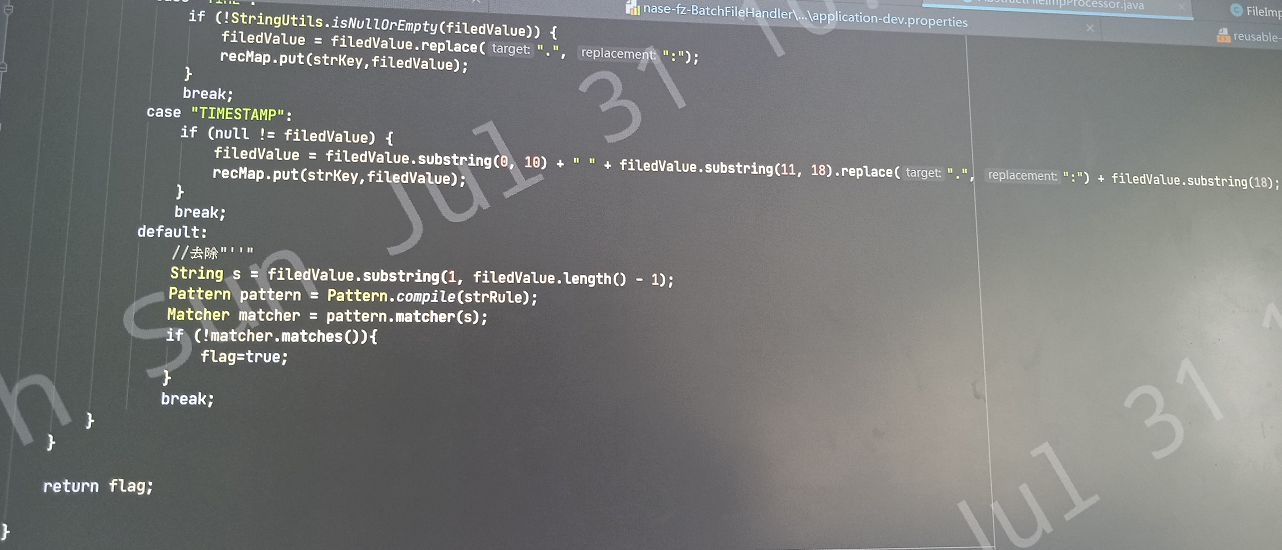

批量--09---批量读文件入表

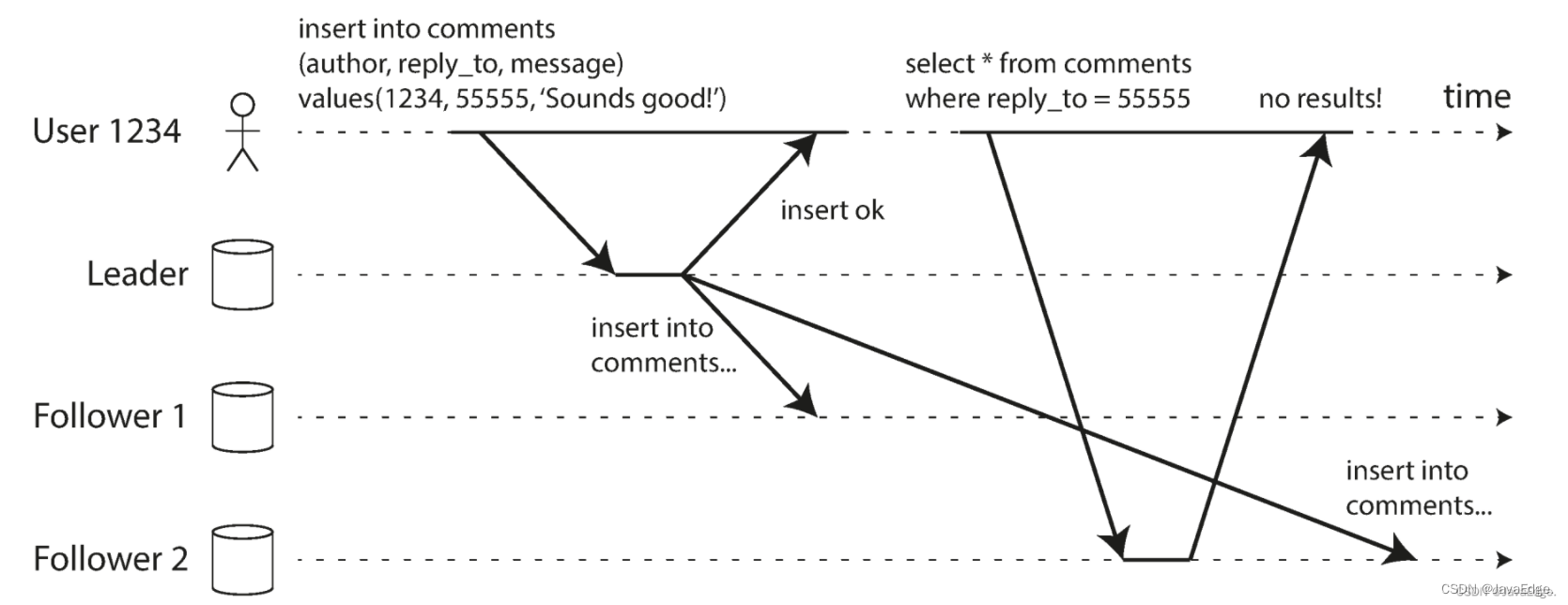

分布式系统的一致性与共识(1)-综述

C语言可以应用在哪些领域?

【面试】招聘要求

Visual SLAM Lecture Fourteen - Lecture 13 Practice: Designing a SLAM system (the most detailed code debugging and running steps)

Deep Blue Academy - 14 Lectures on Visual SLAM - Chapter 7 Homework

AFMG SysTune1.3.7使用图解

深度剖析-class的几个对象(utlis,component)-瀑布流-懒加载(概念,作用,原理,实现步骤)

What if some fields don't want to be serialized?

A practice arrangement about map GIS (below) GIS practice of Redis

如何解决QByteArray添加quint16双字节时错误?

26. 如何判断一个对象是否存活?(或者GC对象的判定方法)?

已更新 联通 电信 tiny模式

ScholarOne Manuscripts submits journal LaTeX file and cannot convert PDF successfully!

今天突然下雨

falco 【1】入门

关于地图GIS开发事项的一次实践整理(上)

HyperLynx中层叠设计实例