当前位置:网站首页>Karatsuba大数乘法的Verilog实现

Karatsuba大数乘法的Verilog实现

2022-08-03 07:06:00 【FPGA硅农】

我们以一个例子为例,来介绍一下Karatsuba大数乘法的基本原理。

题目:写一个乘法器,它可以计算两个32bit无符号数a,b的乘积。

针对这个问题,我们当然可以直接通过out<=a*b来实现,但是这种实现方式,需要在一个周期内计算一个32bit的乘法,当频率很高时,显然会成为整个系统的瓶颈。为此,我们将32bit乘法进行拆分,以期望提高时钟频率:

设a的高16位为ah,低16位为al,b的高16位为bh,低16位为bl,则有

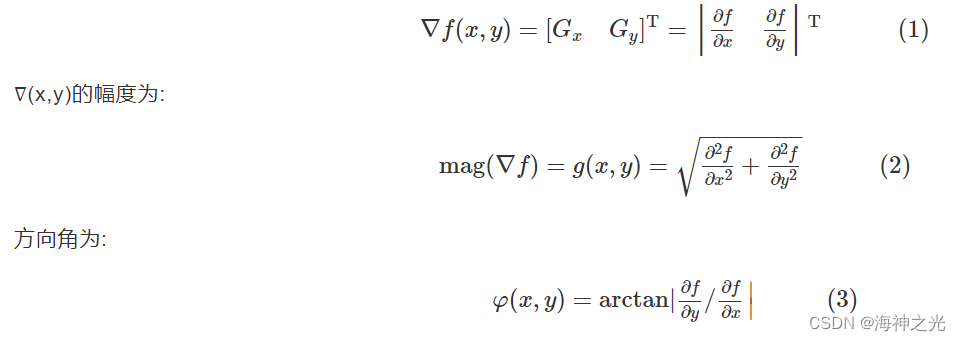

a ∗ b = ( a h ∗ 2 16 + a l ) ( b h

边栏推荐

猜你喜欢

随机推荐

解决移动端有纵向滚动条但是不能滚动的问题

帆软11版本参数联动为null查询全部

Shell脚本之一键安装mysql

9月考,如何选择靠谱正规的培训机构?

海思项目总结

boot - SSE

STL迭代器

[ 漏洞复现篇 ] yapi 代码执行 getshell 漏洞复现详解

static数据成员

如何使用电子邮件营销在五个步骤中增加产品评论

学会可视化大屏布局技巧,让领导都赞不绝口

死锁的成因和对应的解决方案

商业智能BI业务分析思维:供应链分析 – 如何控制牛鞭效应(二)

【卫朋】硬件创业:营销与开发同行

Windows安装MySQL(MIS)

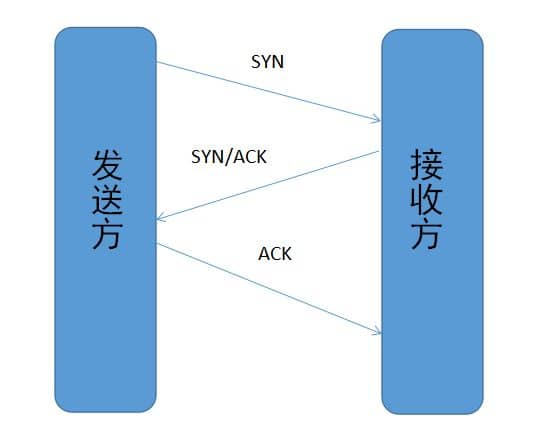

计算机网络常见面试题总结

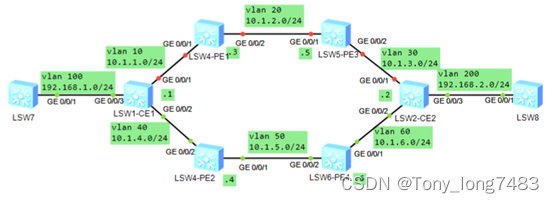

HCIP笔记整理 2022/7/18

多线程案例

MySQL - 触发器

七夕和程序员有毛关系?