当前位置:网站首页>FPGA的虚拟时钟如何使用?

FPGA的虚拟时钟如何使用?

2022-06-24 06:55:00 【碎碎思】

在我之前写的FPGA时序约束教程中,有一篇中讲到了虚拟时钟:

但文中对虚拟时钟的应用介绍的还不够详细,因此这里我们再对虚拟时钟做一个更加细致的介绍。

首先,虚拟时钟用于什么地方?

虚拟时钟通常用于设定输入和输出的延时,即set_input_delay和set_output_delay。可能有同学忘记这两个约束的用法了,这里我们再展示一下:

set_input_delay 0.5 -clock clkA [get_ports A]

set_output_delay 1 -clock clkB [get_ports B]其中clkA和clkB就是我们使用create_clock创建的主时钟或者虚拟时钟。

主时钟在创建的时候需要指定时钟输入端口,虚拟时钟不需要指定端口,所以称之为虚拟时钟。那什么场景下要用到虚拟时钟呢?

外部IO的参考时钟并不是设计中的时钟

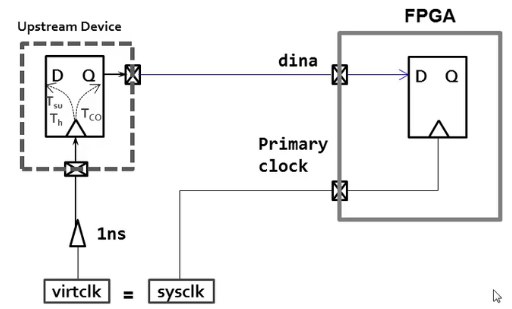

下图中,外部IO的参考时钟比设计中主时钟的路径上多了一个BUFFER,因此我们需要使用虚拟时钟来进行约束。

create_clock -name sysclk -period 10 [get_ports clkin]

create_clock -name virtclk -period 10

set_clock_latency -source 1 [get_clock virtclk]

set_input_delay -clock virtclk -max 4 [get_ports dina]

set_input_delay -clock virtclk -min 2 [get_ports dina]FPGA I/O路径参考时钟来源于内部衍生时钟,但与主时钟的频率关系并不是整数倍

如果I/O路径参考时钟源于内部的衍生时钟,那set_input_delay和set_output_delay约束中-clock参数后的时钟不能是衍生时钟,比如下图的例子中,输入10MHz时钟经过了MMCM后去采输入的数据。

a) 如果MMCM没有负的相移而且输出的频率也是10MHz,那么直接使用主时钟来约束input delay。

create_clock -period 100.000 -name clk [get_ports clk]

set_input_delay -clock clk -max 2.000 [get_ports datain]

set_input_delay -clock clk -min 1.000 [get_ports datain]b) 如果MMCM输出频率是60MHz,那么这个衍生时钟跟主时钟并不是整数倍关系,这时就需要用到虚拟时钟了

create_clock -period 100.000 -name clk [get_ports clk]

create_clock -name clk_port_vclk -period 16.67

set_input_delay -clock clk_port_vclk -max 2 [get_ports datain]

set_input_delay -clock clk_port_vclk -min 1 [get_ports datain]在不修改时钟特性的情况下针对I/O指定不同的jitter和latency

这个需求我们可以在Constraints Wizards中指定,简单又方便

在设置完成后,可以看到Tcl Command Preview中提示的约束指令。

完

边栏推荐

- Cold thinking on the hot track: multiplier effect is the fundamental requirement of East West calculation

- Solution of electric education system for intelligent supervision station

- Application of JDBC in performance test

- Simple summary of lighting usage

- 不止于观测|阿里云可观测套件正式发布

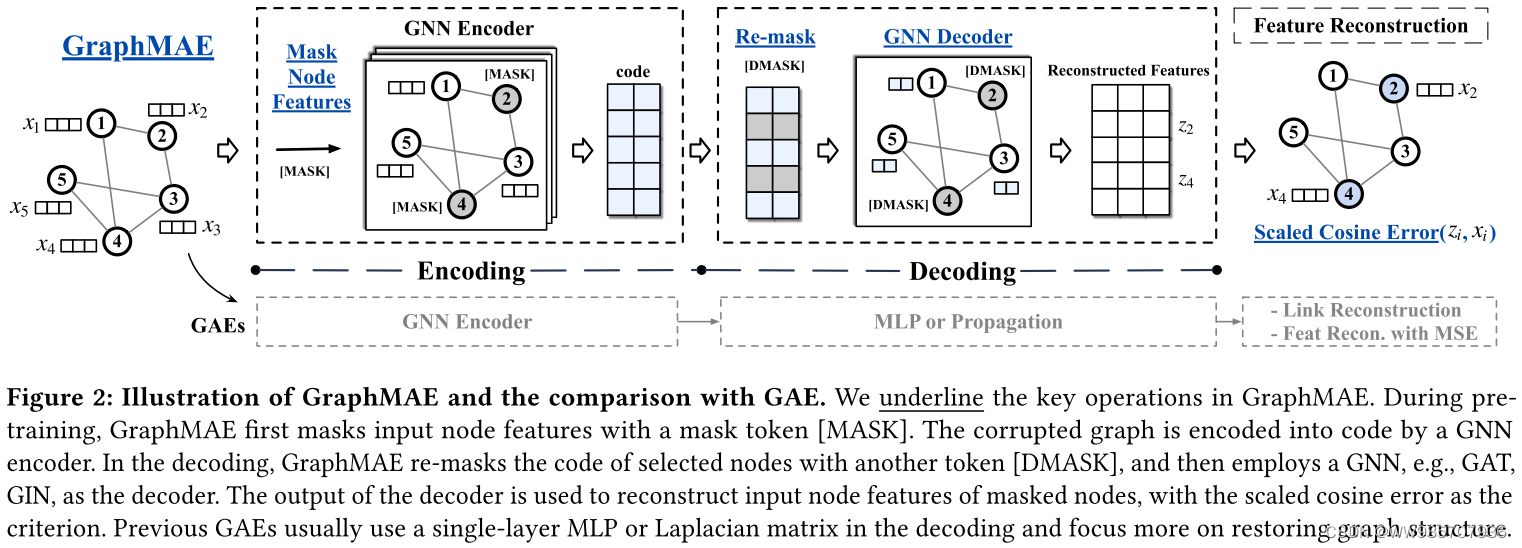

- GraphMAE----論文快速閱讀

- Hilbert Huang Transform

- 宝塔面板安装php7.2安装phalcon3.3.2

- Thread considerations

- 毕业两年月薪36k,说难也不难吧

猜你喜欢

Graphmae ---- quick reading of papers

Solve the problem of notebook keyboard disabling failure

Part 2: drawing a window

![[C language] system date & time](/img/de/faf397732bfa4920a8ed68df5dbc48.png)

[C language] system date & time

有关iframe锚点,锚点出现上下偏移,锚点出现页面显示问题.iframe的srcdoc问题

Swift Extension NetworkUtil(网络监听)(源码)

解决错误: LNK2019 无法解析的外部符号

![[nilm] non intrusive load decomposition module nilmtk installation tutorial](/img/d0/bc5ea1cbca9ee96a2fe168484ffec4.png)

[nilm] non intrusive load decomposition module nilmtk installation tutorial

Latest news of awtk: new usage of grid control

对于flex:1的详细解释,flex:1

随机推荐

闲谈:3AC到底发生了什么?

Introduction of model compression tool based on distiller

Graphmae - - lecture rapide des documents

Examples of corpus data processing cases (reading multiple text files, reading multiple files specified under a folder, decoding errors, reading multiple subfolder text, batch renaming of multiple fil

LINQ 查询(2)

不止于观测|阿里云可观测套件正式发布

模型效果优化,试一下多种交叉验证的方法(系统实操)

Los Angeles p1051 who won the most Scholarships

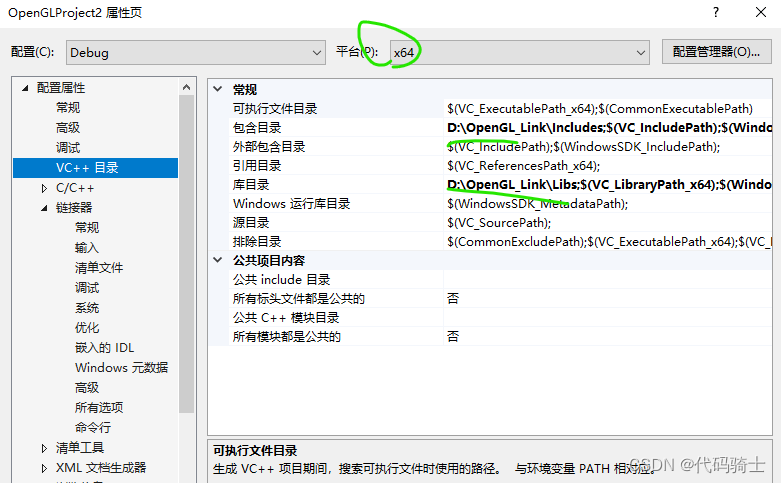

第 1 篇:搭建OpenGL环境

Chapter 1 overview of canvas

OC extension detects whether an app is installed on the mobile phone (source code)

Swift Extension ChainLayout(UI的链式布局)(源码)

第 3 篇:绘制三角形

Installation and use of selenium IDE

Tuple remarks

Cold thinking on the hot track: multiplier effect is the fundamental requirement of East West calculation

Leetcode 207: course schedule (topological sorting determines whether the loop is formed)

Learning event binding of 3D visualization from scratch

Chrono usage notes

Selenium IDE的安装以及使用