当前位置:网站首页>Understand chisel language thoroughly 08. Chisel Foundation (V) -- wire, REG and IO, and how to understand chisel generation hardware

Understand chisel language thoroughly 08. Chisel Foundation (V) -- wire, REG and IO, and how to understand chisel generation hardware

2022-07-04 14:08:00 【github-3rr0r】

Chisel Basics ( 5、 ... and )——Wire、Reg and IO, And how to understand Chisel Build hardware

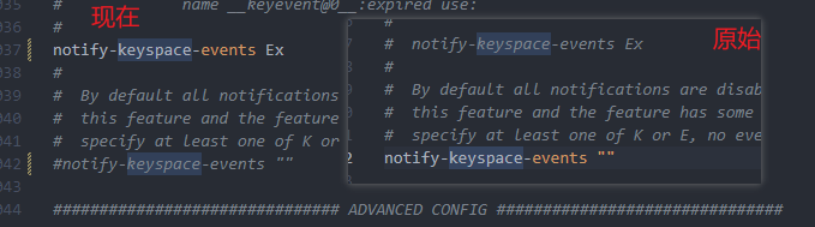

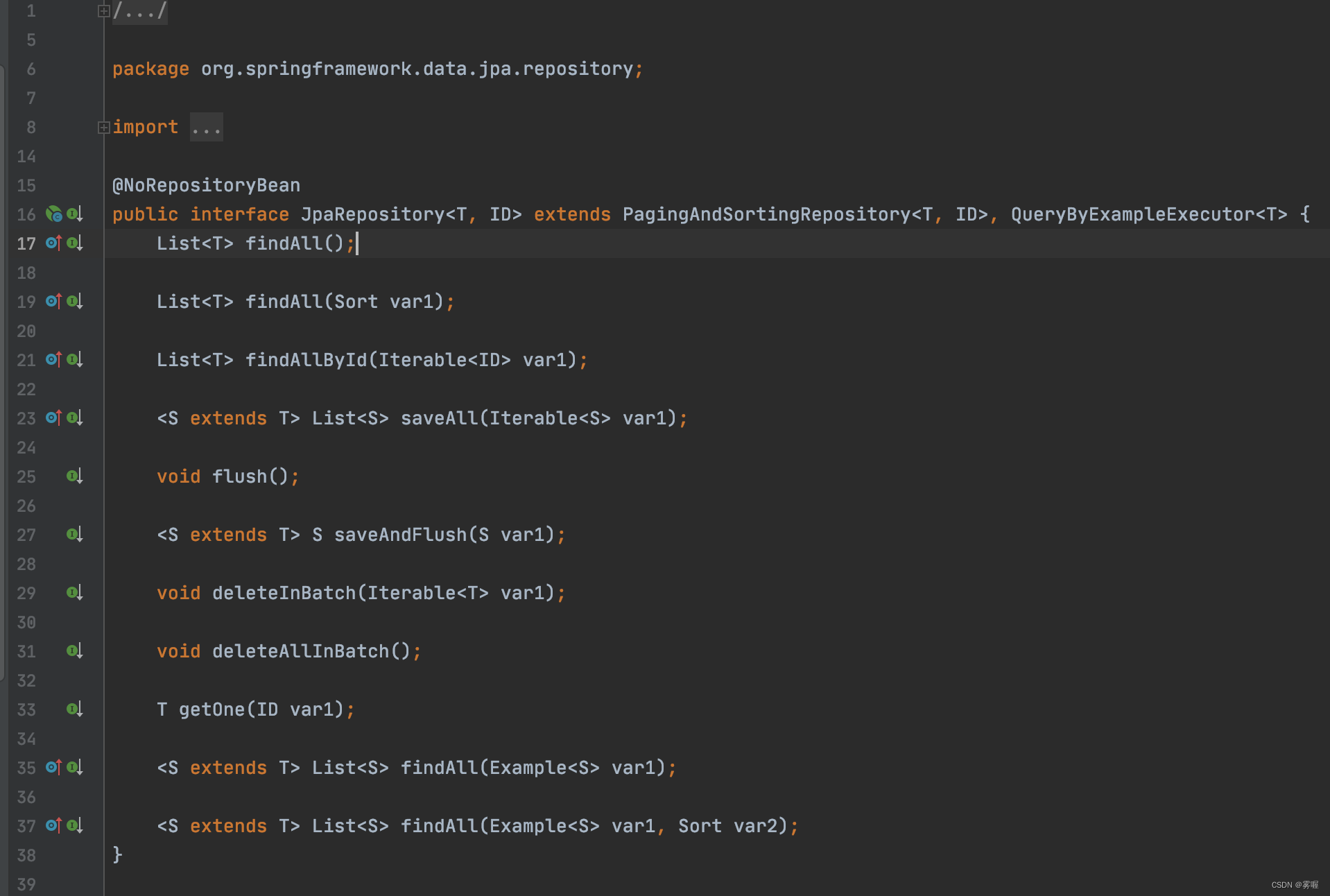

The conclusion of the previous article mentioned ,UInt、SInt and Bits All are Chisel type , They themselves do not directly represent hardware , Only by encapsulating them into Wire、Reg or IO Will generate a circuit . This matter can be understood in this way , Digital logic circuits are made up of wires 、 Logic gate 、 Registers and input / output ( Including clock and reset signal ) And so on , The connection corresponds to Wire, Logic gate corresponding operator , Registers correspond to Reg, Input output correspondence IO. So in Chisel How can they be used in ? How to understand Chisel Generation circuit ? Learn this article together .

Wire、Reg and IO

stay Chisel in ,Wire Used to represent combinatorial logic ,Reg Used to represent registers (D- Set of triggers ), and IO Is used to represent the interface of a module ( For example, the pin of a specific integrated circuit ). As mentioned earlier ,Wire、Reg and IO Can encapsulate any Chisel type , And of course Bundle and Vec.

stay Scala in , Variables are divided into var and val Two types of , The former is variable , The latter is immutable . And in the Chisel in , We just need to use val To describe the circuit , It's immutable Scala Variable , such as :

val number = Wire(UInt())

val reg = Reg(SInt())

We can assign or reassign the value or expression to Wire、Reg or IO, Use of Chisel Operators are :=:

number := 10.U

reg := value - 3.U

This is obviously the same as Scala The assignment operator in = It's different . How to use these two operators ? It's simple , stay establish When we use a hardware object Scala The operator =, And I'm giving What already exists When assigning or reassigning hardware objects , Just use Chisel The operator :=.

Combinatorial logical values can also be conditionally assigned , But you need to assign values to each branch of the condition . Otherwise , A latch will be introduced (latch), This is a Chisel Compiler does not accept . The best way is to create Wire A default value is given when , therefore , The previous code is better written like this :

val number = WireDefault(10.U(4.W))

Empathy , As mentioned before ,Chisel Will infer the required bit width for signals and registers , But it is better to specify the desired bit width when creating hardware objects . On most occasions , It is also best to give the register a known reset initialization value :

val reg = RegInit(0.S(8.W))

RegInit and WireDefault not quite the same , The former refers to the value at reset , The latter refers to the default connection .

as for IO, Interface for declaring a module , The usage is usually as follows :

val io = IO(new Bundle {

val in_a = Input(UInt(8.W))

val out_b = Output(UInt(8.W))

})

IO() It's a bundle Example ,bundle Inside is the input and output interface , Use them separately Input and Output encapsulation . Here is just a brief introduction , We will talk about it later .

How to understand Chisel Build hardware

We have so far , Some have been lifted Chisel The basic code of , It looks like traditional programming languages, such as C and Java This kind is almost . however ,Chisel Like other hardware description languages , It really defines hardware components . What's the difference ? In software , The code is executed line by line , In hardware, all lines of code are Parallel execution Of .

Write Chisel Be sure to keep in mind Chisel It's really hardware generation . You can imagine , Or draw on paper , We wrote them one by one Chisel Circuit description generated module . Create one component at a time , Will add a hardware , Each assignment statement , Will generate a gate circuit and / Or trigger .

So technically ,Chisel When executing code , It's Executive Scala Program , And then by executing Chisel sentence , aggregate (collect) All hardware components and connect these nodes . The network composed of these hardware nodes is Chisel Generated hardware , Can be born Verilog Code for ASIC or FPGA comprehensive , It can also be used. Chisel tester To test . The network composed of these hardware nodes is completely parallel !

It may be a little difficult for people who have written software before to understand this kind of parallel execution , Because it is different from the parallel program of software , Hardware is naturally parallel , There is no need to assign programs to threads , There is no need to lock the communication between threads , It is a very simple parallel execution , The current runs simultaneously in every part of the hardware , That's it .

Conclusion

When I first came into contact with hardware description language , I'm confused, too , Often use the thinking of writing software to write hardware , The last thing I wrote is not what I imagined . You can only stop thinking about writing software , Simply understand writing hardware as building blocks , What we need to do is to logically connect them .

up to now , We haven't run the code yet , Just learned the basics Chisel grammar . Next article , We will learn how to use sbt Build our Chisel Project and run , At the same time, it also briefly introduces Chisel Tool flow for , Coming soon .

边栏推荐

- 逆向调试入门-PE结构-资源表07/07

- 吃透Chisel语言.09.Chisel项目构建、运行和测试(一)——用sbt构建Chisel项目并运行

- 基于PaddleX的智能零售柜商品识别

- 美国土安全部长:国内暴力极端主义是目前美面临的最大恐怖主义威胁之一

- Haobo medical sprint technology innovation board: annual revenue of 260million Yonggang and Shen Zhiqun are the actual controllers

- 常见 content-type对应表

- PHP log debugging

- 2022年山东省安全员C证考试题库及在线模拟考试

- 中邮科技冲刺科创板:年营收20.58亿 邮政集团是大股东

- How to choose a technology stack for web applications in 2022

猜你喜欢

Interviewer: what is the internal implementation of hash data type in redis?

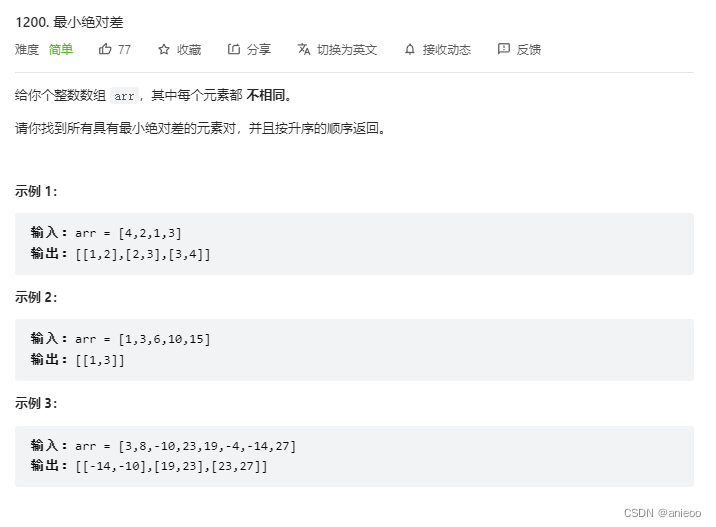

1200. 最小绝对差

Doctoral application | West Lake University Learning and reasoning system laboratory recruits postdoctoral / doctoral / research internship, etc

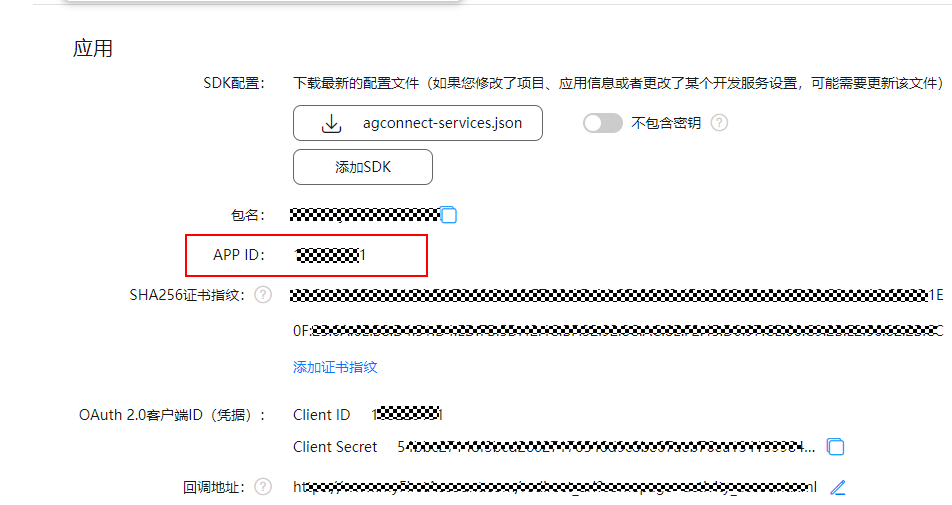

【FAQ】华为帐号服务报错 907135701的常见原因总结和解决方法

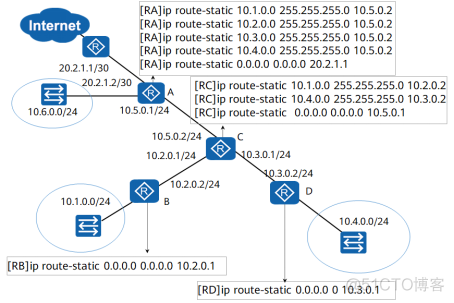

使用默认路由作为指向Internet的路由

.Net之延迟队列

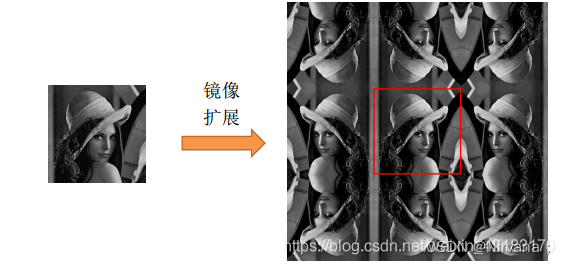

【Matlab】conv、filter、conv2、filter2和imfilter卷积函数总结

Summary of recent days (non-technical article)

Fisher信息量检测对抗样本代码详解

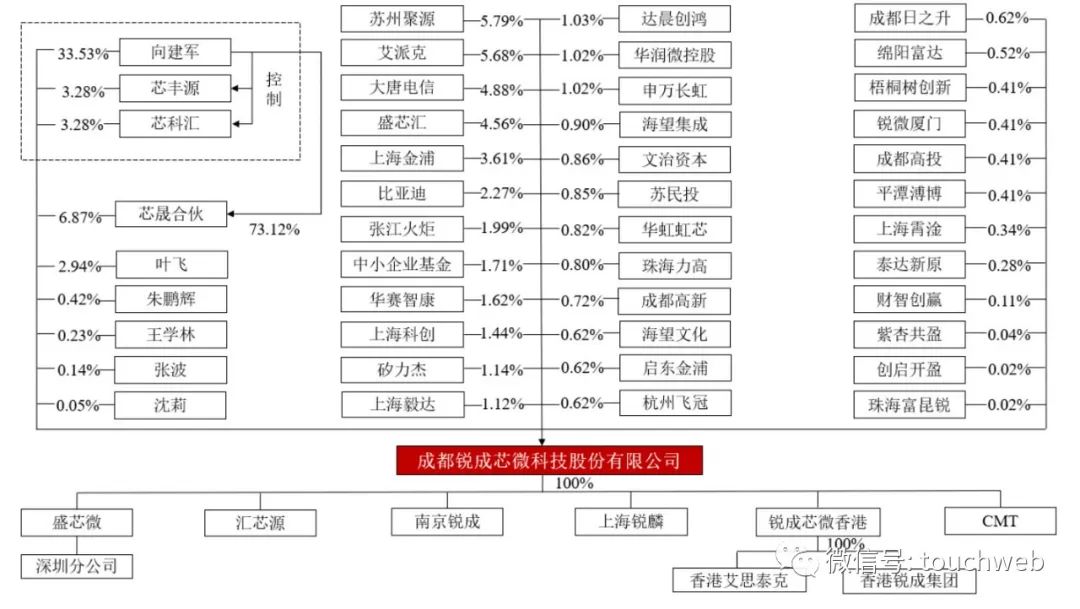

锐成芯微冲刺科创板:年营收3.67亿拟募资13亿 大唐电信是股东

随机推荐

1200. Minimum absolute difference

Unittest框架之断言

Deming Lee listed on Shenzhen Stock Exchange: the market value is 3.1 billion, which is the husband and wife of Li Hu and Tian Hua

Doctoral application | West Lake University Learning and reasoning system laboratory recruits postdoctoral / doctoral / research internship, etc

Use the default route as the route to the Internet

吃透Chisel语言.05.Chisel基础(二)——组合电路与运算符

2022年起重机械指挥考试模拟100题模拟考试平台操作

Fisher信息量检测对抗样本代码详解

Yingshi Ruida rushes to the scientific and Technological Innovation Board: the annual revenue is 450million and the proposed fund-raising is 979million

【R语言数据科学】:交叉验证再回首

美国土安全部长:国内暴力极端主义是目前美面临的最大恐怖主义威胁之一

markdown 语法之字体标红

使用默认路由作为指向Internet的路由

xshell/bash/zsh 等终端鼠标滚轮乱码问题(转)

WS2811 M是三通道LED驱动控制专用电路彩灯带方案开发

Huahao Zhongtian rushes to the scientific and Technological Innovation Board: the annual loss is 280million, and it is proposed to raise 1.5 billion. Beida pharmaceutical is a shareholder

.Net之延迟队列

吃透Chisel语言.11.Chisel项目构建、运行和测试(三)——Chisel测试之ScalaTest

基于链表管理的单片机轮询程序框架

程序员转方向