当前位置:网站首页>手把手教你移植 tinyriscv 到FPGA上

手把手教你移植 tinyriscv 到FPGA上

2022-06-27 20:56:00 【luoganttcc】

一、下载源码

tinyriscv 官方库链接:https://gitee.com/liangkangnan/tinyriscv

这里我选择的是 master v2.4 版本: https://gitee.com/liangkangnan/tinyriscv/tree/v2.4/

用 Git 克隆到本地。(使用的终端软件是 Cygwin,安装教程:https://blog.csdn.net/qq_44447544/article/details/123246995?spm=1001.2014.3001.5501)

二、创建 Vivado 工程

打开 tinyriscv 文件夹,可以看到有很多目录:

这里 rtl 为tinyriscv Verilog源码。

用 Vivado 创建工程,并把源码和约束添加进去,具体步骤可见 tinyriscv\fpga\README.md 文件,写的很详细。

三、修改约束文件

所谓的移植其实就是根据自己所用的板卡编写正确的管脚约束文件,并且根据需求修改源码。

基本步骤如下:

先修改约束文件中的时钟和复位引脚绑定

修改状态指示信号引脚绑定

在源码中,over、succ、halted_ind都是状态指示信号,应该绑定到开发板上的 LED上,而不同的开发板LED的电路连接方式也不同,有的是给高电平亮,有的是给低电平亮。而 tinyriscv 源码中是给低电平,即状态指示信号有效时为低电平,而达芬奇开发板LED是要给高电平亮,所以要修改源码,取反下就行。

3.修改串口 tx 和 rx 信号引脚绑定

注:这个是绑开发板中未使用的任意管脚,而不是绑开发板上已有的串口。

4.修改GPIO外设所用的引脚约束

5.修改JTAG所用的引脚约束

注:这个是绑开发板中未使用的任意管脚,而不是绑FPGA自己的JTAG,FPGA自己的JTAG已经和开发板上的Flash绑定好了,无法使用,就像按键,led灯所绑定的管脚一样,都已经被使用了,无法被复用。

6.修改SPI所用的引脚约束

7.添加时钟约束

由于 jtag_TCK 信号在设计中是作为同步时钟的,而敏感列表中无晶振时钟所对应的信号。所以要添加下面语句;

create_clock -name jtag_clk_pin -period 300 [get_ports {jtag_TCK}];

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets jtag_TCK]

完整的约束文件:

# 时钟约束50MHz,占空比50%

create_clock -add -name sys_clk_pin -period 20.00 -waveform {0 10} [get_ports {clk}];

# 时钟引脚

set_property -dict { PACKAGE_PIN R4 IOSTANDARD LVCMOS33 } [get_ports {clk}];

# 复位引脚

set_property -dict { PACKAGE_PIN U2 IOSTANDARD LVCMOS33 } [get_ports {rst}];

# 程序执行完毕指示引脚,over 为1时有效,点亮led0

set_property -dict { PACKAGE_PIN R2 IOSTANDARD LVCMOS33 } [get_ports {over}];

# 程序执行成功指示引脚,succ 为1时有效,点亮led1

set_property -dict { PACKAGE_PIN R3 IOSTANDARD LVCMOS33 } [get_ports {succ}];

# CPU停住指示引脚,halted_ind 为1时有效,点亮led2

set_property -dict { PACKAGE_PIN V2 IOSTANDARD LVCMOS33 } [get_ports {halted_ind}];

# 串口下载使能引脚,由于没有拨码开关和自锁开关,所以绑定到key0上,key0按住不放时才使能串口下载

set_property -dict { PACKAGE_PIN T1 IOSTANDARD LVCMOS33 } [get_ports {uart_debug_pin}];

# 串口发送引脚

set_property -dict { PACKAGE_PIN AB6 IOSTANDARD LVCMOS33 } [get_ports {uart_tx_pin}];

# 串口接收引脚

set_property -dict { PACKAGE_PIN V7 IOSTANDARD LVCMOS33 } [get_ports {uart_rx_pin}];

# GPIO0引脚

set_property -dict { PACKAGE_PIN F16 IOSTANDARD LVCMOS33 } [get_ports {gpio[0]}];

# GPIO1引脚

set_property -dict { PACKAGE_PIN F15 IOSTANDARD LVCMOS33 } [get_ports {gpio[1]}];

# JTAG TCK引脚 PortA 0

set_property -dict { PACKAGE_PIN AA8 IOSTANDARD LVCMOS33 } [get_ports {jtag_TCK}];

create_clock -name jtag_clk_pin -period 300 [get_ports {jtag_TCK}];

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets jtag_TCK]

# JTAG TMS引脚 PortA 3

set_property -dict { PACKAGE_PIN AB8 IOSTANDARD LVCMOS33 } [get_ports jtag_TMS];

# JTAG TDI引脚 PortA 1

set_property -dict { PACKAGE_PIN Y7 IOSTANDARD LVCMOS33 } [get_ports {jtag_TDI}];

# JTAG TDO引脚 PortA 2

set_property -dict { PACKAGE_PIN Y8 IOSTANDARD LVCMOS33 } [get_ports jtag_TDO];

# SPI MISO引脚

set_property -dict { PACKAGE_PIN F14 IOSTANDARD LVCMOS33 } [get_ports {spi_miso}];

# SPI MOSI引脚

set_property -dict { PACKAGE_PIN F13 IOSTANDARD LVCMOS33 } [get_ports {spi_mosi}];

# SPI SS引脚

set_property -dict { PACKAGE_PIN E13 IOSTANDARD LVCMOS33 } [get_ports {spi_ss}];

# SPI CLK引脚

set_property -dict { PACKAGE_PIN E14 IOSTANDARD LVCMOS33 } [get_ports {spi_clk}];

#SPI 相关设置

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN PULLUP [current_design]

四、综合实现

Layout:

资源消耗;

所以只要板卡上的资源足够,都可以成功移植 tinyriscv。

五、通过 JTAG debug RISCV

调试器芯片:ftdi4232HL

配置文件:

ft4232h.cfg:

adapter driver ftdi

# VID and PID

ftdi vid_pid 0x0403 0x6011

transport select jtag

# TCK frequency

adapter speed 100

# ftdi_layout_init [data] [direction]

# 指定FTDI GPIO的初始数据和方向,16bit数据宽度。

# 参数data中1表示高电平,0表示低电平,而参数direction中1表示输出,0表示输入(注意与常规的设定不同)

ftdi layout_init 0x0018 0x05fb

# ftdi_layout_signal name [-data|-ndata data_mask] [-input|-ninput input_mask] [-oe|-noe oe_mask] [-alias|-nalias name]

# 创建一个名字为name的信号。

# [-data|-ndata data_mask]

# data_mask:pin mask ndata:invert -data:normal bit

# data_mask是对应pin脚的掩码,-ndata表示输入数据反向,-data则不反向。

ftdi layout_signal nSRST -data 0x0010 -noe 0x0400

tinyriscv.cfg:

set _CHIPNAME riscv

jtag newtap $_CHIPNAME cpu -irlen 5 -expected-id 0x1e200a6f

set _TARGETNAME $_CHIPNAME.cpu

target create $_TARGETNAME riscv -chain-position $_TARGETNAME

riscv set_reset_timeout_sec 1

init

halt

打开 cmd 执行命令:openocd -f ft4232h.cfg -f tinyriscv.cfg

成功检测到 RISCV CPU。

原文链接

边栏推荐

- Spark bug practice (including bug:classcastexception; connectexception; NoClassDefFoundError; runtimeException, etc.)

- 跟着存档教程动手学RNAseq分析(四):使用DESeq2进行DE分析的QC方法

- pytorch实现kaggle猫狗识别

- Livox Lidar+海康Camera 基于loam的实时三维重建生成RGB彩色点云

- The latest cloud development wechat balance charger special effect applet source code

- To build a "strong core" in Nansha, the first IC Nansha conference was held in Nansha

- 树莓派(以及各种派)使用指南

- 「R」 Using ggpolar to draw survival association network diagram

- 【经典干货书】数据科学中的信息理论方法,561页pdf

- SQL Server 2016详细安装教程(附注册码和资源)

猜你喜欢

未能加载文件或程序集“CefSharp.Core.Runtime.dll”或它的某一个依赖项。 不是有效的 Win32 应用程序。 (异常来自 HRESULT:0x800700C1)

电子科大(申恒涛团队)&京东AI(梅涛团队)提出用于视频问答的结构化双流注意网络,性能SOTA!优于基于双视频表示的方法!

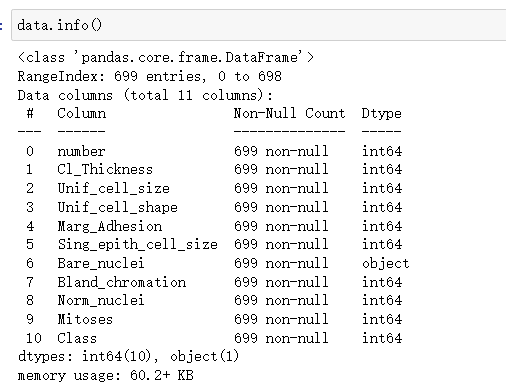

良/恶性乳腺肿瘤预测(逻辑回归分类器)

如何设置企业微信群机器人定时发消息?

第一性原理(最优解理论)

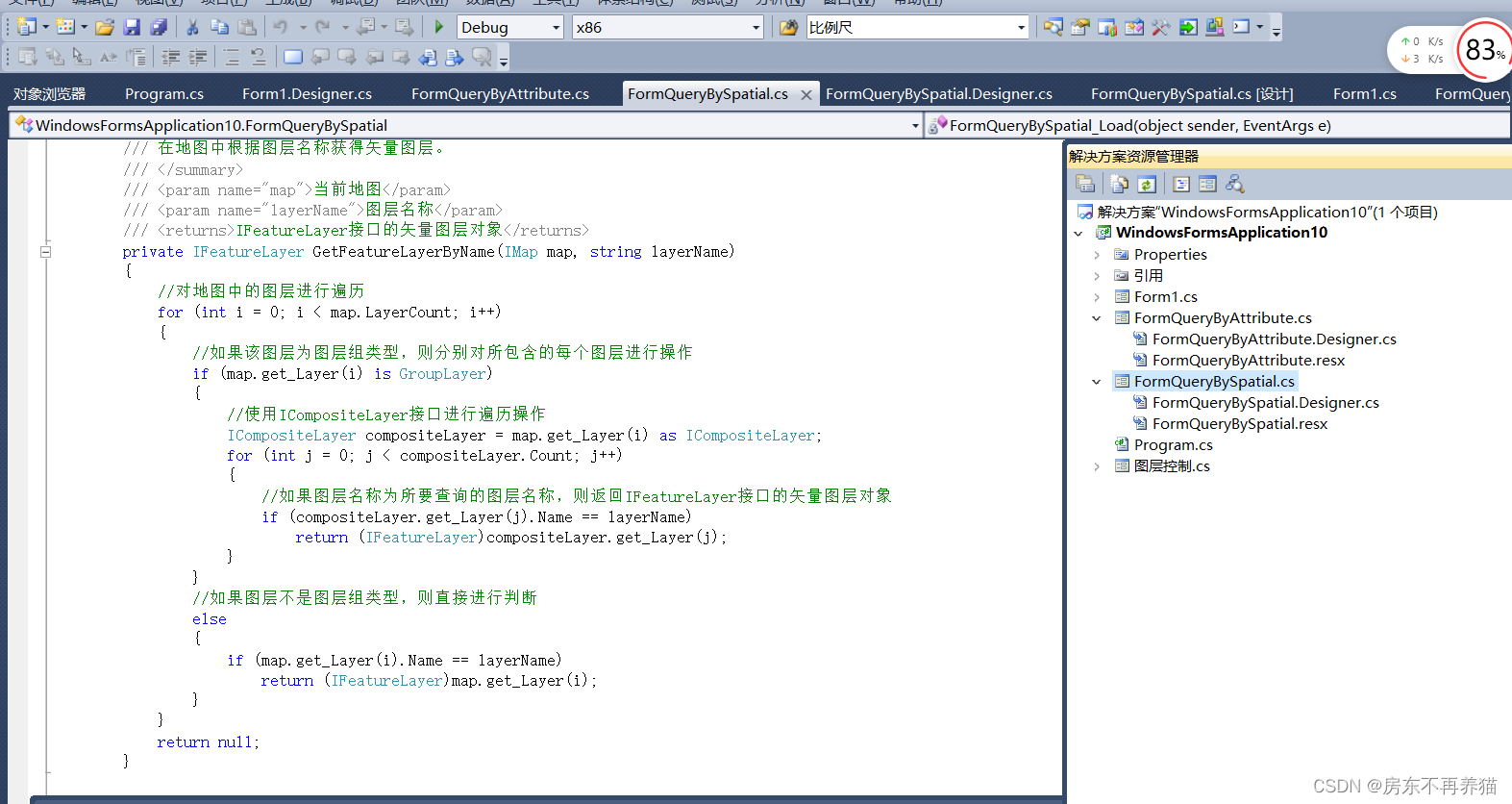

Spatial relation query and graph based query in secondary development of ArcGIS Engine

EasyCVR平台路由日志功能的技术实现过程【附代码】

Detect objects and transfer images through mqtt

Arcgis-engine二次开发之空间关系查询与按图形查询

跨系统数据一致性问题解决方案汇总

随机推荐

Livox Lidar+海康Camera实时生成彩色点云

Livox Lidar+海康Camera 基于loam的实时三维重建生成RGB彩色点云

【数字IC/FPGA】检测最后一个匹配序列的位置

[网络]常见的请求方法

Azure Kinect DK realizes 3D reconstruction (Jetson real-time version)

Sentinel

Spug - 轻量级自动化运维平台

小芯片chiplet技术杂谈

Batch processing - Excel import template 1.1- support multiple sheet pages

Vivado FFT IP的使用说明

Azure Kinect DK 实现三维重建 (PC非实时版)

Aggregation and index optimization of mongodb basic operations

支持删除,更新任意结点的优先级队列

【经典干货书】数据科学中的信息理论方法,561页pdf

MySQL十八:写语句的执行过程

因美纳陷数据泄露“丑闻”:我国基因数据安全能交给美企吗?

Avoid using 100vh[easy to understand] at mobile terminal

【IDEA】IDEA 格式化 代码技巧 idea 格式化 会加 <p> 标签

vivado 如何添加时序约束

[essay]me53n add button to call URL