当前位置:网站首页>RISC-V instruction format and 6 basic integer instructions

RISC-V instruction format and 6 basic integer instructions

2022-08-02 13:12:00 【good moon births autumn】

The instruction format is the structural form of the instruction using binary encoding,Generally, an instruction is divided into two parts: an operation code and an address code.:

一、操作码

The opcode indicates the attribute function of the instruction and the type of instruction executed.The number of bits corresponding to the operand determines the maximum number of instructions that the computer can implement.例如,操作码是 7 位的二进制码,The maximum number of instructions a computer can implement is 128(2^7).Opcodes are subdivided into fixed length and variable length according to whether the number of bits is variable.

Fixed-length opcodes keep the number of bits unchanged,All instructions operation code length is equal to a constant value,and they must be in a field.它的优点主要有:Regular command format,Simplified low-level hardware design,Very short instruction decode time,Improves the overall performance of the computer system.But the coding efficiency of instructions is low,Has a lot of information redundancy,Greatly increases the total length of the code,可扩展性差.RISC- V The solution used is a fixed-length opcode.

可变长度操作码,Also known as extended opcode,It is an extension to the related opcodes,The binary length of the opcode can be changed and reset,and can exist in multiple fields at the same time.Variable-length opcodes usually have specific fields as the corresponding opcodes,And the remaining instruction part,Will use the extended method corresponding to the address code.

二、地址码

The function of the address code is different from that of the opcode,The main function of the address code is to indicate the object of the instruction operation,Get the address of the object being manipulated、Operands store address and check equipment, etc.The structure of the address code is much more complex than that of the opcode,主要包括address where source operand is stored、The destination operand address where the result is stored、and the address of the next instruction that will jump the link.The address of the next instruction is generally implicit,It must be obtained through computational analysis.According to the number of operand addresses in an instruction,Divide the address code into the following types.

1、zero address code

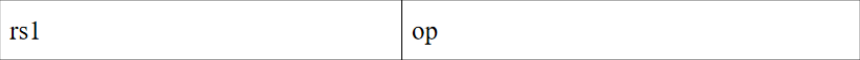

zero address code,just an opcode and no address code,The instruction format as shown in the figure below,op代表操作码.The zero address code instruction does not need to set the corresponding operand first,This may be an already set up the operands.e.g. no-op、Shutdown and other orders.

2、an address code

an address code,There is only one address where the operand is stored,It is also the storage address of the final processing result., It is also called a single operand instruction.The instruction format as shown in the figure below,op 代表操作码,rs1 represents the address of the operand.e.g. increment operation,After processing the operand for that address,Store the final processing result back to the original address.

3、two address code

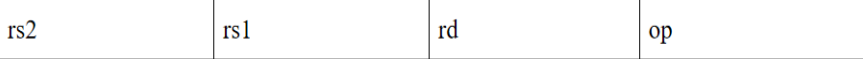

Two-address code instructions,Also known as a two-operand instruction,It is the most widely used computer system in the current stage.The instruction format as shown in the figure below,op 是操作码,rs1 Indicates the source operand address and the storage destination address of the final processing result,rs2 Indicates another source operand address.

4、三地址码

Three-address code instructions,Has three addresses to store operands.The command format is shown in the figure below,op 代表操作码,rs1 Represents the source operand address,rs2 Represents another source operand address,rd Represents the destination operand address, that is, the address where the processing result is stored.

三、RISC-VSix basic instruction formats

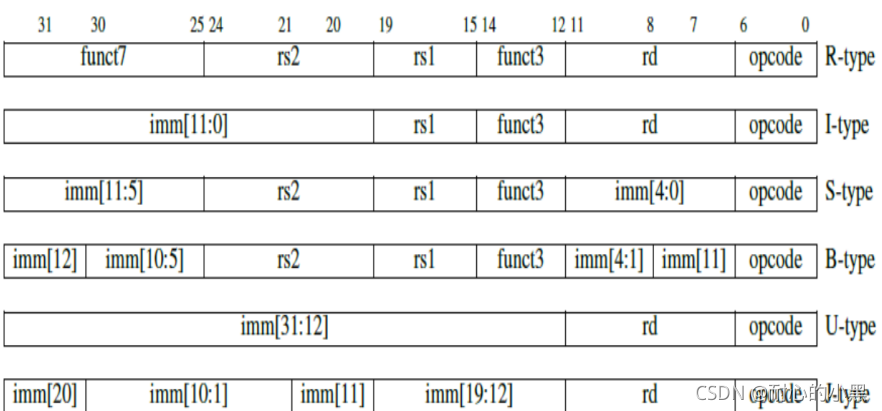

RISC-V The instruction format is a typical three-operand,7 Instruction format for bit opcodes.RISC-V Instruction set has six basic instruction format(R/I/S/B/U/J),如下图所示:

- 其中 opcode 表示 7 An instruction operation code,Its role is to distinguish between different instructions;

- funct3 表示 3 位 的功能码,funct7 表示 7 Bit function code,They can help distinguish between different kinds of instructions;

- rs1 和 rs2表示两个 5 位的源寄存器;

- rd 是 5 bit destination register,The result of the instruction operation is stored rd 中;

- imm Immediate numbers representing different lengths,Can be used directly as an operand.

6 Basic instruction format specific introduction is as follows:

1、R-typed

R-typed Instructions are the most commonly used arithmetic instructions,Has three register addresses,每个都用 5bit 的数表示.Instructions by the operation 7 位的 opcode、7 位的 funct7 以及 3 位的 funct3 共同决定的.R-typed are all integer computation instructions that do not contain immediate values,General representation register-Instructions for register manipulation.

2、I-typed

I-typed Has two register addresses and an immediate,One is the source registers rs1,一个是目的寄存器 rd,command high 12 Who is the number immediately.The operation of the instruction is only 7 位的 opcode 和 3 位的funct3两者决定.值得注意的是,When performing operations need to put first 12 An extension to immediately 32 operation after the bit.I-typed command is equivalent to R-typed One of the operands in the instruction format is changed to an immediate value.Generally means short immediate data and memory fetch load 操作的指令.

3、S-typed

S-typed The command function is given by 7 位 opcode 和 3 位 funct3 决定,The instruction contains two source registers and the instruction'simm[31:25]和 imm[11:7]构成的一个12位的立即数,When executing the instruction operation, it is necessary to put the12 An extension to immediately 32 位,然后再进行运算,S-typed The general said to fetch store 操作指令,as stored word(sw)、半字(sh)、字节(sb)等指令.

4、B-typed

B-typed By the instruction of operation 7 位 opcode 和 3 位 funct3 决定,instruction has two source registers and one 12 位的立即数,The immediate value constitutes the first32位是 imm[12]、第7位是imm[11]、25 到 30 是 imm[10:5]、8 到 11 位是 imm[4:1],同样的,When performing an operation, it is necessary to12 An extension to immediately 32 位,然后再进行运算.B-typed Generally means conditional jump operation instruction,如相等(beq)、不相等(bne)、大于等于(bge)以及小于(blt)等跳转指令.

5、U-typed

U-typed The instruction operation is only controlled by 7 位 opcode 决定,The instruction includes a destination register rd 和高20 位表示的 20 位立即数.U-typed Generally means a long immediate operation instruction,例如 lui 指令,将立即数左移 12 位,并将低 12 位置零,The result is written back to the destination register.

6、J-typed

J-typed By the instruction of operation 7 位 opcode 决定,与 U-typed There is only one destination register rd和一个 20 位的立即数,但是 20 The immediate composition of bits is different,即指令的 31 位是 imm[20]、 12 到 19 位是 imm[19:12]、20 位是 imm[11]、21 到 30 位是 imm[10:1],J-typed Generally means an unconditional jump instruction,如 jal 指令.

It can be seen from the basic instruction format,RISC-V It is a simpler instruction set architecture design with high performance and low power consumption.

- 首先,RISC-V Instruction only above 6 basic instruction format,and each instruction length is 32 位的,不像 X86-32 和 ARM-32 That has a lot of instruction format,This greatly reduces the decoding time of instructions.

- 第二,RISC-V The instruction format has three register addresses,不像 X86 That way the source and destination operands share an address,It doesn't need to use an extra move instruction to finish storing the value of the destination register.

- 第三,对于所有的 RISC-V 指令,The reading and writing need register identifier in the same location,This makes instructions before performing decoding operation,early access to register values.

- 第四,Immediate values in the instruction format are always sign-extended,and the highest bit of the instruction is the sign bit,So it is possible to perform a sign-extend operation of the immediate value before decoding.

这说明RISC-V 是优秀的、Concise instruction set architecture,因此,RISC-V Instruction set architecture will continue to evolve,Gradually become the most mainstream instruction set architecture.

四、6basic integer instruction set

RISC-V Basic integer instruction set is that each must have a specialized instruction set,It is mainly to ensure the basic functional requirements and the normal operation of all programs,以 32 The bit example is introduced as follows:

1. 算数运算指令

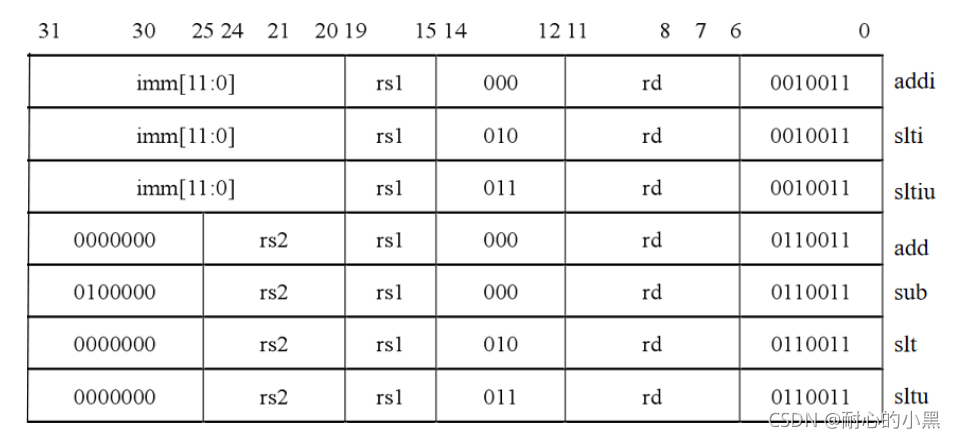

RISC-V 的 32 位基础整数指令集(RV32I)具有 7 Arithmetic operation instructions,分别是 ADDI、 SLTI、SLTIU、ADD、SUB、SLT 和 SLTU.Their command format is shown in the following figure:

Arithmetic operation instructions use two types of instruction formats,One is the register-immediate operation I-typed 指令格式,One is the register-寄存器操作的 R-typed 指令格式.Two kinds of instruction format for arithmetic operation instructions,target register rd.R-typed 是 add、sub、slt 和 sltu,I-typed 是 addi、slti和 sltiu.

addiThe function is to combine the immediate and rs1 add and write rd 中;add是将 rs1 和 rs2 相 add and write rd 中;sub是 rs1 减去 rs2 并写入 rd 中;slt 和 sltuIs signed and unsigned compare instructions,即 rs1 小于 rs2 则置 1,no set 0;slti 和 sltiu的功能是 rs1 Set if less than immediate 1,no set 0.

2. 移位指令

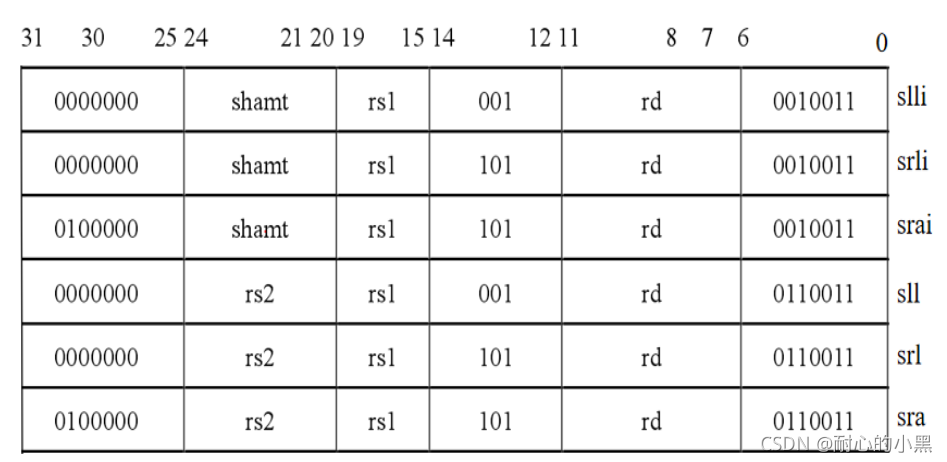

RV32I 具有 6 shift instruction,分别是 SLLI、SRLI、SRAI、SLL、SRL 和 SRA,The instruction format as shown in the figure below,其中 shamt Represents the offset, which is the shift amount.

The shift instruction is also used R-typed 和 I-typed Two command formats,R-typed 的是 sll、srl 和 sra, I-typed 的是 slli、srli 和 srai.

slliThe function is an immediate logical left shift,rs1 左移 shamt 位,Fill in the vacancy 0 并写入 rd 中;srliis an immediate logical right shift,rs1 右移 shamt 位,Fill in the vacancy 0 并写入rd 中;sraiimmediate arithmetic right shift,rs1 右移 shamt 位,Fill in the vacancy rs1 the highest bit and write rd 中;sll是逻辑左移,rs1 左移 rs2 位,Fill in the vacancy 0 并写入 rd 中;srl是逻辑右移,rs1 右移 rs2位,Fill in the vacancy 0 并写入 rd 中;sra是算数右移,rs1 右移 rs2 位,Fill in the vacancy rs1 the highest bit and write rd 中.

3. 逻辑操作指令

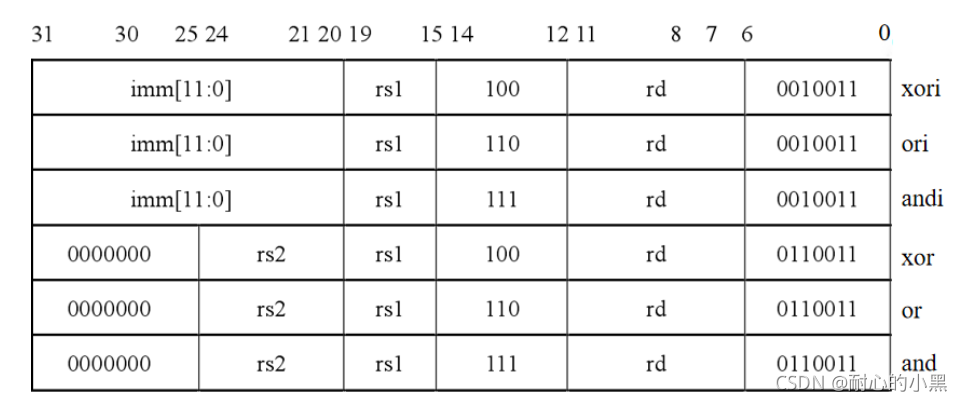

RV32I 具有 6 logical operation instructions,分别是 XORI、ORI、ANDI、XOR、OR 和 AND,The instruction format as shown in the figure below:

Logical operation instructions are also used R-typed 和 I-typed 指令格式,R-typed 为 xor、or 和 and, I-typed 为 xori、ori 和 andi.

xoriis an immediate XOR,rs1 Bitwise XOR with immediate and write rd中;ori是 rs1 bitwise OR with immediate and write rd 中;andi是 rs1 and immediate bit AND and write rd 中;xor异或,rs1 和 rs2 Bitwise XOR and write rd 中;or是 rs1 和 rs2 bitwise OR and write rd 中;and是 rs1 和 rs2 bit-and-write rd 中.

4. 加载和存储指令

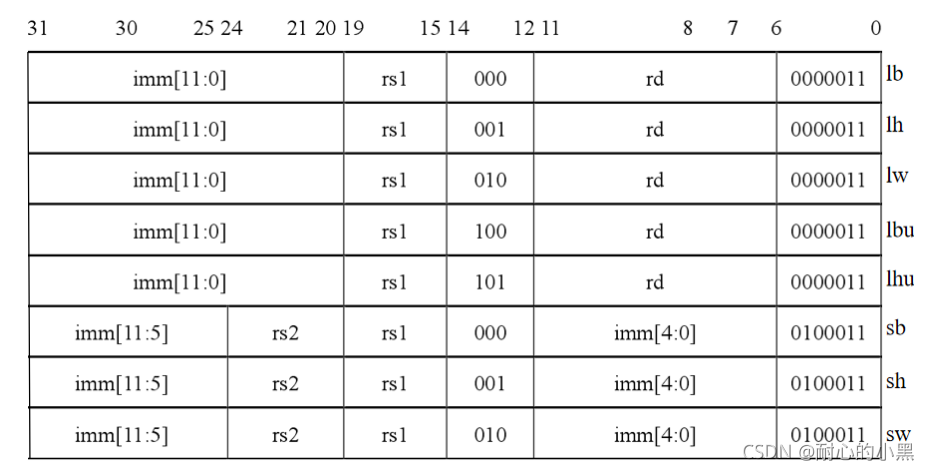

RV32I 具有 8 load and store instructions,分别是 LB、LH、LW、LBU、LHU、SB、SH 和 SW,The instruction format as shown in the figure below:

RV32I 是一个加载-存储结构,只有加载-Can access memory storage class instruction,在寄存器

data transfer to and from memory.Load class instruction is used I-typed 指令格式,storage class directive

用的是 S-typed 指令格式.

lbis a byte load,read one byte write rd 中;lhis half word loading,read two bytes write rd 中;lwis word loading,read four bytes write rd 中;lbuis an unsigned byte load,read one byte write rd 中;lhuis an unsigned halfword load,read two bytes write rd中;sbis the storage byte,把 rs2 The lower one byte of the address is stored in rs1+immediate count;shhalf-word,把 rs2The lower two bytes of the address are stored in rs1+immediate count;swis a save word,把 rs2 The lower four bytes of the address are stored in the address rs1+immediate count.

5. 控制转移指令

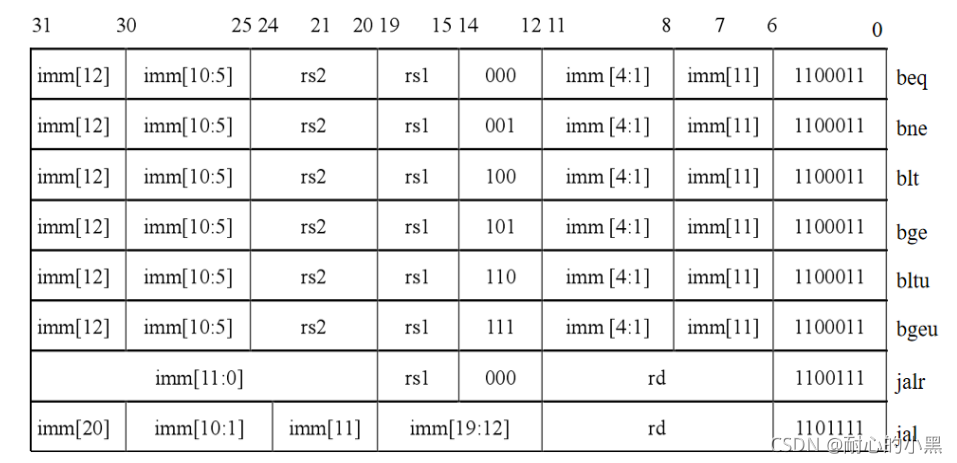

RV32I 具有 8 control transfer instruction,分别是 BEQ、BNE、BLT、BGE、BLTU、BGEU、 JAL 和 JALR,The instruction format as shown in the figure below:

Control transfer instructions are divided into two types of instructions: conditional branch jump and unconditional jump link.,Use conditional branch to jump

的是 B-typed 格式,unconditional jump jalr 和 jal 使用的分别是 I-typed 格式和 J-typed 格

式.

beqis an equality conditional branch,rs1 和 rs2 的值相等时,把 pc set the value to the current value+偏移值;bneis an unequal conditional branch,rs1 和 rs2 的值不等时,把 pc set the value to the current value+偏移值;bltis less than conditional branch,rs1 小于 rs2 的值时,把 pc set the value to the current value+偏移值;bgeis greater than or equal to conditional branch,rs1 大于等于 rs2 的值时,把 pc set the value to the current value+偏移值;bltuis an unsigned less than conditional branch;bgeuis an unsigned greater than or equal conditional branch;jalIs the jump and links,把 pc 设置成当前值+偏移值,然后将 pc+4 Stored as the address of the next instruction rd 中;jalr跳转并链接,把 pc 设置成 rs1+偏移值,然后将 pc+4 写入 rd 中.

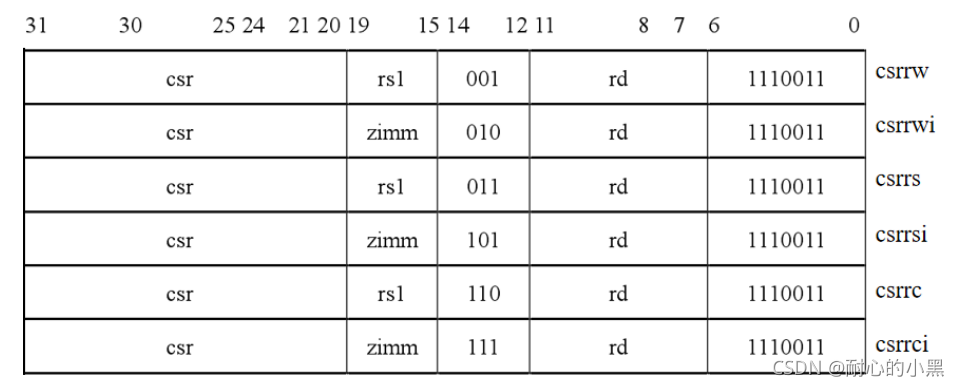

6. CSR 操作指令

RV32I 具有 6 条 CSR 操作指令,分别是 CSRRW、CSRRWI、CSRRS、CSRRSI、 CSRRC 和 CSRRCI.CSR The command format of the operation command is shown in the following figure,其中 csr 表示 CSR 寄存器的地址,zimm Represents a zero-extended immediate.

CSR Operation instructions are used I-typed 指令格式.

csrrwis the read-after-write control status register,先将 csr The value of the record为 t,把 rs1 的值写入 csr,再将 t 写入 rd 中;csrrwiIs an immediate data read and then write to the control status register,将 csr 的值写入 rd 中,Then write the immediate data csr 中;csrrsYes, the control status register is set after reading,先将 csr The value of the record为 t,让 t 和 rs1 fetch or and write csr,再将 t 写入 rd 中;csrrsiIs the immediate data set control status register after read,先将 csr The value of the record为 t,把 t 和立即数 zimm fetch or and write csr,再将 t 写入 rd 中;csrrcYes Clear Control Status Register after Read,先将 csr The value of the record 为 t,把 t 和 rs1 bit-and-write csr,再将 t 写入 rd 中;csrrciYes, clear control status register after immediate data read,csr The value of the record为 t,把 t 和立即数 zimm bit-and-write csr,再将 t 写入 rd 中.

先自我介绍一下,小编13年上师交大毕业,曾经在小公司待过,去过华为OPPO等大厂,18年进入阿里,直到现在.深知大多数初中级java工程师,想要升技能,往往是需要自己摸索成长或是报班学习,但对于培训机构动则近万元的学费,着实压力不小.自己不成体系的自学效率很低又漫长,而且容易碰到天花板技术停止不前.因此我收集了一份《java开发全套学习资料》送给大家,初衷也很简单,就是希望帮助到想自学又不知道该从何学起的朋友,同时减轻大家的负担.添加下方名片,即可获取全套学习资料哦

边栏推荐

- SQL Server 2019 installation error 0 x80004005 service there is no timely response to the start or control request a detailed solution

- Closures in JS

- 路由-嵌套路由

- Wireless vibrating wire acquisition instrument remote modification method

- [b01lers2020]Welcome to Earth-1

- Basic operations of openGauss database (super detailed)

- Oracle update误操作单表回滚

- 网络流详解(流网图一般能够反映什么信息)

- SQL Server 2014安装教程(保姆级图解教程)

- SQL中字符串拼接

猜你喜欢

随机推荐

Interpretation of new features | MySQL 8.0 GIPK invisible primary key

SQL Server 2014安装教程(保姆级图解教程)

企业用直播平台能实现什么

WeChat applet getPhoneNumber interface code=40013

你知道图论的Dijkstra吗?

C语言结构体(入门)

Closures in JS

Js scratchable latex style draw plug-in

工厂方法模式

package.json与package-lock.json

Set proxy server (Google+IE) "Recommended Collection"

pytorch模型转tensorflow模型

Wireless vibrating wire acquisition instrument remote modification method

无线振弦采集仪远程修改参数方式

js炫酷仪表盘插件

PHP伪协议详解

FreeRTOS--栈实验

Good shooting js game source code

动态组件-component

图论之Kruskal,最小生成树如何优雅解题?