当前位置:网站首页>5.PCIe官方示例

5.PCIe官方示例

2022-08-05 00:41:00 【jjinl】

官方提供3个使用PCIe的例子。第一个比较简单,我把例化参数剔除,整个文件结构如下:

module top_basic (/*AUTOARG*/

// Outputs

hdoutp, hdoutn, pll_lk, poll, l0, dl_up, usr0, usr1, usr2, usr3,

na_pll_lk, na_poll, na_l0, na_dl_up, na_usr0, na_usr1, na_usr2,

na_usr3, led_out, dp, TP,

// Inputs

rstn, FLIP_LANES, LED_INV, refclkp, refclkn, hdinp, hdinn,

dip_switch

);

....

led_status led (....); // Templated

pcie2_core pcie (..... );

ip_rx_crpr #(.c_DATA_WIDTH (c_DATA_WIDTH)) cr (....);

ip_crpr_arb crarb (.....); // Templated

UR_gen #(.c_DATA_WIDTH (c_DATA_WIDTH)) ur (.......); // Templated

ip_tx_arbiter #(.c_DATA_WIDTH (c_DATA_WIDTH)) tx_arb (.....);

wb_tlc #(.c_DATA_WIDTH(c_DATA_WIDTH)) wb_tlc (.....); // Templated

wb_arb #(.c_DATA_WIDTH(c_DATA_WIDTH),

.S0_BASE (32'h0000),

.S1_BASE (32'h4000),

.S2_BASE (32'h1000),

.S3_BASE (32'h5000))

wb_arb (.....);

wbs_gpio gpio (......); // Templated

wbs_32kebr #(.c_DATA_WIDTH(c_DATA_WIDTH),

.init_file("none"))

ebr (......); // Templated

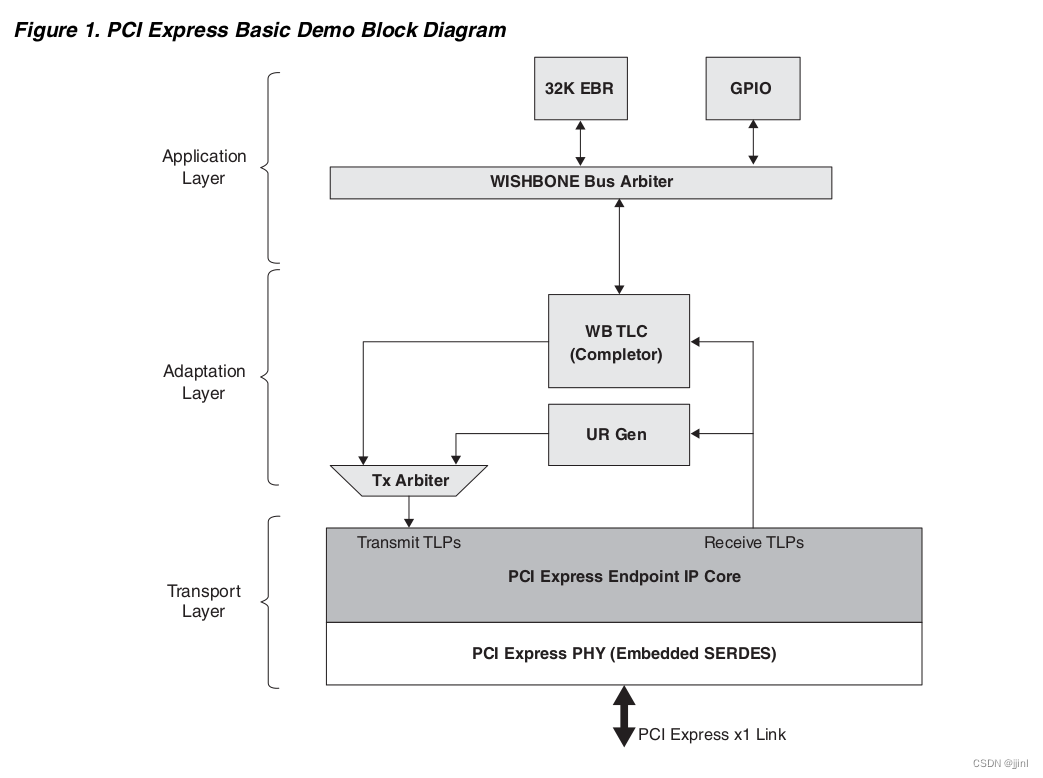

endmodule这个文件里面调用几个IP,分别是led_status、pcie2_core、ip_rx_crpr、ip_crpr_arb、UR_gen、ip_tx_arbiter、wb_tlc、wb_arb、wbs_gpio、wbs_32kebr.连接框图如下:

上图中PCIe发来的TLP包送到UR Gen模块和WB TLC模块,WB TLC接收自己感兴趣的包,并转换为wishbone总线接口,产生读写时序到wishbone总线仲裁模块wishbone bus arbiter,仲裁器根据读写数据的地址操作对应的wishbone从设备,从设备返回的数据通过wb tlc打包成tlp包,再通过tx arbiter发送到PCIe EP,之后上传到上位机。UR Gen模块在这里主要是处理wb_tlc模块不感兴趣的包,回复完成报文并标识不支持的TLP包。

先挑简单文件看看,打开Tx Arbiter文件ip_tx_arbiter.v,内容如下:

// $Id: ip_tx_arbiter.v,v 1.1.1.1 2008/07/01 17:34:22 jfreed Exp $

module ip_tx_arbiter #(parameter c_DATA_WIDTH = 64) (/*AUTOARG*/

// Outputs

tx_rdy_0, tx_rdy_1, tx_rdy_2, tx_rdy_3, tx_req, tx_dout, tx_sop,

tx_eop, tx_dwen,

// Inputs

clk, rstn, tx_val, tx_req_0, tx_din_0, tx_sop_0, tx_eop_0,

tx_dwen_0, tx_req_1, tx_din_1, tx_sop_1, tx_eop_1, tx_dwen_1,

tx_req_2, tx_din_2, tx_sop_2, tx_eop_2, tx_dwen_2, tx_req_3,

tx_din_3, tx_sop_3, tx_eop_3, tx_dwen_3, tx_rdy

);

input clk;

input rstn;

input tx_val;

input tx_req_0;

input [c_DATA_WIDTH-1:0] tx_din_0;

input tx_sop_0;

input tx_eop_0;

input tx_dwen_0;

output tx_rdy_0;

input tx_req_1;

input [c_DATA_WIDTH-1:0] tx_din_1;

input tx_sop_1;

input tx_eop_1;

input tx_dwen_1;

output tx_rdy_1;

input tx_req_2;

input [c_DATA_WIDTH-1:0] tx_din_2;

input tx_sop_2;

input tx_eop_2;

input tx_dwen_2;

output tx_rdy_2;

input tx_req_3;

input [c_DATA_WIDTH-1:0] tx_din_3;

input tx_sop_3;

input tx_eop_3;

input tx_dwen_3;

output tx_rdy_3;

output tx_req;

output [c_DATA_WIDTH-1:0] tx_dout;

output tx_sop;

output tx_eop;

output tx_dwen;

input tx_rdy;

reg tx_req;

reg [c_DATA_WIDTH-1:0] tx_dout;

reg tx_sop;

reg tx_eop;

reg tx_dwen;

reg tx_rdy_0;

reg tx_rdy_1;

reg tx_rdy_2;

reg tx_rdy_3;

reg [1:0] rr;

reg tx_rdy_p;

reg tx_rdy_p2;

always @(/*AUTOSENSE*/rr or tx_din_0 or tx_din_1 or tx_din_2

or tx_din_3 or tx_dwen_0 or tx_dwen_1 or tx_dwen_2

or tx_dwen_3 or tx_eop_0 or tx_eop_1 or tx_eop_2

or tx_eop_3 or tx_rdy or tx_req_0 or tx_req_1 or tx_req_2

or tx_req_3 or tx_sop_0 or tx_sop_1 or tx_sop_2

or tx_sop_3)

begin

case (rr)

2'b00: begin // Service 0

tx_req <= tx_req_0;

tx_dout <= tx_din_0;

tx_sop <= tx_sop_0;

tx_eop <= tx_eop_0;

tx_dwen <= tx_dwen_0;

tx_rdy_0 <= tx_rdy;

tx_rdy_3 <= 1'b0;

tx_rdy_2 <= 1'b0;

tx_rdy_1 <= 1'b0;

end

2'b01: begin // Service 1

tx_req <= tx_req_1;

tx_dout <= tx_din_1;

tx_sop <= tx_sop_1;

tx_eop <= tx_eop_1;

tx_dwen <= tx_dwen_1;

tx_rdy_1 <= tx_rdy;

tx_rdy_3 <= 1'b0;

tx_rdy_2 <= 1'b0;

tx_rdy_0 <= 1'b0;

end

2'b10: begin // Service 2

tx_req <= tx_req_2;

tx_dout <= tx_din_2;

tx_sop <= tx_sop_2;

tx_eop <= tx_eop_2;

tx_dwen <= tx_dwen_2;

tx_rdy_2 <= tx_rdy;

tx_rdy_3 <= 1'b0;

tx_rdy_1 <= 1'b0;

tx_rdy_0 <= 1'b0;

end

2'b11: begin // Service 3

tx_req <= tx_req_3;

tx_dout <= tx_din_3;

tx_sop <= tx_sop_3;

tx_eop <= tx_eop_3;

tx_dwen <= tx_dwen_3;

tx_rdy_3 <= tx_rdy;

tx_rdy_2 <= 1'b0;

tx_rdy_1 <= 1'b0;

tx_rdy_0 <= 1'b0;

end

default: begin

end

endcase

end // always @ (...

// mux control

always @(posedge clk or negedge rstn)

begin

if (~rstn) begin

rr <= 2'b00;

tx_rdy_p <= 1'b0;

tx_rdy_p2 <= 1'b0;

end

else begin

tx_rdy_p <= tx_rdy; // use pipe of tx_rdy to account for getting the tx_end through

tx_rdy_p2 <= tx_rdy_p;

if (tx_val && ~tx_rdy_p2 && ~tx_rdy_p && ~tx_rdy) begin

if (tx_req_0 && ~tx_req) rr <= 2'b00;

else if (tx_req_1 && ~tx_req) rr <= 2'b01;

else if (tx_req_2 && ~tx_req) rr <= 2'b10;

else if (tx_req_3 && ~tx_req) rr <= 2'b11;

end

end // else: !if(~rstn)

end // always @ (posedge clk or negedge rstn)

endmodule

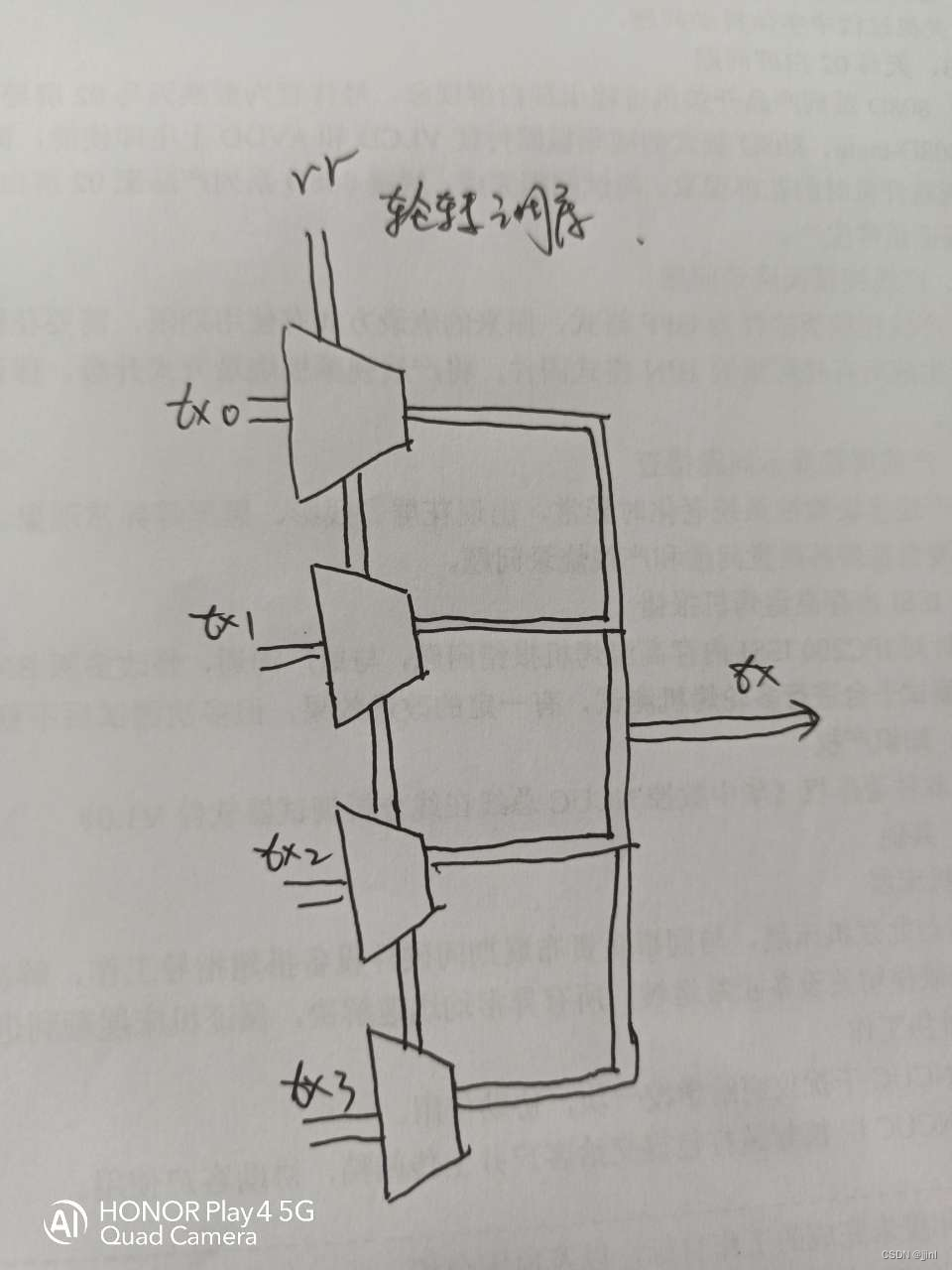

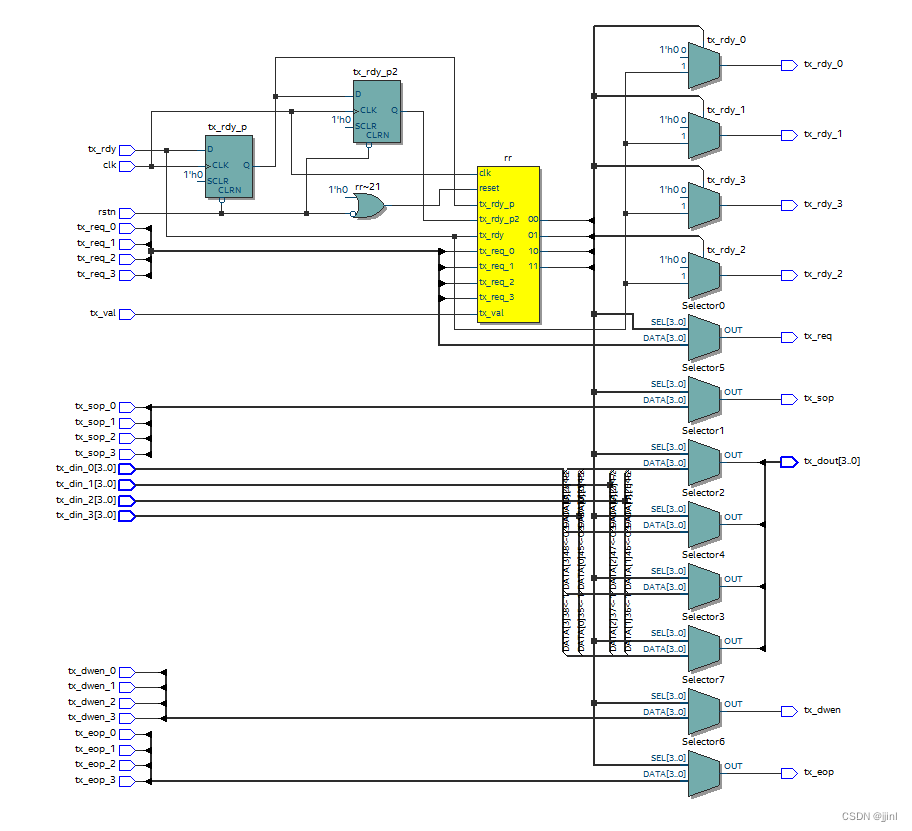

这个文件实现4选一输出的功能

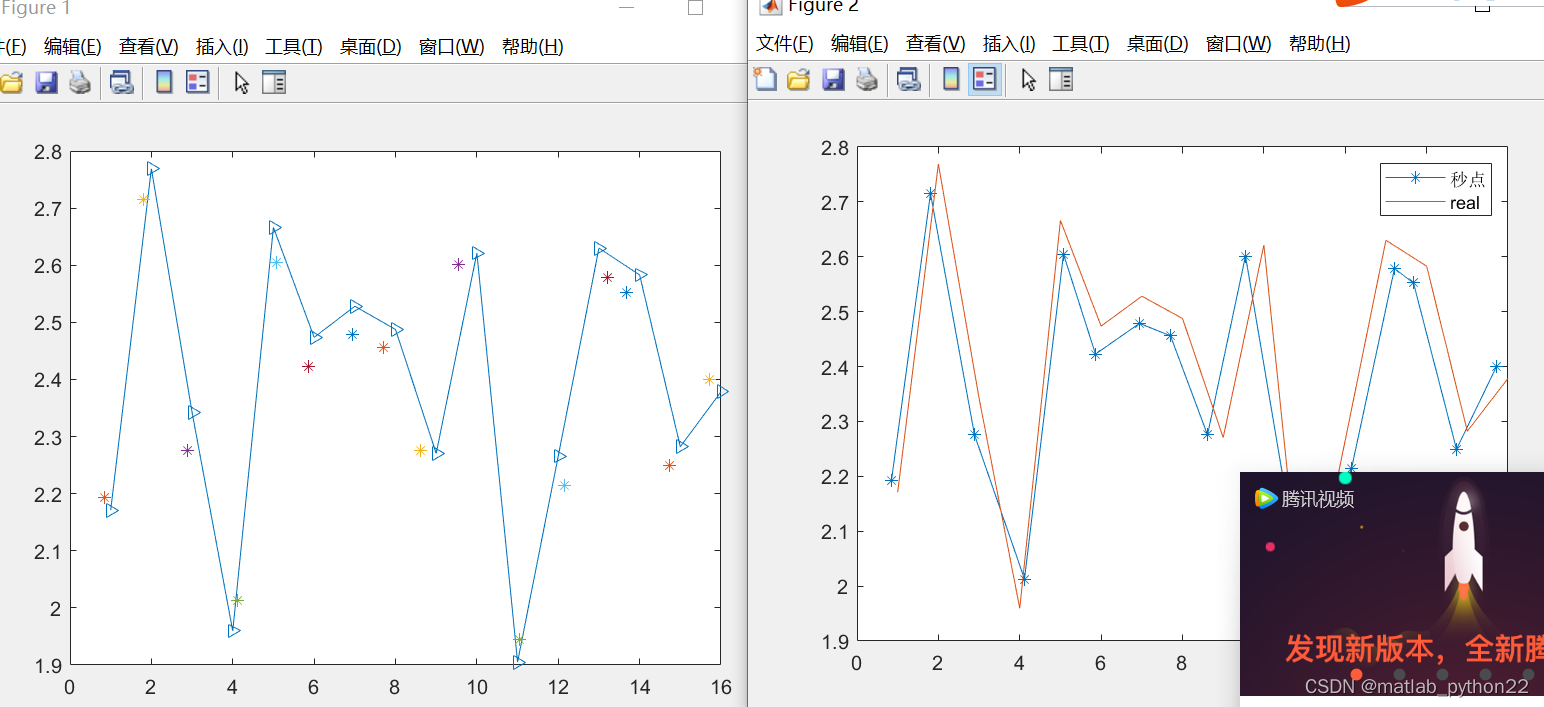

本来想使用综合工具 查看RTL,生成的RTL太复杂,我把总线宽度从64改为4后生成RTL视图如下:

边栏推荐

猜你喜欢

QSunSync Qiniu cloud file synchronization tool, batch upload

![[230]连接Redis后执行命令错误 MISCONF Redis is configured to save RDB snapshots](/img/fa/5bdc81b1ebfc22d31f42da34427f3e.png)

[230]连接Redis后执行命令错误 MISCONF Redis is configured to save RDB snapshots

2 用D435i运行VINS-fusion

电子行业MES管理系统的主要功能与用途

Matlab uses plotting method for data simulation and simulation

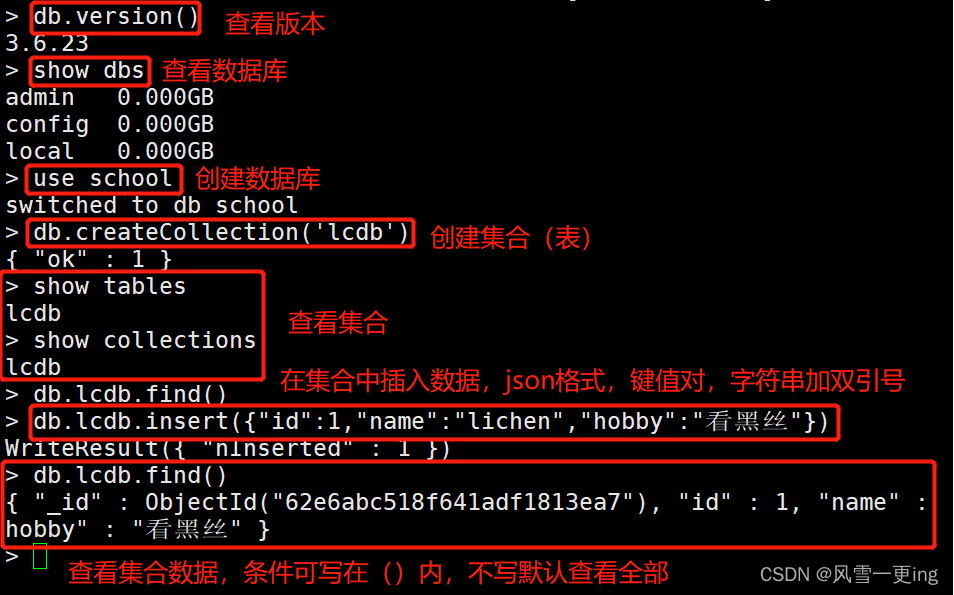

MongoDB搭建及基础操作

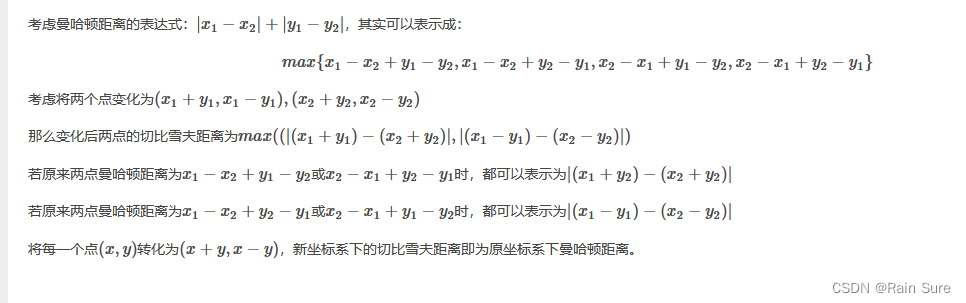

2022杭电多校第三场 K题 Taxi

![[230] Execute command error after connecting to Redis MISCONF Redis is configured to save RDB snapshots](/img/fa/5bdc81b1ebfc22d31f42da34427f3e.png)

[230] Execute command error after connecting to Redis MISCONF Redis is configured to save RDB snapshots

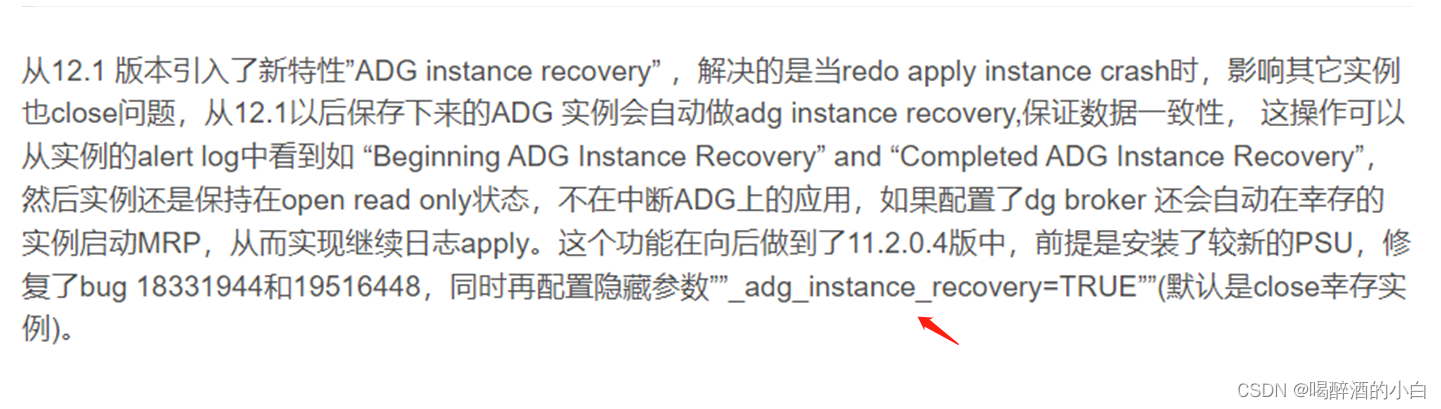

ora-01105 ora-03175

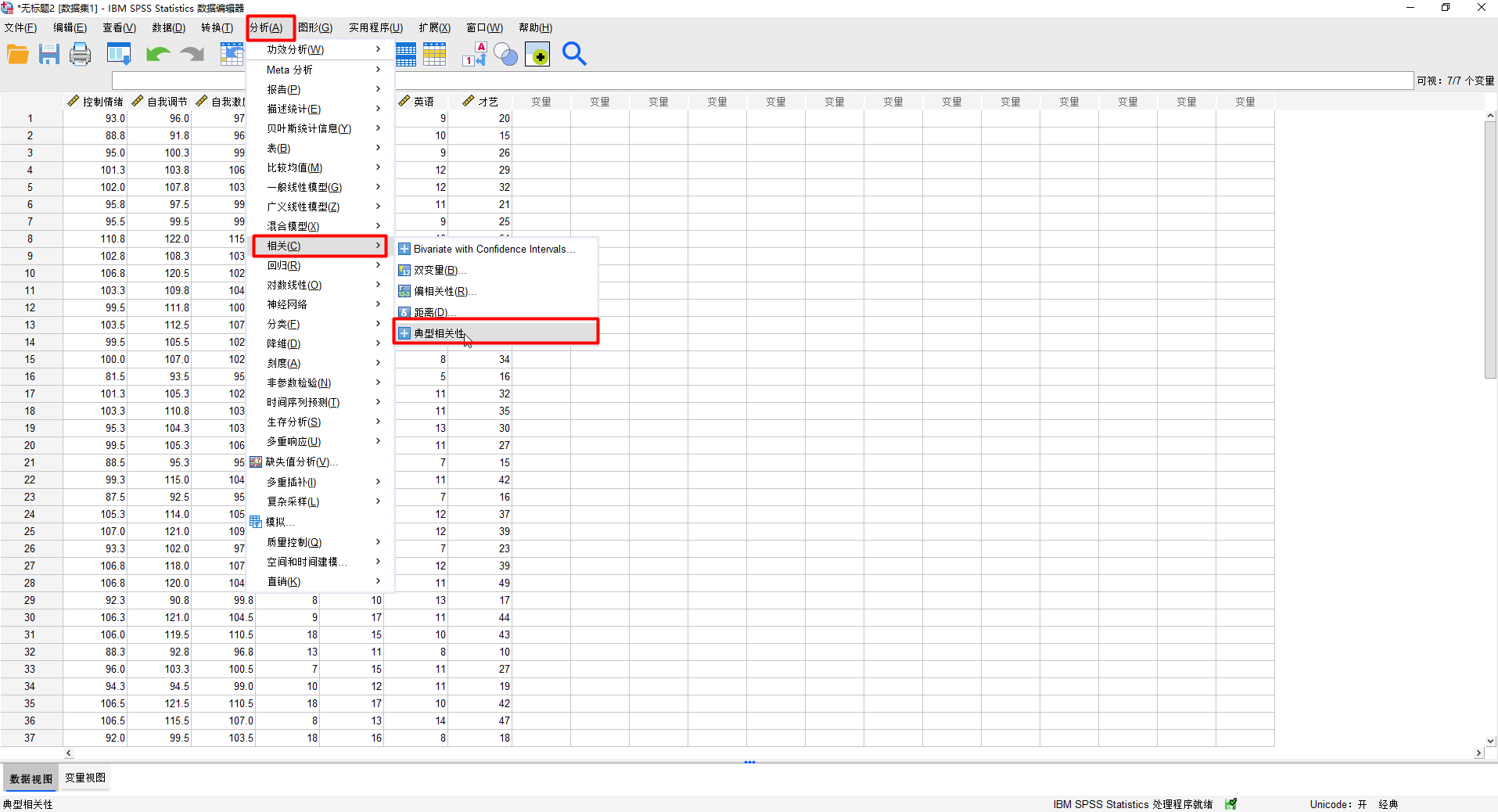

典型相关分析CCA计算过程

随机推荐

The method of freely controlling concurrency in the sync package in GO

数据类型-整型(C语言)

Software testing interview questions: test life cycle, the test process is divided into several stages, and the meaning of each stage and the method used?

tiup update

2022杭电多校第三场 L题 Two Permutations

【unity编译器扩展之模型动画拷贝】

TinyMCE disable escape

2022 Nioke Multi-School Training Session 2 J Question Link with Arithmetic Progression

软件测试面试题:关于自动化测试工具?

2022 Hangzhou Electric Multi-School 1004 Ball

Software testing interview questions: the difference and connection between black box testing, white box testing, and unit testing, integration testing, system testing, and acceptance testing?

tensor.nozero(),面具,面具

软件测试面试题:负载测试、容量测试、强度测试的区别?

Software testing interview questions: What are the seven-layer network protocols?

Mysql_14 存储引擎

leetcode:266. 回文全排列

2022杭电多校 第三场 B题 Boss Rush

2022 Hangzhou Electric Power Multi-School Session 3 Question L Two Permutations

日志(logging模块)

Theory of Software Fundamentals