当前位置:网站首页>Haute performance et faible puissance Cortex - A53 Core Board | i.mx8m mini

Haute performance et faible puissance Cortex - A53 Core Board | i.mx8m mini

2022-07-02 03:27:00 【Wuhan Vientiane aoke】

Basé sur NXP i.MX8M MiniQuatre noyaux64Conception du processeur de bits,Fréquence principale la plus élevée1.8GHz,ARM Cortex -A53Architecture,Intégration2GBOu4GB LPDDR4;CPUAdopter des14nmProcessus,Assurer une gestion plus efficace de l'énergie,Prise en charge de la conception sans ventilateur;Pour la reconnaissance d'images、Traitement audio et vidéo、Réseau de véhicules、Internet des objets、Publicité multimédia、Smart City、Applications telles que le contrôle industriel et l'interaction homme - machine.

Cortex-M4Nucléaire | Garantie de mission en temps réel

Intégration des processeursCortex-M4Noyau,Fréquence principale jusqu'à400MHz,M4AvecCortex-A53MéridienAHBCommunication par bus,Traitement des tâches en temps réel,Peut également répondre aux applications de scénarios de consommation d'énergie(ContrôleA53Sommeil et réveil du noyau).

Riche ressource multimédia

GPUSoutienOpenGL ES2.0、OpenVG1.1,Soutien3D、1080PAffichage HD、H.265Décodage du matériel vidéo、 H.264Codage du matériel vidéo, SoutienMIPI-DSI、MIPI-CSI,SoutienIIS、AC97、TDM、PDM、SPDIF,SoutienLVDSAvecRGB Afficher les extensions d'interface , Prise en charge de l'extension de l'écran tactile

Android | Ubuntu | YoctoSystèmes multiples

SoutienAndroid、Ubuntu、YoctoSystèmes multiples,Riche en ressources logicielles, Soutenir le développement d'applications diversifiées ; Nouvelle version du système d'exploitation et UI Le cadre offre une plus grande sécurité et une expérience d'interaction homme - ordinateur plus cool pour vos produits , Il est pratique pour l'étude de bureau 、Jeux et divertissements、Développement de logiciels、Mise en oeuvre du projet……

Interface de données haute vitesse | Riches ressources fonctionnelles

Réseau intégré Gigabit 、PCIe2.0、SDIO3.0Interface isovitesse,Soutien4RouteUART(Jusqu'à5Mbps)、USB2.0、IIC、SPI、PWM、GPIOAttendez..

CAN-busInterface

NXP i.MX8M Mini Le processeur ne supporte pas CAN-bus, Pour satisfaire l'industrie 、À bord、Surveillance des incendies、 Le métro et d'autres projets CAN Exigences relatives à la fonctionnalité du bus , Vientiane offre 2RouteCAN-busPlan d'expansion, Et soutenir les tests d'évaluation .

Connecteur Seiko

Le module de base adopte HRSDouble rangée80P Connecteur plaque - à - plaque plaqué or ,DF12Série, Conception unique de contact shrapnel , Stabilité structurelle 、Résistance à l'oxydation、 Plus résistant à la corrosion ,Ductilité、Conductivité électrique、 La transmission de signaux à grande vitesse est plus efficace , Soutenir l'utilisation de l'environnement vibratoire à bord .

Taille minimale

Taille du module central seulement 55mmx45mm, Plateau de commodité / Conception de la disposition et miniaturisation du plancher d'interface .

Paramètres matériels

Tableau d'évaluation fonctionnel complet

Le module de base est équipé d'un tableau d'évaluation entièrement fonctionnel , Soutien2Route Gigabit port、 2RouteCAN-bus、 2RouteRS-485、 2RouteRS-232、TTLDébogage du port série、 2RouteUSB Host、 USB Device Interface、 4GInterface(Y comprisSIMCircuit de carte)、 MIPI-CSI Connecteur de caméra、 Interface LCD et écran tactile 、GPIOInterface、Interface audio I / o、Wi-Fi、 TFConnecteur de carte、 RTC、 Buzzer、LEDAttendez..

边栏推荐

- Just a few simple steps - start playing wechat applet

- Comment élaborer une stratégie nuageuse à l'ère des nuages mixtes

- Exchange rate query interface

- Failed to upgrade schema, error: “file does not exist

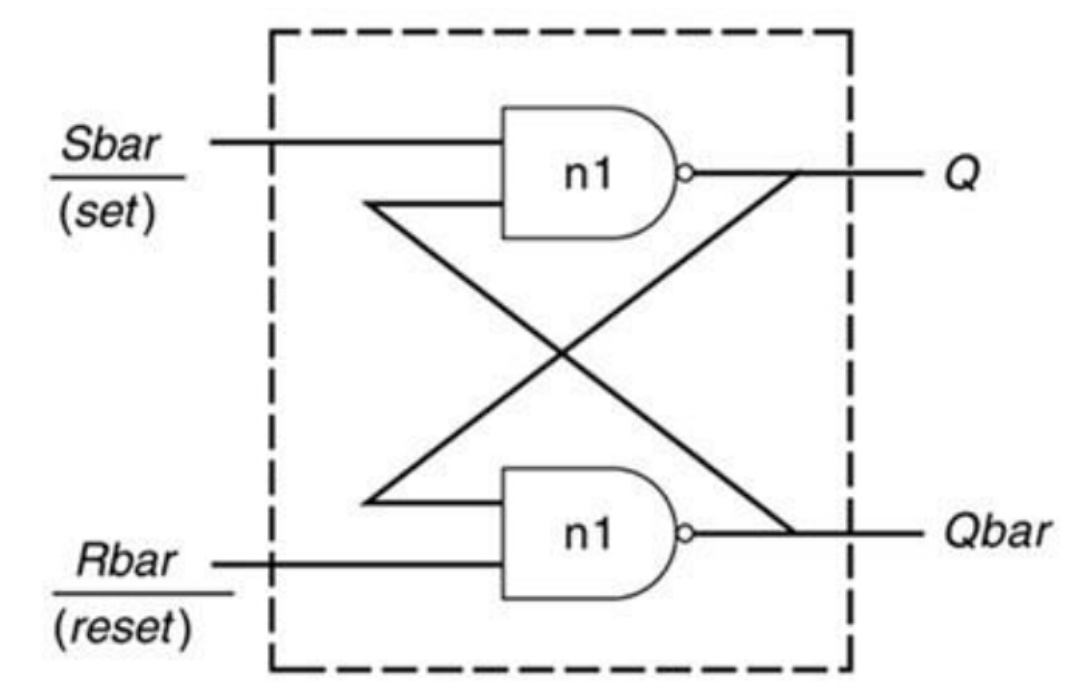

- 竞争与冒险 毛刺

- Qualcomm platform WiFi -- Native crash caused by WiFi

- Global and Chinese market of X-ray detectors 2022-2028: Research Report on technology, participants, trends, market size and share

- Kotlin基础学习 17

- Grpc快速实践

- 命名块 verilog

猜你喜欢

How to establish its own NFT market platform in 2022

Verilog 避免 Latch

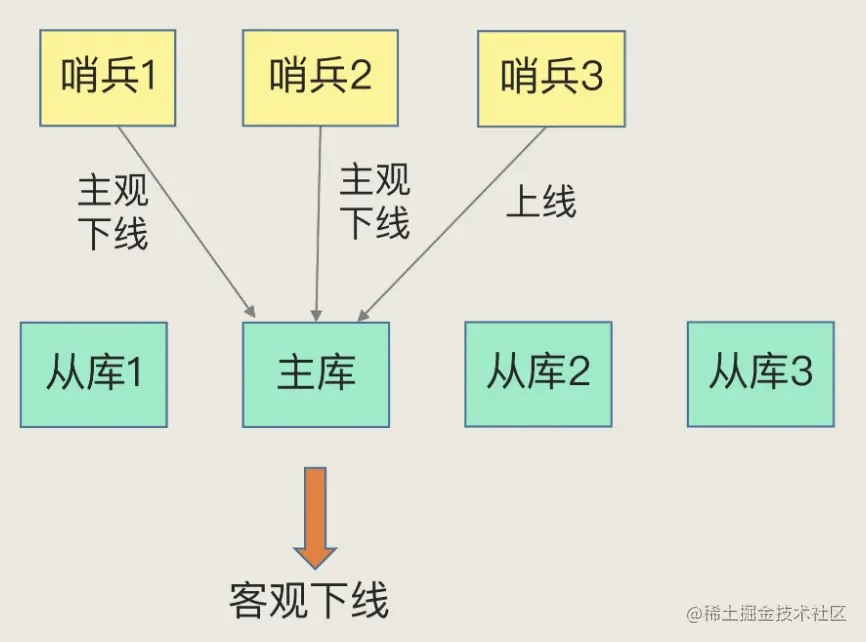

On redis (II) -- cluster version

《MATLAB 神经网络43个案例分析》:第42章 并行运算与神经网络——基于CPU/GPU的并行神经网络运算

Analyse de 43 cas de réseaux neuronaux MATLAB: Chapitre 42 opérations parallèles et réseaux neuronaux - - opérations parallèles de réseaux neuronaux basées sur CPU / GPU

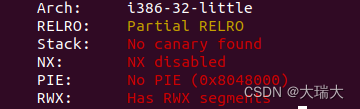

Learn PWN from CTF wiki - ret2shellcode

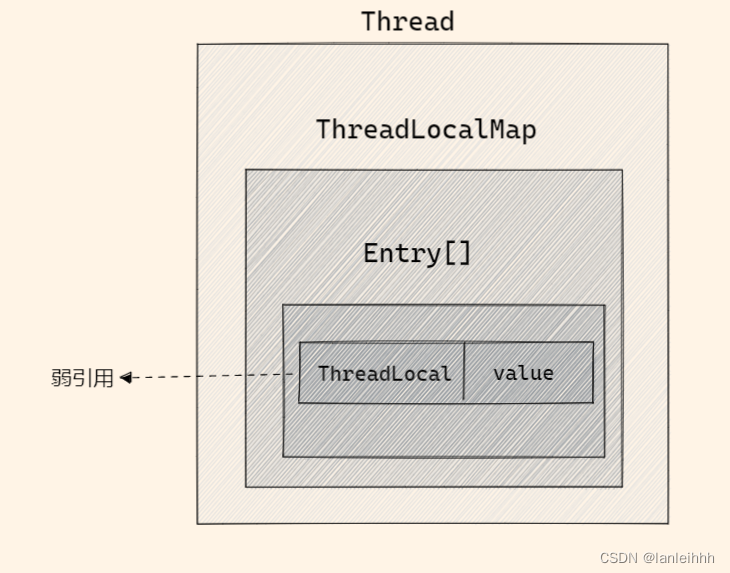

Detailed explanation of ThreadLocal

Form custom verification rules

Retrofit's callback hell is really vulnerable in kotlin synergy mode

数据传输中的成帧

随机推荐

js生成随机数

Kotlin基础学习 15

aaaaaaaaaaaaa

微信小程序中 在xwml 中使用外部引入的 js进行判断计算

Kotlin basic learning 13

Custom classloader that breaks parental delegation

[数据库]JDBC

One of the future trends of SAP ui5: embrace typescript

ORA-01547、ORA-01194、ORA-01110

GSE104154_scRNA-seq_fibrotic MC_bleomycin/normalized AM3

焱融看 | 混合雲時代下,如何制定多雲策略

3048. Number of words

Screenshot literacy tool download and use

Form custom verification rules

Eight steps of agile development process

Yan Rong looks at how to formulate a multi cloud strategy in the era of hybrid cloud

/silicosis/geo/GSE184854_ scRNA-seq_ mouse_ lung_ ccr2/GSE184854_ RAW/GSM5598265_ matrix_ inflection_ demult

Verilog parallel block implementation

Pycharm2021 delete the package warehouse list you added

Large screen visualization from bronze to the advanced king, you only need a "component reuse"!