当前位置:网站首页>硬件描述语言Verilog HDL学习笔记之模块介绍

硬件描述语言Verilog HDL学习笔记之模块介绍

2022-08-04 05:32:00 【久违de约定】

前言

其实很早以前我就学习过一段时间Verilog语言,但是由于一些语言搁置了很久,最近重新捡起来,发现以前还是走了很多弯路的。首先是学习这门语言的软硬件基础问题,现在回忆当初学习的时候,其实很多有关软硬件我在现在看来很常见的知识,我是真不知道。而如今在我看来,学习这们语言之前,对于计算机专业的学生,数电和计算机组成原理的学习是很有必要,真的很重要,在学习这两门课程后,才能对计算机有一个总体的架构。同样,还需要学习一些单片机方面的知识。

一、模块介绍

模块(module)是 Verilog 的基本描述单位,是用于描述某个设计的功能或结构及与其他模块 通信的外部端口。

模块在概念上可等同一个器件,就如调用通用器件(与门、三态门等)或通用宏单元(计数器、 ALU、CPU)等。因此,一个模块可在另一个模块中调用,一个电路设计可由多个模块组合而成。一 个模块的设计只是一个系统设计中的某个层次设计,模块设计可采用多种建模方式。 Verilog 的基本设计单元是“模块”。采用模块化的设计使系统看起来更有条理也便于仿真和测试, 因此整个项目的设计思想就是模块套模块,自顶向下依次展开。在一个工程的设计里,每个模块实现 特定的功能,模块间可进行层次的嵌套。对大型的数字电路进行设计时,可以将其分割成大小不一的 小模块,每个小模块实现特定的功能,最后通过由顶层模块调用子模块的方式来实现整体功能,这就 是 Top-Down 的设计思想。模块是 Verilog 的基本描述单位, 用于描述每个设计的功能和结构,以及其他模块通信的外部接口。

模块有五个主要部分:端口定义、参数定义(可选)、 I/O 说明、内部信号声明、功能定义。 模块总是以关键词 module 开始,以关键词 endmodule 结尾。

//端口定义

module module_name

( clk , //端口 1,时钟

rst_n , //端口 2,复位

dout //其他信号,如 dout

);

//参数定义(可选)

parameter DATA_W = 8;

//I/O说明

input clk ; //输入信号定义

input rst_n ; //输入信号定义

output[DATA_W-1:0] dout; //输出信号定义

//信号说明

reg [DATA_W-1:0] dout; //信号类型 (reg、wire)定义

reg signal1;//信号类型 (reg、wire)定义

//功能定义

//……………以下为描述功能部分…………//

//组合逻辑写法

[email protected](*)begin

end

//时序逻辑写法

[email protected](posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

end

else begin

end

end

endmodule下面详细分析一下这段代码:

二、模块名和端口定义

第 2 至 6 行声明了模块的名字和输入输出口。其格式如下:

module 模块名(端口 1,端口 2,端口 3,……);

其中模块是以 module 开始,以 endmodule 结束。模块名是模块唯一的标识符,一般建议模块名 尽量用能够描述其功能的名字来命名,并且模块名和文件名相同。

模块的端口表示的是模块的输入和输出口名,也是其与其他模块联系端口的标识。

三、参数定义

第 9 行参数定义是将常量用符号代替以增加代码可读性和可修改性。这是一个可选择的语句, 用不到的情况下可以省略,参数定义一般格式如下:

parameter DATA_W = x;

四、接口定义

第 12 至 14 行是 I/O(输入/输出)说明,模块的端口可以是输入端口、输出端口或双向端口。其说明格式如下。

输入端口: input [信号位宽-1 : 0] 端口名 1;

input [信号位宽-1 : 0] 端口名 2;

……;

输出端口: output [信号位宽-1 : 0] 端口名 1;

output [信号位宽-1 : 0] 端口名 2;

……;

双向端口: inout [信号位宽-1 : 0] 端口名 1;

inout [信号位宽-1 : 0] 端口名 2;

……;

五、信号类型

第 17 至 18 行定义了信号的类型。这些信号是在模块内使用到的信号,并且与端口有关的 wire 和 reg 类型变量。其声明方式如下:

reg [width-1 : 0] R 变量 1, R 变量 2 ……;

wire [width-1 : 0] W 变量 1,W 变量 2……;

如果没有定义信号类型,默认是 wire 型,并且信号位宽为 1。

六、功能描述

第 23 至 32 行是功能描述部分。模块中最重要的部分是逻辑功能定义部分,有三种方法可在模块中产生逻辑。

1. 用“assign”声明语句,如描述一个两输入与门:assign a = b & c。下次仔细写一下。

2. 用“always”块。即前面介绍的时序逻辑和组合逻辑。

3. 模块例化。详细功能见下文“模块例化”。

七、模块例化

对数字系统的设计一般采用的是自顶向下的设计方式,可将系统划分成几个功能模块,每个功能 模块再划分成下一层的子模块。每个模块的设计对应一个 module ,每个 module 设计成一个 Verilo g HDL 程序文件。因此,对一个系统的顶层模块采用结构化设计,即顶层模块分别调用了各个功能 模块。

一个模块能够在另外一个模块中被引用,这样就建立了描述的层次。模块实例化语句形式如下:

module_nameinstance_name(port_associations);信号端口可以通过位置或名称关联,但是关联方式不能够混合使用。端口关联形式如下:

port_expr / /通过位置。

.PortName (port_expr) / /通过名称。

module and (C, A, B);

input A,B;

output C;

//省略

endmodule

//在下面的“and_2”块中对上一模块“and”进行例化,可以有两种方式:

module and_2(xxxxx)

...

//方式一:实例化时采用位置关联,T3 对应输出端口 C,A 对应 A,B 对应 B。

and A1 (T3, A, B );

//方式二:实例化时采用名字关联,.C 是 and 器件的端口,其与信号 T3 相连

and A2(

.C(T3),

.A(A),

.B(B));

…

endmodule;

建议:在例化的端口映射中请采用名字关联,这样,当被调用的模块管脚改变时不易出错。 在实例化中,可能有些管脚没用到,可在映射中采用空白处理,如:

DFF d1 (

.Q(QS),

.Qbar (), // 该管脚悬空

.Data (D ),

.Preset (), // 该管脚悬空

.Clock (CK)); //名称对应方式。输入管脚悬空端口的输入为高阻 Z,由于输出管脚是被悬空的,该输出管脚废弃不用。

边栏推荐

猜你喜欢

随机推荐

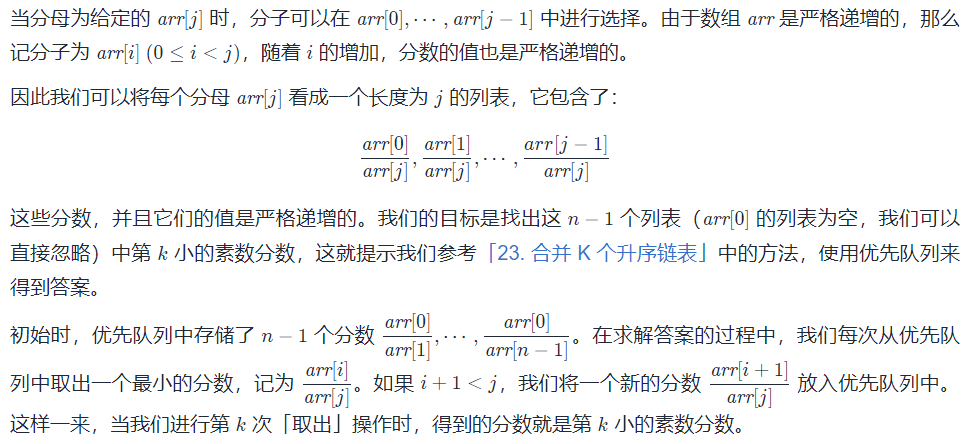

LeetCode_22_Apr_2nd_Week

CAS无锁队列的实现

Shell基础

动态内存管理-C语言

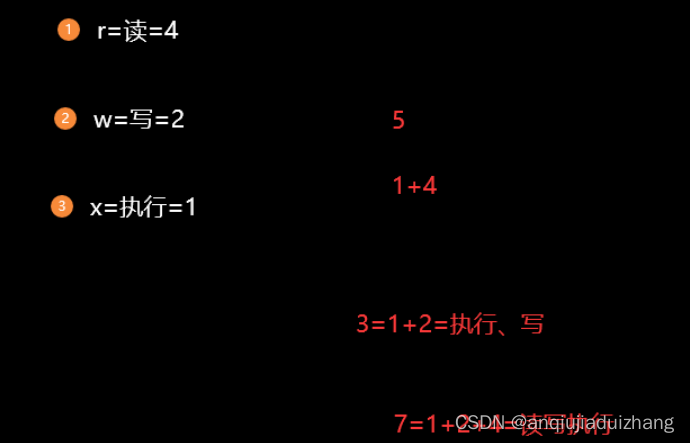

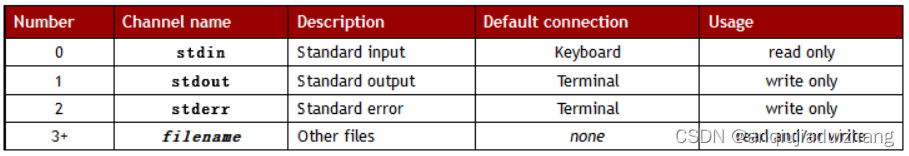

管道重定向

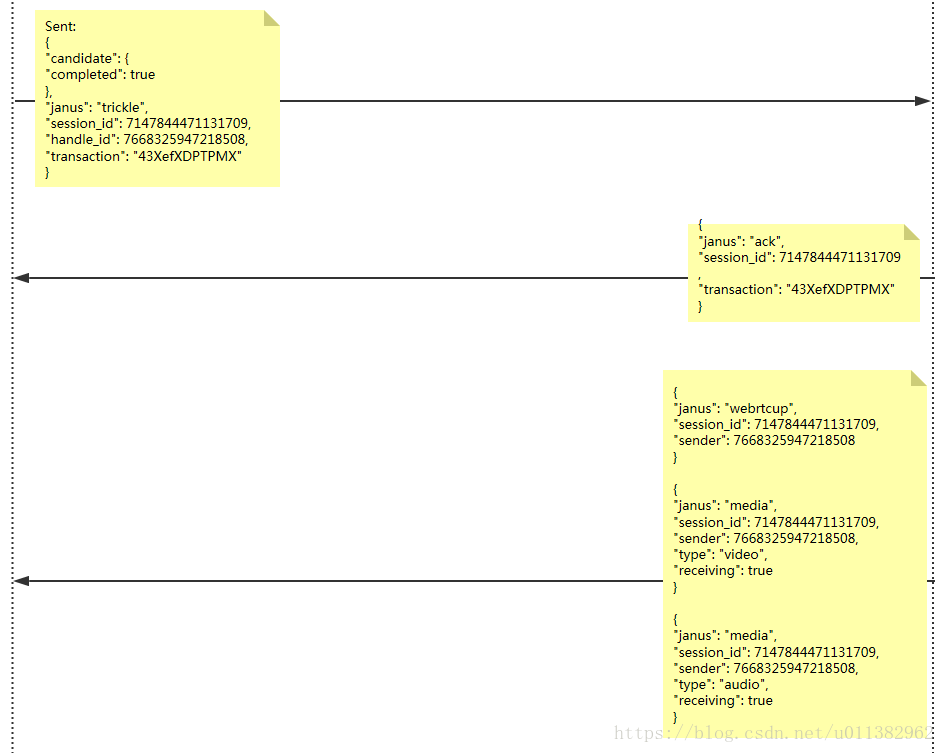

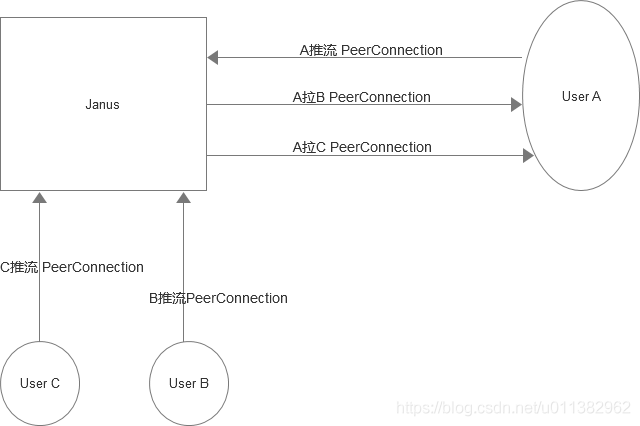

Janus转发丢包导致音视频不同步原因分析

树和二叉树

JDBC第一学之进行数据库连接时出现The server time zone.....解决办法

webrtc代码解读二:音视频播放同步过程

IDEA创建Servlet步骤

基于Webrtc和Janus的多人视频会议系统开发4 - 改造信令交互系统完成sdp交换过程

JUC并发容器——阻塞队列

【C语言】数组名是什么

strlen 转义字符

基于Webrtc和Janus的多人视频会议系统开发5 - 发布媒体流到Janus服务器

IEEE802.X protocol suite

通过socks5代理下载webrtc源码错误:curl: (7) Can't complete SOCKS5 connection xx.xx.xx.xx

tmux概念和使用

【HIT-SC-MEMO7】哈工大2022软件构造 复习笔记7

基于语音识别的QT设计的csgo互动类视频游戏