当前位置:网站首页>4. PCIe interface timing

4. PCIe interface timing

2022-08-05 00:45:00 【jjinl】

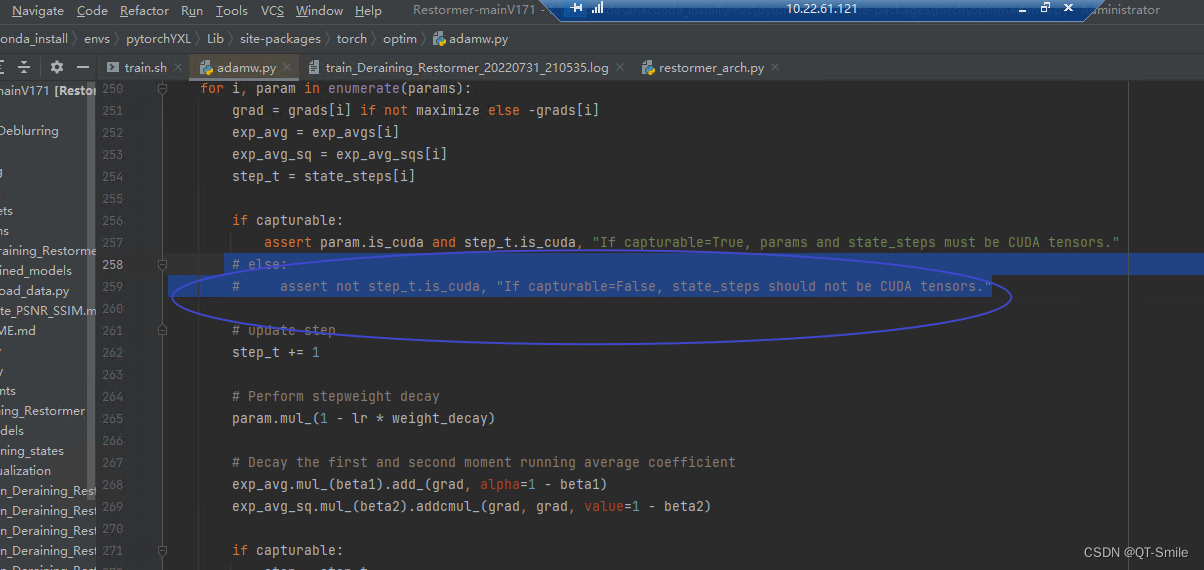

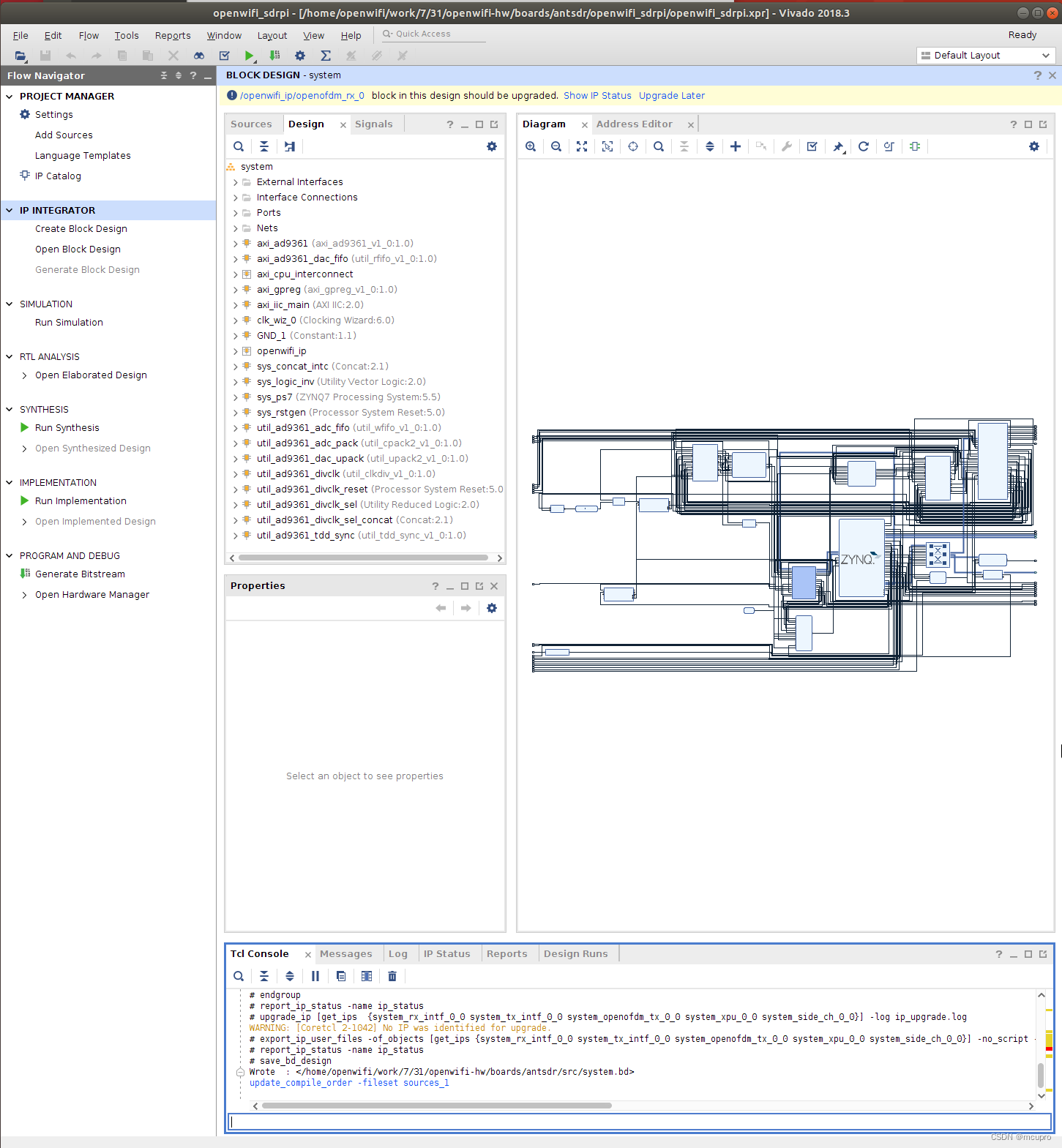

In the previous article, I briefly introduced the IPcore interface.In general, the interface is as shown below

Data is received and sent through transmit TLP interface and Receive TLP interface.The timing of sending and receiving data only describes the relationship between these interfaces.Take the interface timing of PCIe x1 from the manual

Data sending

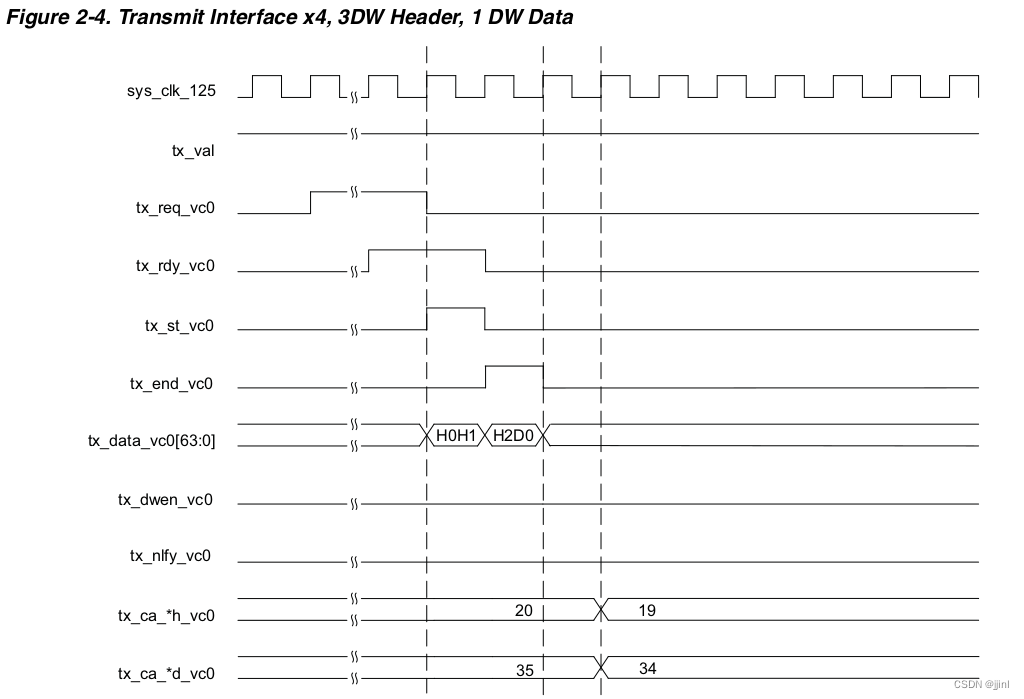

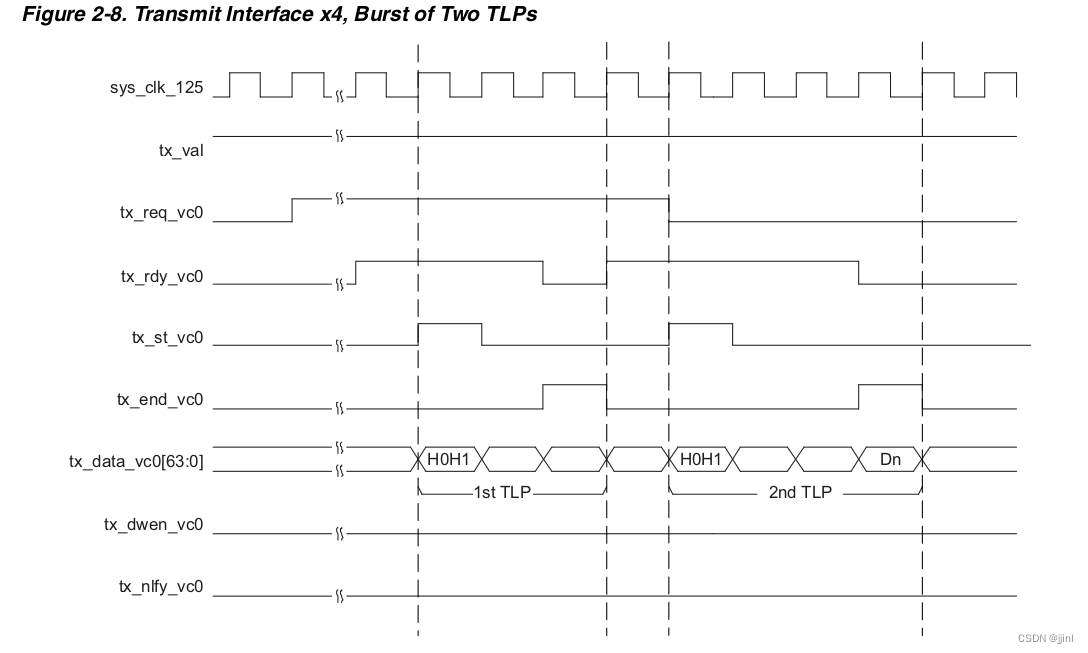

The picture above is the x4 interface. The 5G IP we use, the timing is similar to this, but the tx_val will be valid at intervals.The above timing

Before EP sends data, first send tx_req_vc0 high, indicating request to send, wait for tx_rdy_vc0 to be high to start sending, when tx_rdy_vc0 is high, place data on yx_data_vc0 on the rising edge of the next clock, and pull high tx_st_vc0 signal. tx_rdy_vc0 remains high until the last data of the TLP packet, so this tx_rdy_vc0 signal can be used as a read enable signal for non-pipeline fifo.

tx_end_vc0, indicating that the data line is the last data of TLP.

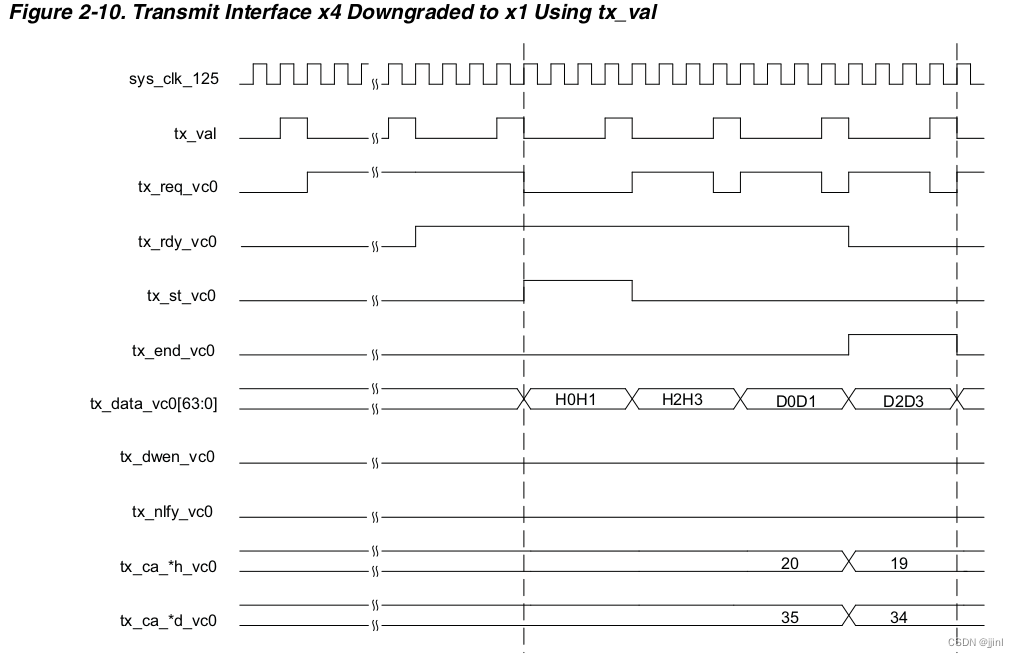

tx_ca_*h_vc0 and tx_ca_*d_vc0 must be checked before each request is sent, and the corresponding value will be decremented by one after the transmission is completed. These two types of flags indicate whether the upper port has resources to forward your sent data

The above picture is the timing of sending two data

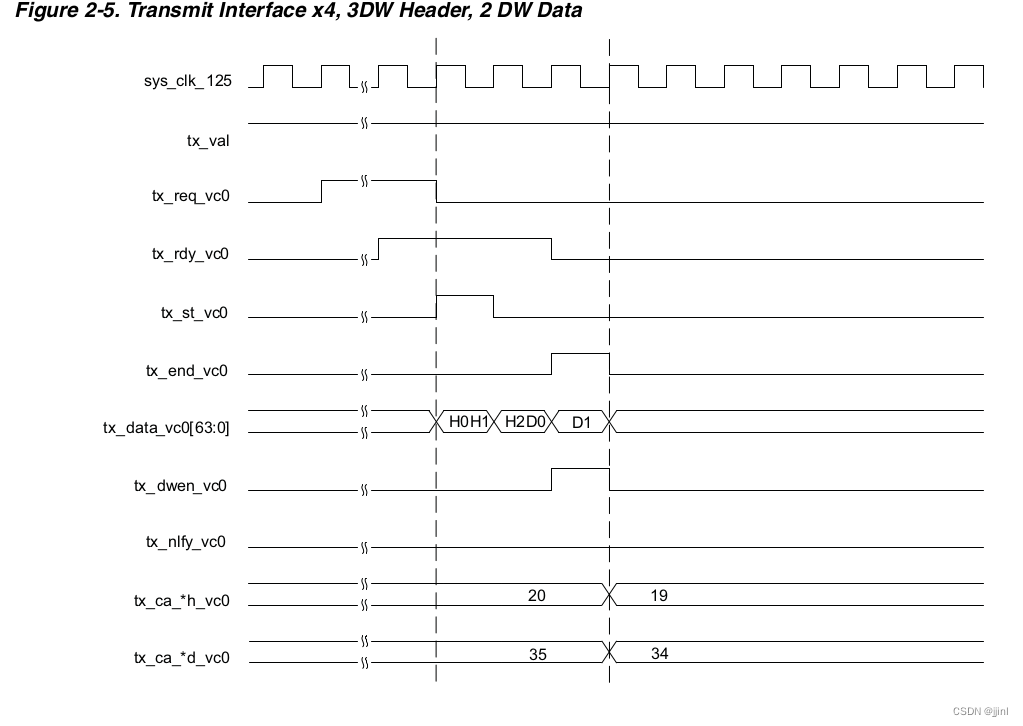

The sending timing of the above picture is only the header, there is no data corresponding to tx_ca_*d_vc0 and there is no change

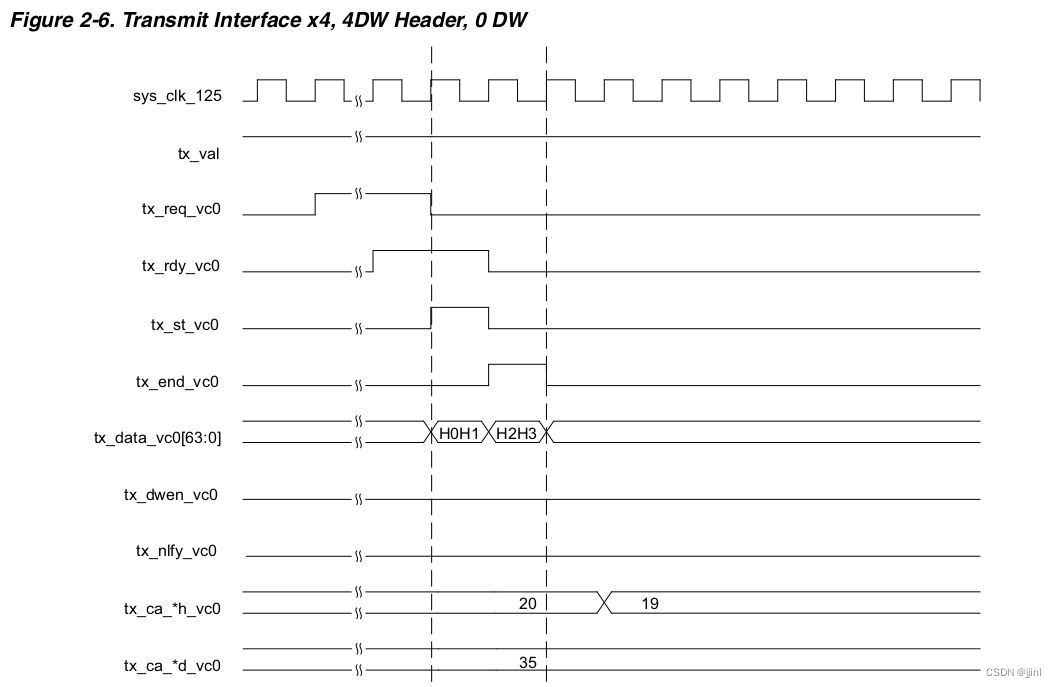

The last data sent in the above picture is not enough 64bit, at this time the dwen signal indicates that 63:32bit is valid

Burst mode, send two TLP packets, the req signal remains valid until the last TLP packet sends the rdy signal

Void the TLP packet, pull the tx_nlfy signal high at any time, void this TLP packet, no need to send the tx_end signal again

When the x4 in the above figure is downgraded to x1, the sequence diagram is the same as above. The x1 used in our project is the same as above.In this figure, when tx_val is high, the signal changes

Data reception

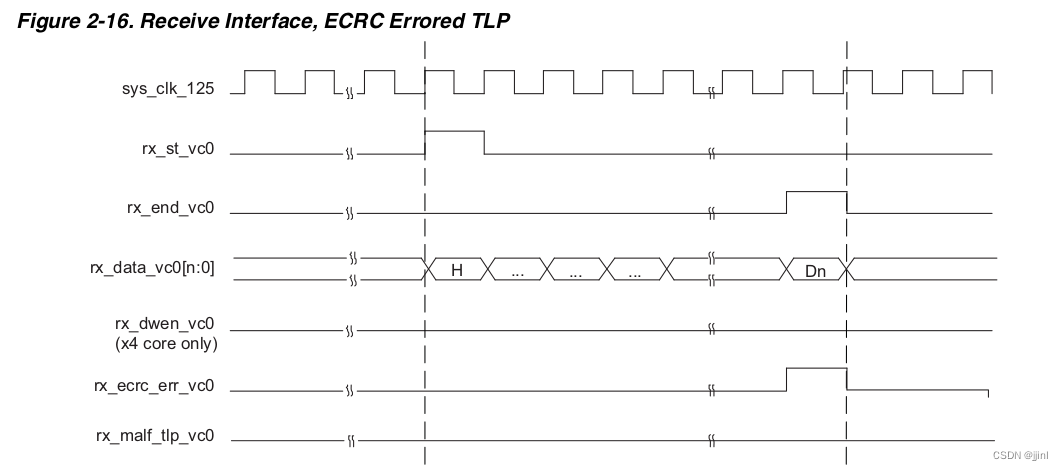

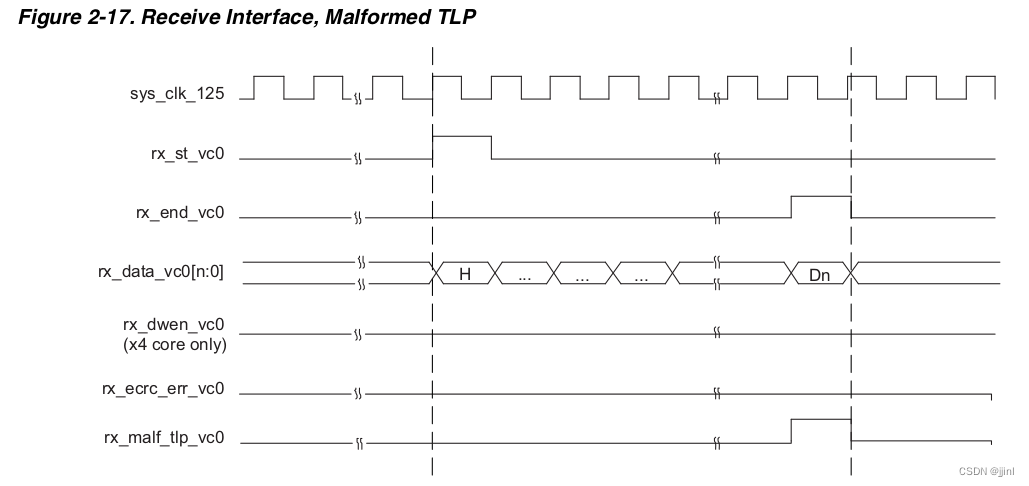

When a TLP data packet is sent, rx_st_vc0 will be pulled high, at this time the first data will appear on the data line, one data per clock, when rx_end_vc0 is high, it means that the data line islast data.If there is an ECRC error, rx_ecrc_err_vc0 will be pulled high at the last data moment; if there is a problem with the length of the TLP, rx_malf_tlp_vc0 will be pulled high

tlp receive data

Receive ECRC error

There is a problem with the TLP length

边栏推荐

- 4. PCIe 接口时序

- Memory Forensics Series 1

- Binary tree [full solution] (C language)

- Getting Started with Kubernetes Networking

- GCC:头文件和库文件的路径

- leetcode: 269. The Martian Dictionary

- Software Testing Interview Questions: What's the Difference Between Manual Testing and Automated Testing?

- 2022 Hangzhou Electric Power Multi-School Session 3 K Question Taxi

- E - Many Operations (bitwise consideration + dp thought to record the result after the operation

- Raw and scan of gorm

猜你喜欢

随机推荐

2022杭电多校 第三场 B题 Boss Rush

Software testing interview questions: the difference and connection between black box testing, white box testing, and unit testing, integration testing, system testing, and acceptance testing?

canvas 高斯模糊效果

软件测试面试题:测试用例通常包括那些内容?

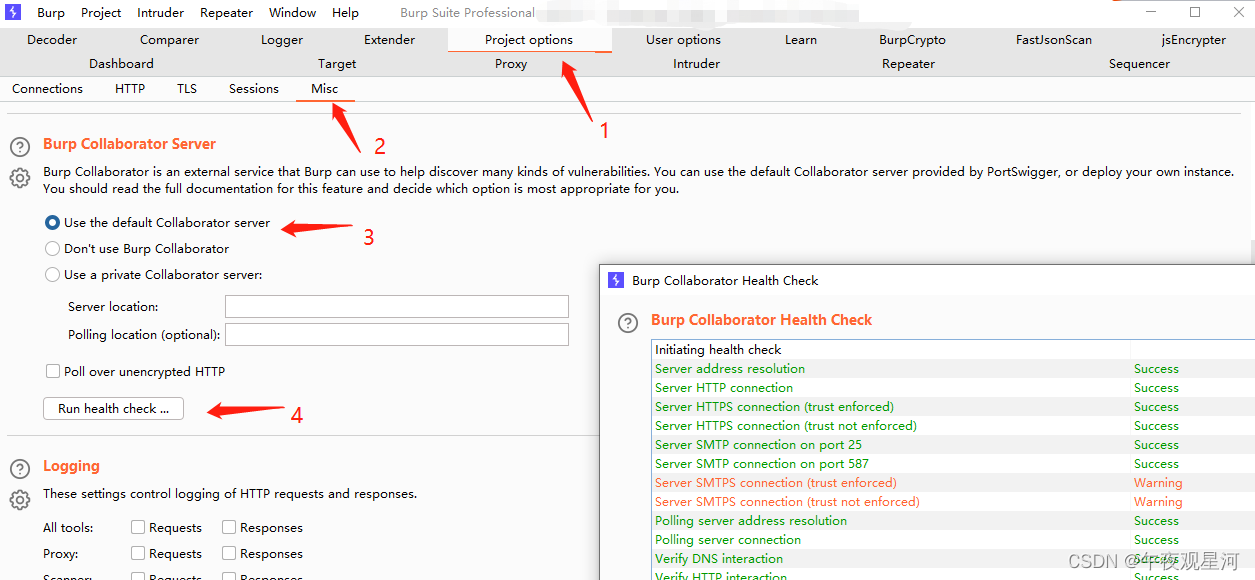

《WEB安全渗透测试》(28)Burp Collaborator-dnslog外带技术

GCC: paths to header and library files

oracle create user

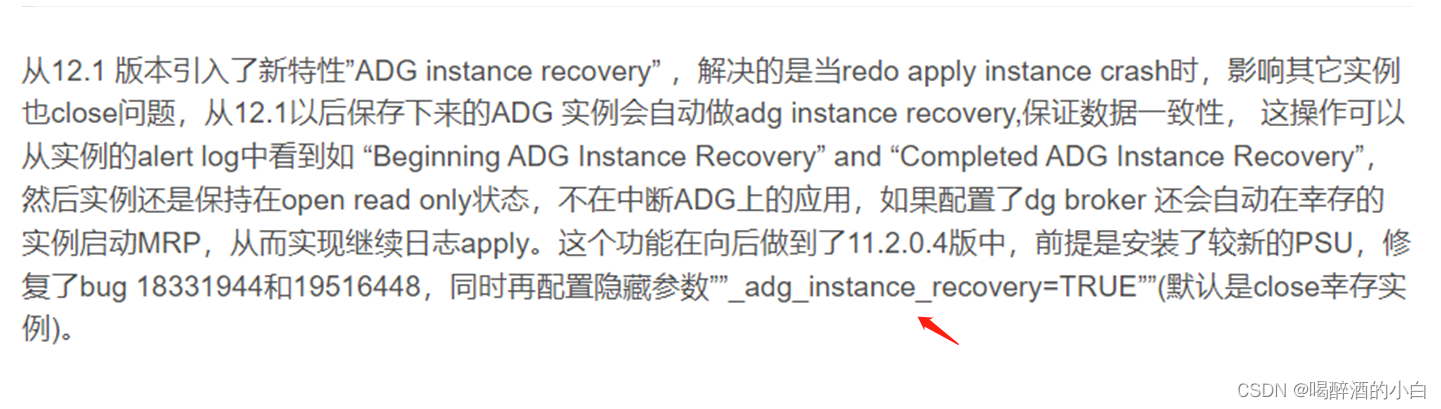

ora-00604 ora-02429

PCIe 核配置

Lattice PCIe 学习 1

Software testing interview questions: What stages should a complete set of tests consist of?

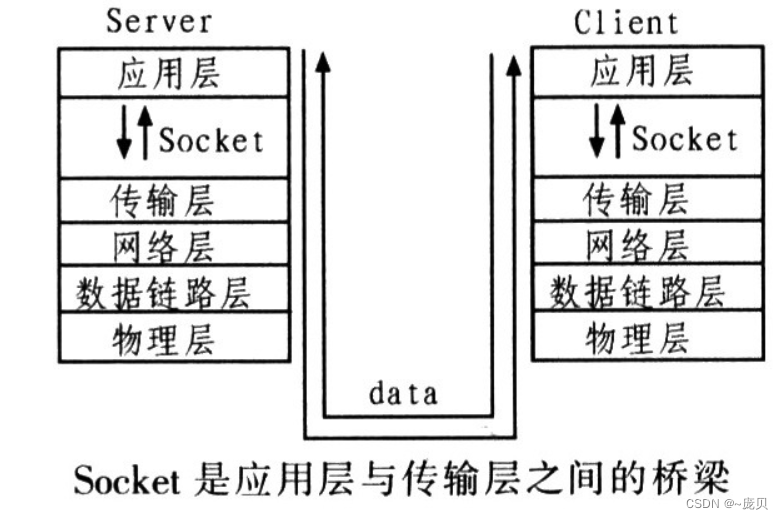

进程间通信和线程间通信

软件测试面试题:测试生命周期,测试过程分为几个阶段,以及各阶段的含义及使用的方法?

3. pcie.v 文件

软件测试面试题:网络七层协仪具体?

ora-01105 ora-03175

2022 Hangzhou Electric Power Multi-School Session 3 Question L Two Permutations

2022 The Third J Question Journey

tiup telemetry

matlab 采用描点法进行数据模拟和仿真