当前位置:网站首页>[Verilog quick start of Niuke network question brushing series] ~ asynchronous reset Series T trigger

[Verilog quick start of Niuke network question brushing series] ~ asynchronous reset Series T trigger

2022-06-29 04:34:00 【AI is very good】

Catalog :

0. Preface

Today, I only scratched one question , Why? ? Is it because it's hard ? It doesn't seem to be !!! Because I think the question on niuke.com seems to be full of loopholes , So I came up with a bold idea , That is to write your own design and test files , Use vcs+verdi Co simulation ( Follow the crowd , Ha ha ha ). Let's not say anything else , It took me a day just to pretend , Purring . But now the environment is basically no problem , About the environment , I did it with reference to the boss , See references .

1. Asynchronous reset series T trigger

Click to see the original question

1.1 Title Description

use verilog Realize two asynchronous reset in series T Logic of trigger

1.1.1 Signal schematic diagram

1.1.2 Waveform diagram

1.1.3 Input description

Input signal data, clk, rst

type wire

stay testbench in ,clk For cycles 5ns The clock of ,rst Reset for low level

1.1.4 Output description

The output signal q

type reg

1.2 Their thinking

It should be noted that , What is the effective level of each signal ? We need to make this clear according to the requirements of the topic , What I need to roast about here is , It is a low level reset , It is not officially defined as rst_n(_n The default is that the low level is active , Personal habits ).

Knowledge point 1:T trigger ===> Input is 1, Output flip ; Input is 0, Output hold .

Knowledge point 2: Asynchronous reset means that the reset can be completed without waiting for the clock . meanwhile , And synchronous reset , In general , It is best to use synchronous reset , Sometimes, asynchronous reset cannot be avoided , Because it saves resources , Very provincial , ha-ha , therefore , An asynchronous reset has occurred , Synchronous release operation , extensive use .

1.3 Code implementation

`timescale 1ns/1ns

module Tff_2 (

input wire data, clk, rst,

output reg q

);

//*************code***********//

reg q_reg;

always @ (posedge clk or negedge rst) begin

if(!rst) begin

q_reg <= 1'b0;

end

else begin

if(data) begin

q_reg <= ~q_reg;

end

else begin

q_reg <= q_reg;

end

end

end

always @ (posedge clk or negedge rst) begin

if(!rst) begin

q <= 1'b0;

end

else begin

if(q_reg) begin

q <= ~q;

end

else begin

q <= q;

end

end

end

//*************code***********//

endmodule

1.4 Simulation file

About simulation files , I haven't done it yet , Let me familiarize myself with vcs and verdi A combination of , ha-ha ! Coming soon .

1.5 Simulation waveform

Coming soon !!!

reference

边栏推荐

- Template method pattern

- ROS URDF model is parsed into KDL tree

- Apifox: it is not only an API debugging tool, but also a collaboration artifact of the development team

- If I hadn't talked to Ali P7, I wouldn't know I was a mallet

- 044. (2.13) add value to yourself

- Practical part: solving the function conflict between swagger and user-defined parameter parser

- Introduction to Bert and Vit

- The virtual machine MySQL cannot be connected to the local computer

- Quelles sont les méthodes de simulation et de gravure des programmes? (comprend les outils communs et la façon dont ils sont utilisés)

- Cisco voice card handling configuration

猜你喜欢

Redis cache penetration, cache breakdown, cache avalanche

泰克TDS3054B示波器技术指标

![[hackthebox] dancing (SMB)](/img/bb/7bf81004b9cee80ae49bb0c0c2b810.png)

[hackthebox] dancing (SMB)

【HackTheBox】dancing(SMB)

What are the ways to simulate and burn programs? (including common tools and usage)

Webapck system foundation

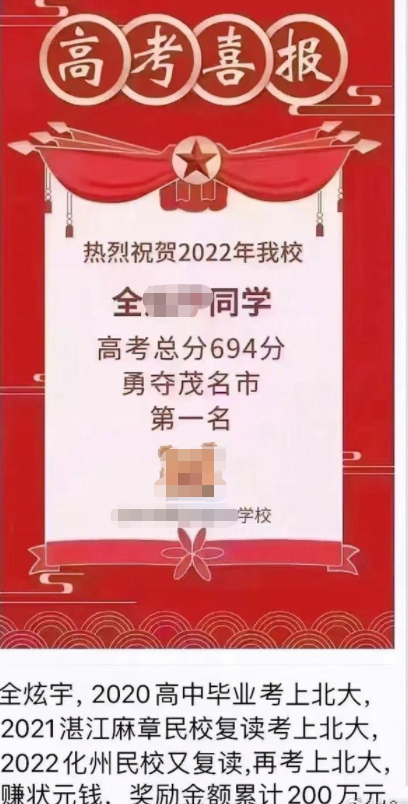

网传广东一名学生3次考上北大,3年共赚200万元奖金

Basic use of JSX

Apifox : 不仅是Api调试工具,更是开发团队的协作神器

如何创建 robots.txt 文件?

随机推荐

泰克TDS3054B示波器技术指标

Redis cache penetration, cache breakdown, cache avalanche

Is the sink usually the JDBC insert update delete?

How to create a subtype like relationship between two generic classes when the classes are generic related

Live broadcast appointment AWS data everywhere series activities

波形记录仪MR6000的实时波形运算功能

1018 hammer scissors cloth

[C language] address of stack memory associated with local variable 'num' returned

How to test electronic components with a multimeter

JVM_ 16_ Garbage collector

Sword finger offer II 040 Largest rectangle in matrix

From zero to one, I will teach you to build a "search by text and map" search service (I)

Redis 缓存穿透、缓存击穿、缓存雪崩

网络设备设置/取消console口登陆单独密码

LabVIEW显示Unicode字符

Mécanisme d'attention du canal de fixation

lua-protobuff emmy-lua 轮子

What exactly does GCC's -Wpsabi option do? What are the implications of supressing it?

Memo pattern

SQL database stored procedure writing method