当前位置:网站首页>NVIC interrupt priority management

NVIC interrupt priority management

2022-07-07 09:07:00 【A big cat 1201】

author : A big cat 1201

special column :《STM32 Study 》

Maxim : You just try to , Leave the rest to time !

NVIC Interrupt priority management

describe

An interrupt can be regarded as an event .

such as , You are studying at home , Suddenly there was a phone call , You can only stop your current study to answer the phone , Someone knocked at the door while answering the phone , You have to put down the phone and open the door , Then pick up the phone and continue to call , After hanging up the phone, continue the previous study .

In the example above , Learning is an ongoing event , And calling is an interruption , When someone knocks on the door during the phone call, it is another interruption .

STM32 The same is true of interruptions in , During the execution of the main program, other events will interrupt the process , Enter the program in the event to execute , After executing the interrupt program, return to the main program to continue execution , This is interrupt .

🦔 Interrupt type

- CM3 The kernel support 256 A break , Which includes 16 Kernel interrupts and 240 External interrupts , And have 256 The programmable interrupt settings of the .

- STM32F10 Series does not use CM3 Everything about the kernel , It's just a part of it .

- STM32F10 Series have 84 A break , Include 16 Kernel interrupts and 68 Maskable interrupts , have 16 Level programmable interrupt priority .

- STM32F103 Above the series , It's just 60 Maskable interrupts ( stay 107 The series has 68 individual ).

Both external interrupts and maskable interrupts here mean the same , It refers to all interrupts excluding kernel interrupts .

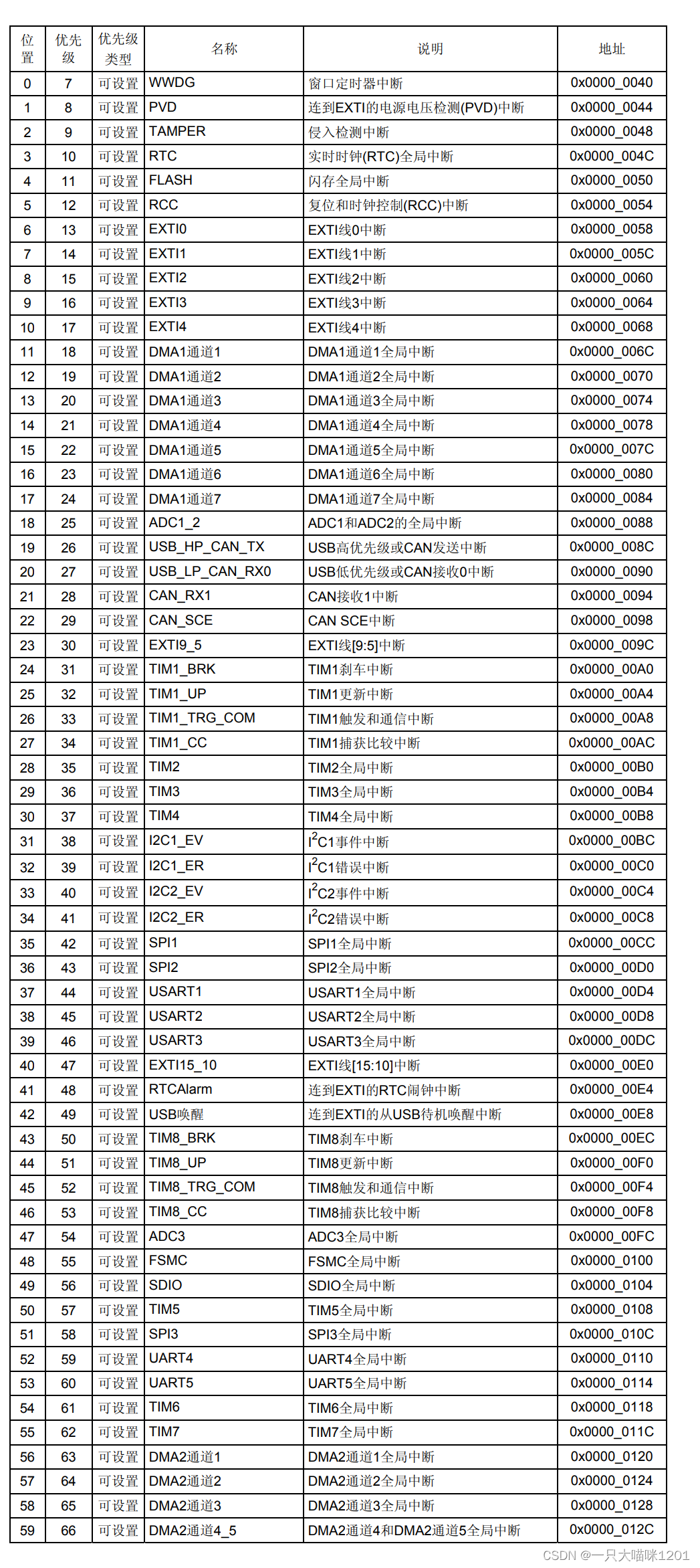

This picture is used by this cat STM32F103ZET6 Of 60 External interrupts .

Interrupt priority grouping

There are so many types of interrupts , How is it managed ?STM32 Manage these interrupts by grouping .

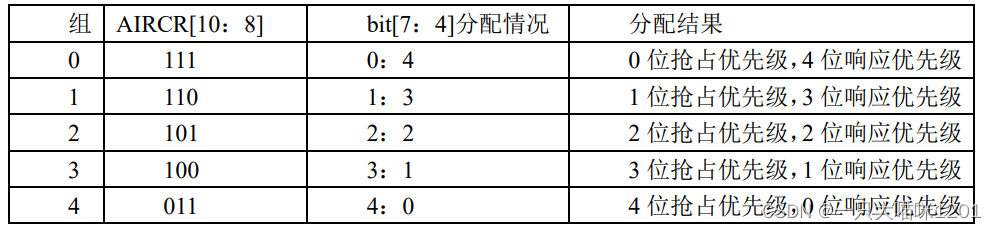

This group is set by SCB->AIRCR The register of bit10~8 To define the .

By giving SCB->AIRCR The second in the register 8 Position to the first 10 The value of bit divides these interrupt types into 5 A set of .

In different groups ,AIRCR The... In the register 4 Position to the first 8 Bit management priorities differ .

For example, the commonly used number 2 Group , this 4 Two of the bits manage preemption priority , You two manage the response priority . From left to right .

At this time, I have doubts , What are the preemption priority and response priority ?

🦔 Preemption priority and response priority

preemption :

- Preemptive priority refers to the interrupt priority of interrupts , Interrupts with high preemption priority can interrupt interrupts with low preemption priority .

Response priority

- Response priority refers to the response sequence of interrupts , The response priority is meaningful only if the preemption priority is the same . Seize the same priority , Two interrupts occur at the same time , Respond to interrupts with high priority first .

Of the two priorities , The smaller the number, the higher the priority .

Illustrate with examples :

- Suppose the interrupt priority group is set to 2

- Then set the

- interrupt 3(RTC interrupt ) The preemption priority of is 2, The response priority is 1.

- interrupt 6( External interrupt 0) The preemption priority of is 3, The response priority is 0.

- interrupt 7( External interrupt 1) The preemption priority of is 2, The response priority is 0.

Then the priority order of these three interrupts is

- interrupt 7> interrupt 3> interrupt 6

When the preemption priority and response priority are the same , Which interrupt occurs first, execute which interrupt program first .

Be careful :

Interrupt grouping is set only once after the initialization of the system . If there is any modification in the later program, the grouping will be chaotic .

For example, when using 2 Group time

The priority management bit is set as shown in the figure above , The preemption priority at this time is 2, The response priority is 2.

After using this group, set the group to 3 Group time , At this time, the preemption priority is 5, The response priority is 0.

In this way , Priority management is chaotic .

🦔 Interrupt priority grouping function

ST The official library function for setting groups , We don't need to set the value of registers one by one .

void NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup)

{

/* Check the parameters */

assert_param(IS_NVIC_PRIORITY_GROUP(NVIC_PriorityGroup));

/* Set the PRIGROUP[10:8] bits according to NVIC_PriorityGroup value */

SCB->AIRCR = AIRCR_VECTKEY_MASK | NVIC_PriorityGroup;

}

This is a function of interrupt priority grouping , He was in ST Official firmware library misc.c In the source file .

From the definition of the function, we can see , Its essence is to configure AIRCR register .

#define NVIC_PriorityGroup_0 ((uint32_t)0x700) /*!< 0 bits for pre-emption priority 4 bits for subpriority */

#define NVIC_PriorityGroup_1 ((uint32_t)0x600) /*!< 1 bits for pre-emption priority 3 bits for subpriority */

#define NVIC_PriorityGroup_2 ((uint32_t)0x500) /*!< 2 bits for pre-emption priority 2 bits for subpriority */

#define NVIC_PriorityGroup_3 ((uint32_t)0x400) /*!< 3 bits for pre-emption priority 1 bits for subpriority */

#define NVIC_PriorityGroup_4 ((uint32_t)0x300) /*!< 4 bits for pre-emption priority 0 bits for subpriority */

above 5 A macro definition is the entry parameter of the interrupt priority grouping function , You can pass the corresponding parameters into the function in which group you need to be divided .

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_0);

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_1);

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2);

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_3);

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_4);

So this 60 External interrupts are grouped .

Interrupt priority setting

Although they are divided into groups , Convenient for management , But exactly which interrupt occurred , Its priority needs to be set in detail .

🦔 Interrupt priority setting register

typedef struct

{

__IO uint32_t ISER[8]; /*!< Offset: 0x000 Interrupt Set Enable Register */

uint32_t RESERVED0[24];

__IO uint32_t ICER[8]; /*!< Offset: 0x080 Interrupt Clear Enable Register */

uint32_t RSERVED1[24];

__IO uint32_t ISPR[8]; /*!< Offset: 0x100 Interrupt Set Pending Register */

uint32_t RESERVED2[24];

__IO uint32_t ICPR[8]; /*!< Offset: 0x180 Interrupt Clear Pending Register */

uint32_t RESERVED3[24];

__IO uint32_t IABR[8]; /*!< Offset: 0x200 Interrupt Active bit Register */

uint32_t RESERVED4[56];

__IO uint8_t IP[240]; /*!< Offset: 0x300 Interrupt Priority Register (8Bit wide) */

uint32_t RESERVED5[644];

__O uint32_t STIR; /*!< Offset: 0xE00 Software Trigger Interrupt Register */

} NVIC_Type;

stay ST In the official firmware library misc.h Such a structure is defined in , The register of the structure is used to set the priority of interrupts .

- ISER[8]:ISER The full name is :Interrupt Set-Enable Registers, This is an interrupt enable register set .STM32F103 The only maskable interrupts are 60 individual , So for us , What works is two (ISER[0] and ISER[1]), All in all, it means 64 A break . and STM32F103 Only the first of them 60 position .ISER[0] Of bit 0 To 31 Corresponding interrupt 0 To 31.ISER[1] Of bit 0 To 27 Corresponding interrupt 32~59; So the total is 60 Each interrupt corresponds to . You have to enable some interruption , You have to set the corresponding ISER Position as 1.

- ICER[8]: The full name is :Interrupt Clear-Enable Registers, It's an interrupt division register set . The register set is similar to ISER It's just the opposite , Is used to clear an interrupt enable . Here we need to set up a special ICER To clear the middle break , Not to ISER Write 0 To get rid of , Because NVIC All of these registers write 1 Effective , Write 0 It's invalid .

- ISPR[8]: The full name is :Interrupt Set-Pending Registers, Is an interrupt pending control register set . The interrupt corresponding to each bit and ISER It's the same . Through setting 1, You can suspend an in progress interrupt , And execute the same level or higher level interrupt . Write 0 It's invalid .

- ICPR[8]: The full name is :Interrupt Clear-Pending Registers, Is an interrupt decoupling control register set . Its function and ISPR contrary , The corresponding bit is also the same as ISER It's the same . By setting 1, You can hook a pending interrupt . Write 0 Invalid .

- IABR[8]: The full name is :Interrupt Active Bit Registers, Is a set of interrupt activated flag registers . The interrupt represented by the corresponding bit and ISER equally , If 1, Indicates that the interrupt corresponding to the bit is being executed . This is a read-only register , It can be used to know which interrupt is currently being executed . After the interrupt is executed, it is automatically reset by hardware .

- IP[240]: The full name is :Interrupt Priority Registers, Is an interrupt priority controlled register set . This register set is quite important STM32 The interrupt group of is closely related to this register group .STM32F103 Only the first of them 60 individual .IP[59] To IP[0] They correspond to interrupts respectively 59~0. And each block interrupt occupied by 8bit Not all use , It's just high 4 position . this 4 position , It is divided into preemption priority and response priority . Preemption comes first , Response priority comes after . And these two priorities occupy several bits, but also according to SCB->AIRCR The interrupt group setting in the .

stay ST Official firmware library core_cm3.h There are several library functions in

static __INLINE void NVIC_SetPendingIRQ(IRQn_Type IRQn);

static __INLINE uint32_t NVIC_GetPendingIRQ(IRQn_Type IRQn);

static __INLINE void NVIC_ClearPendingIRQ(IRQn_Type IRQn);

The function of separation is to suspend an interrupt , Read an interrupt state , Release a suspended interrupt .

🦔 Interrupt priority initialization function

ST The official also provides the setting function of interrupt priority , We don't need to set registers one by one .

typedef struct

{

uint8_t NVIC_IRQChannel; // Set interrupt channel

uint8_t NVIC_IRQChannelPreemptionPriority;// Set preemption priority

uint8_t NVIC_IRQChannelSubPriority; // Set response priority

FunctionalState NVIC_IRQChannelCmd; // Can make / Can make

} NVIC_InitTypeDef;

stay misc.h Such a structure is defined in , Member variables represent

- Interrupt channel , That is, which type of interrupt .

- preemption .

- Response priority .

- Interrupt enable .

And use this structure and GPIO The method of using is similar to

NVIC_InitTypeDef NVIC_InitStructure;

NVIC_InitStructure.NVIC_IRQChannel = USART1_IRQn;// A serial port 1 interrupt

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority=1 ;// Preemption priority is 1

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 2;// Sub priority bit 2

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;//IRQ Channel enable

NVIC_Init(&NVIC_InitStructure); // Initialize... According to the parameters specified above NVIC register

The above completes the initialization of interrupt priority .

summary

When using interrupts

After the system is running, set the interrupt priority group first .

Call function :void NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup); During the execution of the whole system , Set interrupt packet only once .For each interrupt , Set the corresponding preemption priority and response priority .

Call function :void NVIC_Init(NVIC_InitTypeDef* NVIC_InitStruct); If you need to suspend / Jie hang , View the current activation status of the interrupt , Call related functions respectively .

边栏推荐

- systemd

- Port occupation troubleshooting

- 【ChaosBlade:根据标签删除POD、Pod 域名访问异常场景、Pod 文件系统 I/O 故障场景】

- LeetCode 715. Range module

- Original collection of hardware bear (updated on June 2022)

- 年薪50w阿里P8亲自下场,教你如何从测试进阶

- 【istio简介、架构、组件】

- Serial port experiment - simple data sending and receiving

- MySQL master-slave delay solution

- Explain Huawei's application market in detail, and gradually reduce 32-bit package applications and strategies in 2022

猜你喜欢

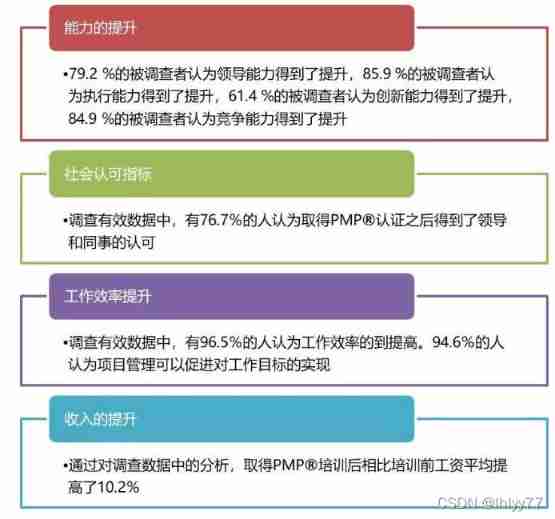

How to pass the PMP Exam in a short time?

JVM 内存结构 详细学习笔记(一)

Platformization, a fulcrum of strong chain complementing chain

PMP Exam details after the release of the new exam outline

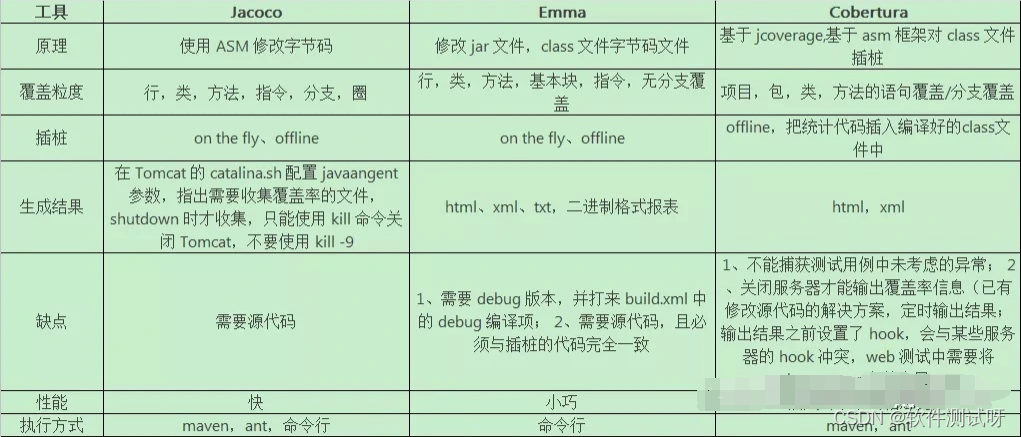

阿里p8推荐,测试覆盖率工具—Jacoco,实用性极佳

C语言指针(上篇)

Hard core sharing: a common toolkit for hardware engineers

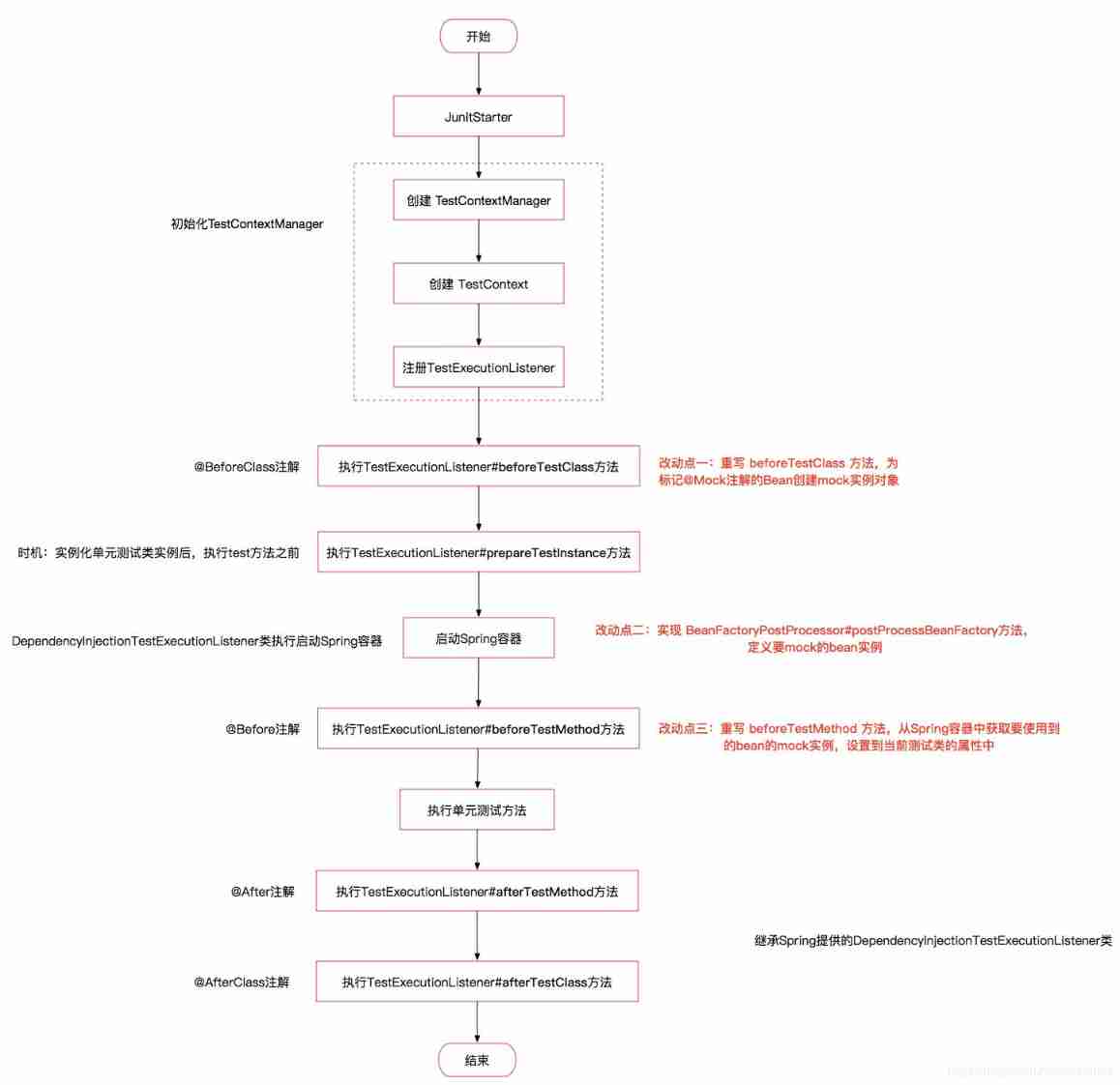

Two schemes of unit test

寄存器地址名映射

面试题:高速PCB一般布局、布线原则

随机推荐

How to pass the PMP Exam in a short time?

JVM garbage collection detailed learning notes (II)

Calf problem

PMP Exam Preparation experience systematically improve project management knowledge through learning

模拟卷Leetcode【普通】1705. 吃苹果的最大数目

Platformization, a fulcrum of strong chain complementing chain

模拟卷Leetcode【普通】1706. 球会落何处

Original collection of hardware bear (updated on June 2022)

模拟卷Leetcode【普通】1609. 奇偶树

2021 year end summary

C language for calculating the product of two matrices

Lenovo hybrid cloud Lenovo xcloud: 4 major product lines +it service portal

LeetCode 715. Range 模块

C语言指针(特别篇)

年薪50w阿里P8亲自下场,教你如何从测试进阶

[chaosblade: node disk filling, killing the specified process on the node, suspending the specified process on the node]

Systick滴答定时器

数字三角形模型 AcWing 1027. 方格取数

Tronapi wave field interface - source code without encryption - can be opened twice - interface document attached - package based on thinkphp5 - detailed guidance of the author - July 6, 2022 - Novice

Analysis of Hessian serialization principle