当前位置:网站首页>面试题:高速PCB一般布局、布线原则

面试题:高速PCB一般布局、布线原则

2022-07-07 06:20:00 【硬件大熊】

面试过程中关于高速PCB的布局、布线原则的提问可以对面试者的layout功底进行一定的考量,对此笔者总结、记录如下,仅供参考——

高速PCB布局

高速PCB布局基本上决定了布线的大致走向和结构、电源和地平面的分割,以及对噪声和EMI的控制情况。一般的布局原则为——

了解系统原理图,在各个电路中划分数字、模拟、混合数字/模拟元器件,注意各芯片电源和信号引脚的定位;

根据电路中各部分所占比重,初步划分数字电路、模拟电路在PCB上的布线区域,让数字元器件、模拟元器件及其相应布线尽量远离并限定在各自的布线区域内,划分完毕后一般的顺序是混合型器件 --> 模拟器件 --> 数字器件 --> 旁路电容

数模混合元器件放置在数字信号区域和模拟信号区域的交界之处,摆放的方向上注意芯片的数字信号和模拟信号引脚朝向各自的布线区域。纯数字或模拟元器件放置在各自规定的范围之内,晶振电路尽量靠近其驱动器件;

对噪声敏感的器件要远离高频信号布线,如反馈电压Fb。有时序要求限制的信号布线,需根据长度和结构进行布局的调整。旁路电容尽量靠近电源引脚放置,尤其是高频电容。在电源接口附件放置大容量电容,以保持电源稳定、降低低频噪声干扰。

高速PCB布线

高速PCB布线涉及到的细节较多且更为灵活,以合理的布局为前提,配合布线基本原则,可以让我们避免意想不到的信号完整性问题或时序问题——

合理选择层数。高频电路集成度较高,布线密度大,合理采用多层板可以利用中间层来设置屏蔽,更好地实现接地,有效降低寄生电感,缩短信号传输长度,降低信号间的交叉干扰等。

减少高速电路元器件引脚间引线的折弯。高频线路最好采用全直线,在需要弯折时,可用45°折线或圆弧线,避免信号的折射;

缩短高频引线长度;

减少高频引线层间交叠。即减少走线过程中所用的过孔,一个过孔可带来约0.5pf的分布电容,减少过孔数能降低对信号速度的影响;

注意信号线近距离布线时可能引入的交叉干扰,若无法避免平行分布,可在平行线的反面、线之间布置大面积的地线。实际操作中,层内平行布线几乎无法避免,但相邻两个层的布线方向必须为相互垂直,即相邻两层的走线方向分别进行平行水平和垂直布线;

对特别敏感的信号线或局部单元进行包地措施。如对时钟单元进行包地;

各类信号布线不能形成环路,也不能形成电流环路;

正确选择单点接地和多点接地。低频电路中,信号的工作频率通常小于1MHz,此时布线和器件间的电感影响较小,而接地电路形成的环流对干扰影响较大,因此采用单点接地的方式;高频电路中,如当信号大于10MHz时,地线阻抗将变得很大,此时应采用多点接地方式,降低接地阻抗。关于地线的设计,还需留意尽量加粗地线,地线太细会导致接地电位随电流的变化而变化,若有可能,地线家村至能通过3倍于PCB的允许电流,另,将接地系统构成闭环路也能缩小电位差。

参考文献:

《Candence高速电路板设计与仿真》周润景、王洪艳编著

推荐阅读:

原创不易,若有转载需求,务必告知!

如果我的文字对你有所启发或帮助,

“点赞\转发”是对我最大的支持

边栏推荐

- Rapid integration of authentication services - harmonyos platform

- IP地址的类别

- Digital triangle model acwing 275 Pass a note

- 数据分析方法论与前人经验总结2【笔记干货】

- [MySQL] detailed explanation of trigger content of database advanced

- 数据库存储---表分区

- A bug using module project in idea

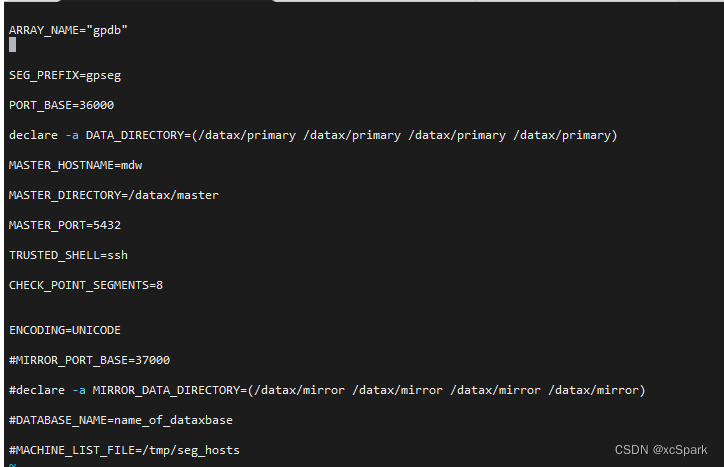

- Greenplum6.x-版本变化记录-常用手册

- 测试踩坑 - 当已有接口(或数据库表中)新增字段时,都需要注意哪些测试点?

- Data analysis methodology and previous experience summary 2 [notes dry goods]

猜你喜欢

Platformization, a fulcrum of strong chain complementing chain

![FPGA knowledge accumulation [6]](/img/db/c3721c3e842ddf4c1088a3f54e9f2a.jpg)

FPGA knowledge accumulation [6]

Esp32-ulp coprocessor low power mode RTC GPIO interrupt wake up

Greenplum 6.x reinitialization

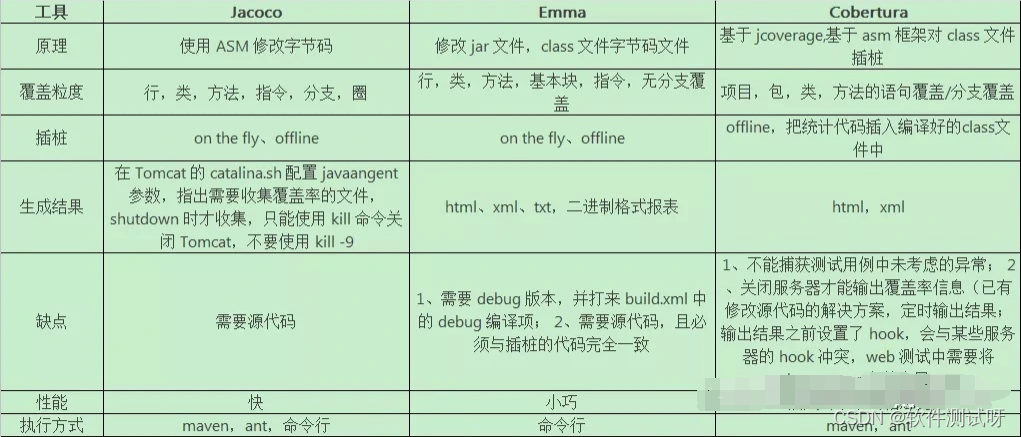

Recommended by Alibaba P8, the test coverage tool - Jacobo is very practical

ESP32-ULP协处理器低功耗模式RTC GPIO中断唤醒

Lenovo hybrid cloud Lenovo xcloud: 4 major product lines +it service portal

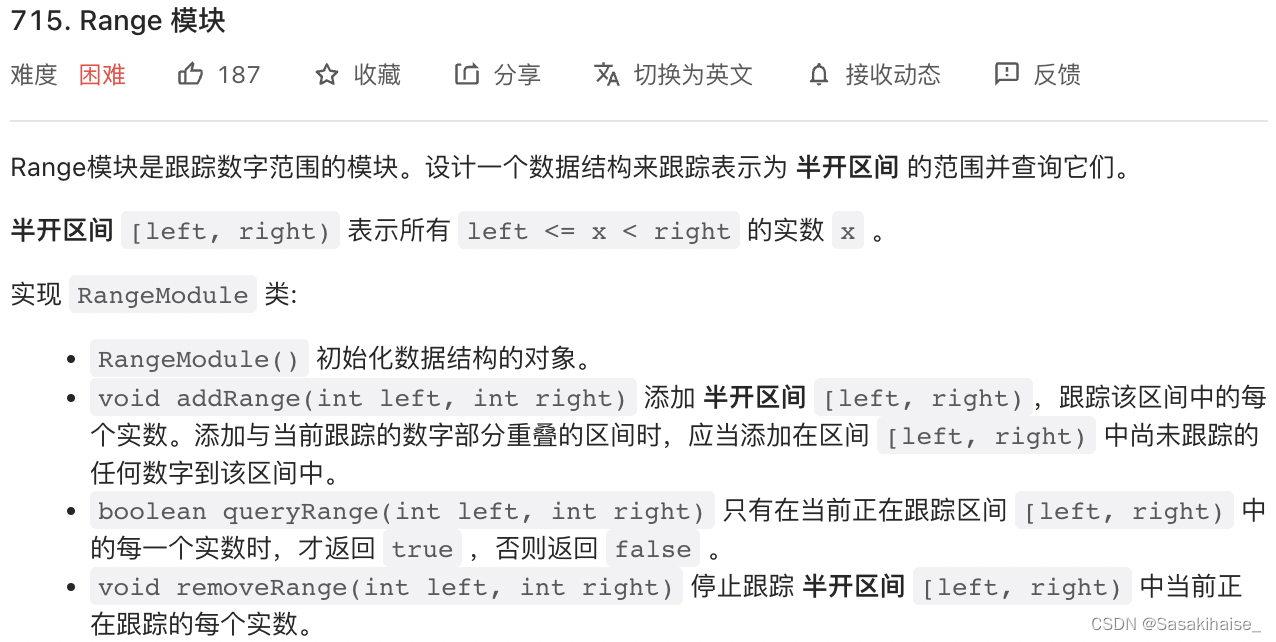

LeetCode 715. Range module

A bug using module project in idea

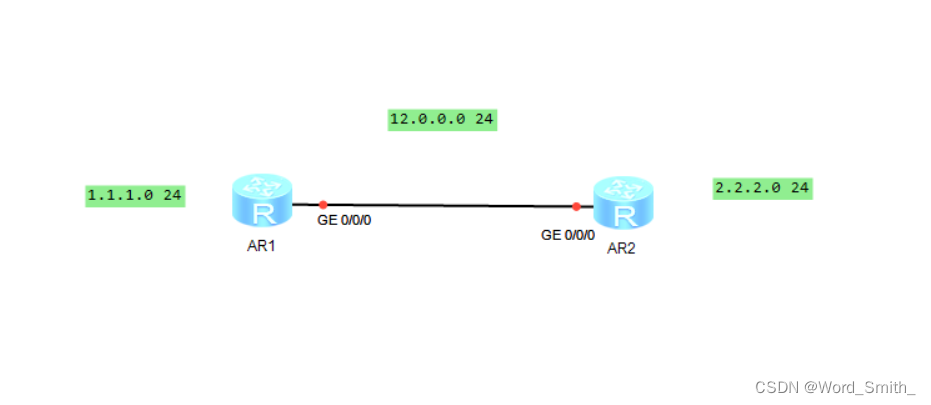

路由信息协议——RIP

随机推荐

go mod module declares its path as: gtihub. com/xxx-xx but was required as:xx-xx

ESP32-ULP协处理器低功耗模式RTC GPIO中断唤醒

cmake命令行使用

You should use Google related products with caution

Category of IP address

Sign and authenticate API interface or H5 interface

年薪50w阿里P8亲自下场,教你如何从测试进阶

指针进阶,字符串函数

登山小分队(dfs)

opencv之图像分割

更改当前文件夹及文件夹下文件日期shell脚本

Tronapi wave field interface - source code without encryption - can be opened twice - interface document attached - package based on thinkphp5 - detailed guidance of the author - July 6, 2022 - Novice

使用AGC重签名服务前后渠道号信息异常分析

redis故障处理 “Can‘t save in background: fork: Cannot allocate memory“

[Yu Yue education] basic reference materials of electrical and electronic technology of Nanjing Institute of information technology

Quick sorting (detailed illustration of single way, double way, three way)

Markdown editor Use of MD plug-in

MySQL partition explanation and operation statement

Recommended by Alibaba P8, the test coverage tool - Jacobo is very practical

Interpolation lookup (two methods)