当前位置:网站首页>FPGA knowledge accumulation [6]

FPGA knowledge accumulation [6]

2022-07-07 08:37:00 【Vince mock, Yamaji】

Catalog

1. Filter type

Analog filters are divided into active and passive , I have seen it in the last section ——FPGA Accumulation of knowledge 【5】 The first 6 spot

Now let's talk about the types of digital filters :

① Classify according to frequency band :

W Is a certain cut-off frequency

low pass filter (LPF): Passband 0 ~ W

Bandpass filter (BPF): Passband W1 ~ W2

Band stop filter (BSF): Stopband W1 ~ W2 ( Limiting wave )

High pass filter (HPF): Passband W ~ ∞

All pass filter (APF): All in

② Sort by response type :

Butterworth response filter : Maximize the passband flatness of the filter

Bessel response filter : The phase nonlinearity of the passband is minimized

Chebyshev response filter : Filter with ripple fluctuation such as frequency response amplitude on passband or stopband

③ Classified by unit pulse :

Infinite impulse response filter (IIR): Recursive filter , From a hardware point of view ,IIR The filter is fast , Efficient 、 real time IIR The sampling rate of the filter is much higher than FIR, And with feedback

Finite impulse response filter (FIR): Finite length unit impulse response filter , It is also called non recursive filter , It is the most basic component in digital signal processing system

2. most Small / Big Item nature

The properties of the minimum term :

① Under any value of the input variable , The value with and only one minimum term is 1;

② The sum of all minimum terms is 1 ;

③ The product of any two minimum terms is 0 ;

④ The sum of two adjacent minimum terms can be combined , Eliminate a pair of factors , Leave only the common factor ;( The important principle of Karnaugh map ) adjacent : The smallest term with only one factor different , Such as :A’BC’ And A’BC;

The properties of the largest term :

① Under any value of the input variable , The value of having and only one maximum item is 0 ;

② The product of all the largest terms is 0 ;

③ The sum of any two largest terms is 1 ;

④ The product of two adjacent largest terms can be merged , Eliminate a pair of factors , Leave only the common factor . adjacent : There is only one maximum term with different factors , Such as :A’+B+C and A’+B+C

3. High speed low speed signal

Here are Candence Judgment of high-speed signal ;

① Everything is greater than 50MHz The signal of , It's a high-speed signal

② It is not directly related to frequency , But the signal goes up / The falling edge is less than 50 ps It is considered as a high-speed signal

③ When the transmission path length of the signal is greater than 1/6λ , The signal is considered to be a high-speed signal

④ When the signal is transmitted along the transmission path , When serious skin effect and ionization loss occur , It is considered a high-speed signal

The above definitions , To some extent, it is reasonable . And the time of the rising edge and falling edge of the signal is smaller , The high-frequency component of the signal will be more and more , The signal bandwidth is large , At this time, the integrity of the signal must be considered .

4. Packet processing performance calculation

The message length is 65bytes,FPGA The processing bit width is 64bit, use 250M Working clock , What is the packet processing performance ?

① How to calculate the package processing performance ? in my opinion , It's just how much data is read in how long

② Then the clock frequency is given in the question stem 250M, We can calculate the time of a clock cycle is 1/250M second

③ So a clock cycle FPGA How much data can be processed , I think so 64bit, That is, the time of a clock cycle , namely 1/250M second ,FPGA Processed 64bit data , Then one second is 250M * 64 bit The data of , That is to say, the performance is 16G bps

5. Clock type

① Global clock : Clock signal on the global clock network , Small signal skew can be guaranteed (skew), The time when the real-time clock signal reaches each trigger is as close as possible , In other words, synchronize the clock , Strong predictability

② Multilevel logic clock : Multi level combinational logic should not be used to clock PLD Triggers in design , Low reliability

③ Traveling wave clock : The output of one trigger is used as the clock input of another trigger , The timing calculation related to the circuit becomes very complex

④ Gate clock : It is used to reduce the excessive internal register flip with the clock flip, so as to reduce the power consumption of the clock

6. Operator priority

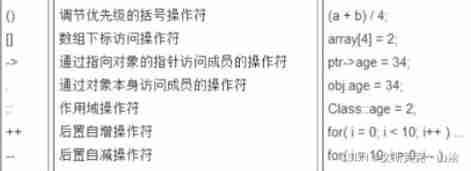

first stage :

Level second :

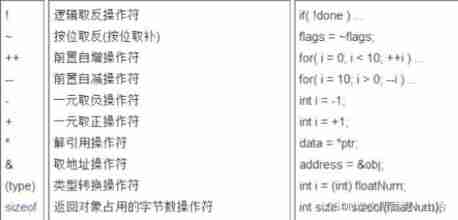

Level third :

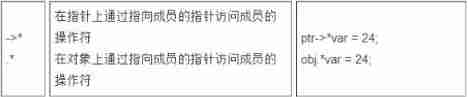

Level fourth :

fifth degree :

Level six :

Level seven :

Level 8 :

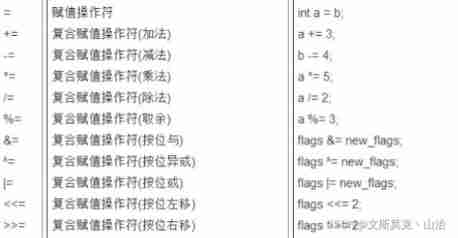

Then lower the priority level by level :

Level 15 :

Level 16 :

7.8421 code

8421 Code is the name of Chinese Mainland ,8421 Code is BCD One of the most commonly used in code , Every decimal number uses 4 Bit representation . for example 45 use 8421 Code means 01000101 , Ahead 0100 Express 4, hinder 0101 Express 5.

8.Verilog Synthesizable statements

① Structures supported by all integrated tools :always,assign,begin,end,case,wire,tri,aupply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter

② Structures that are not supported by all integrated tools :time,defparam,$finish,fork,join,initial,delays,UDP,wait

③ Some tools support structures that some tools do not support :casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while.

Reference resources :

Operator priority full list , List

Verilog Overview of integrable and non integrable sentences in

边栏推荐

- Componentspace2022, assertions, protocols, bindings, and configuration files

- How to understand distributed architecture and micro service architecture

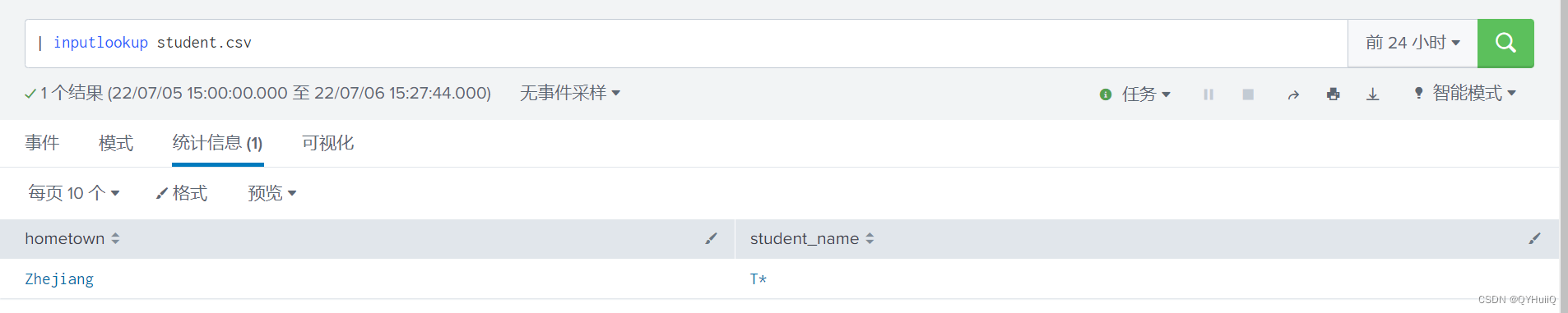

- Splunk query CSV lookup table data dynamic query

- [Yu Yue education] basic reference materials of electrical and electronic technology of Nanjing Institute of information technology

- One click deployment of highly available emqx clusters in rainbow

- Data type - floating point (C language)

- MySQL introduction - crud Foundation (establishment of the prototype of the idea of adding, deleting, changing and searching)

- 更改当前文件夹及文件夹下文件日期shell脚本

- 归并排序和非比较排序

- Installation and configuration of PLSQL

猜你喜欢

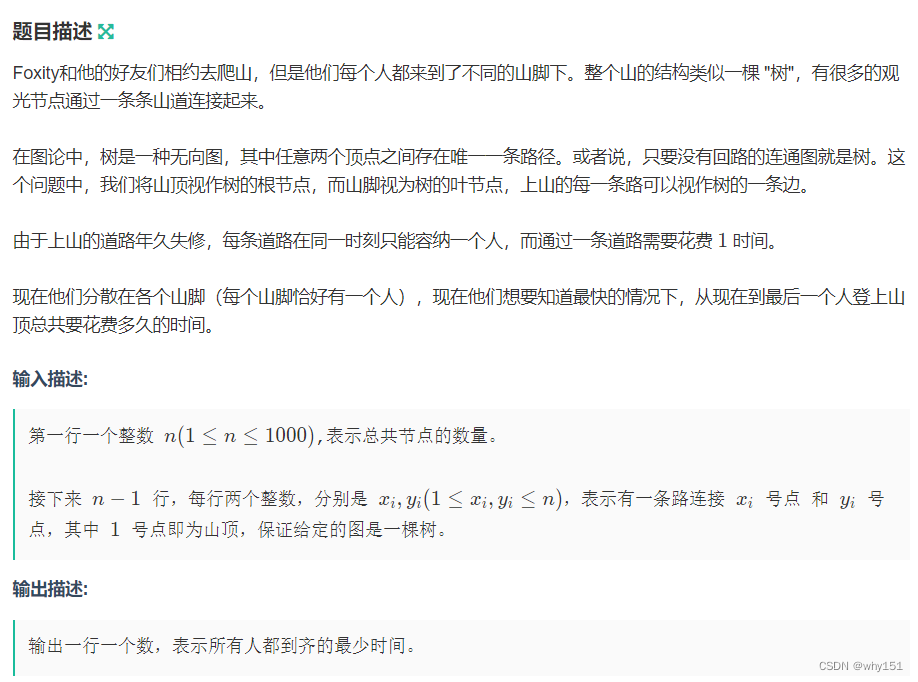

登山小分队(dfs)

【无标题】

All about PDF crack, a complete solution to meet all your PDF needs

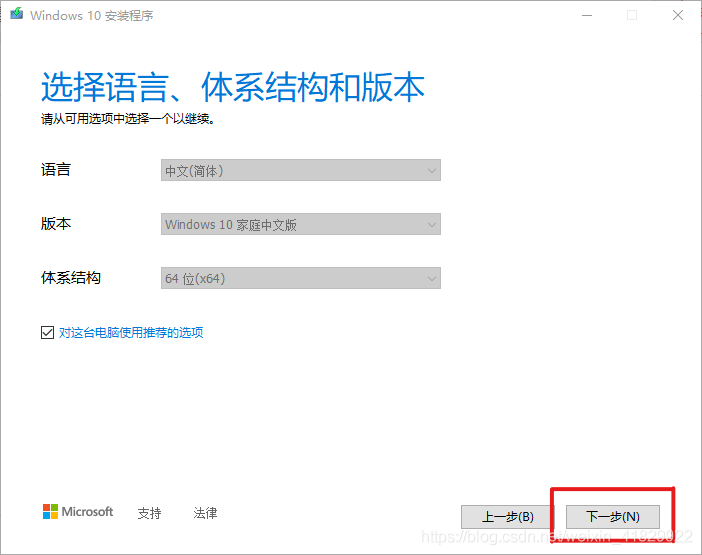

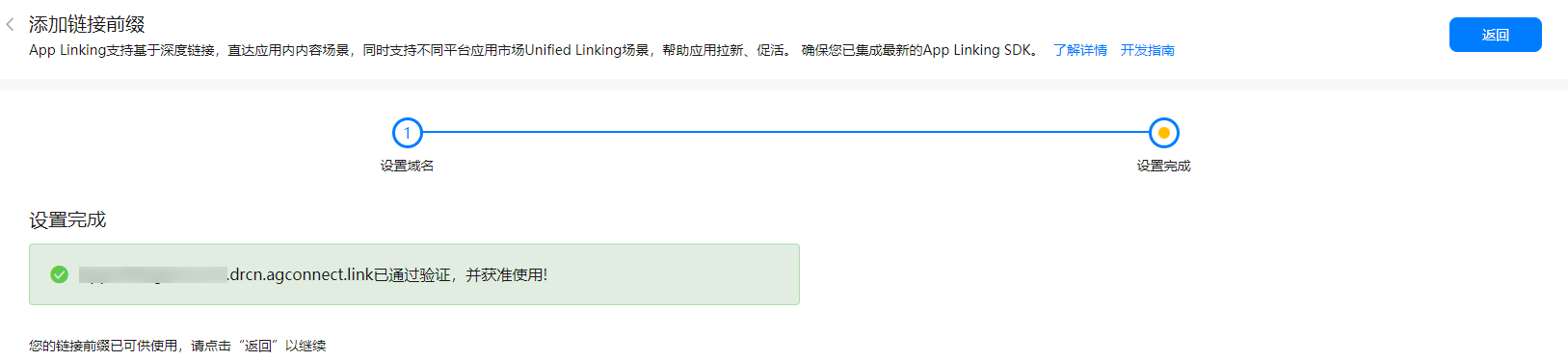

How to integrate app linking services in harmonyos applications

数据分析方法论与前人经验总结2【笔记干货】

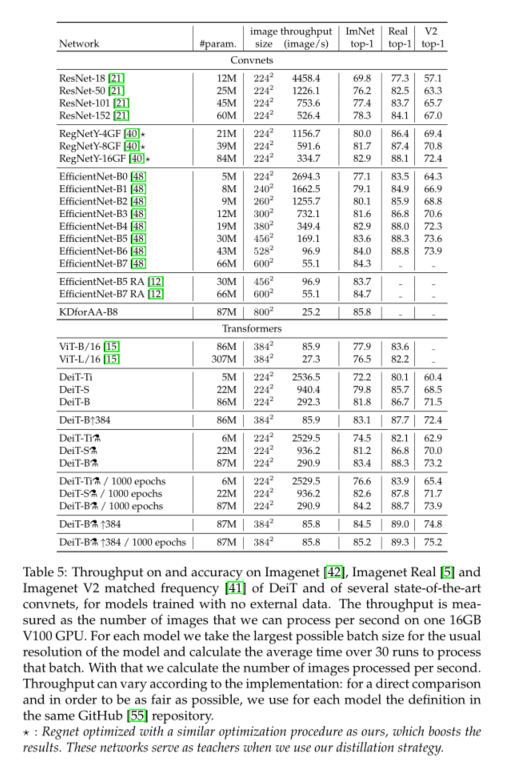

DeiT学习笔记

The field value in Splunk subquery fuzzy matching CSV is*

idea里使用module项目的一个bug

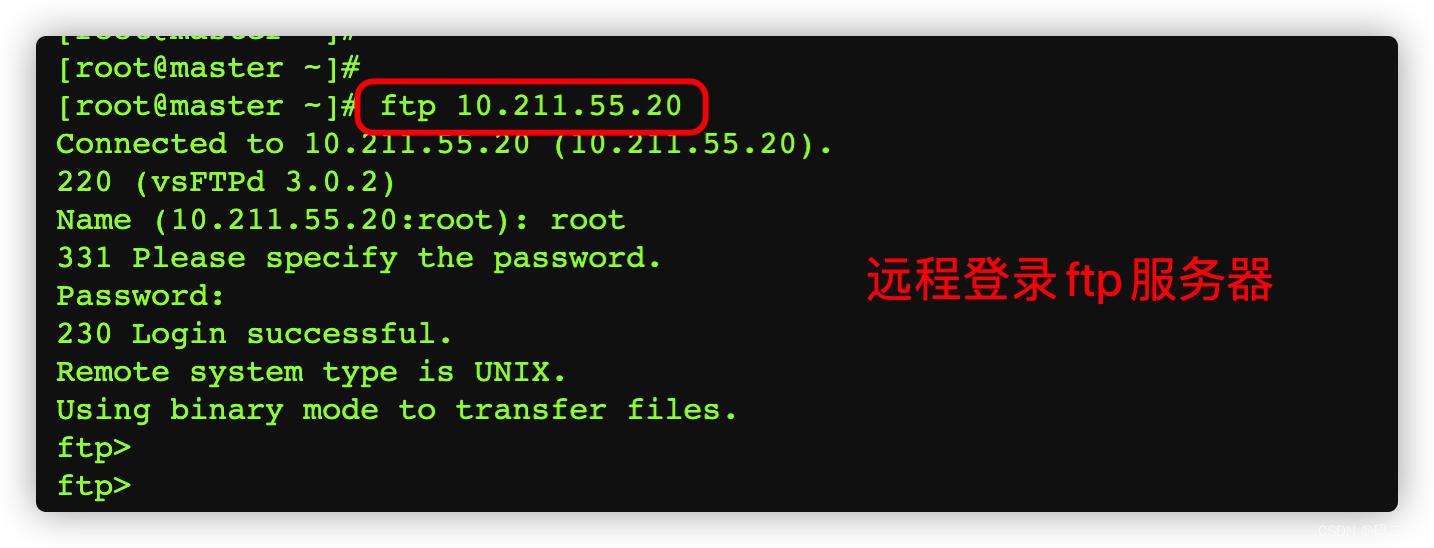

Iptables' state module (FTP service exercise)

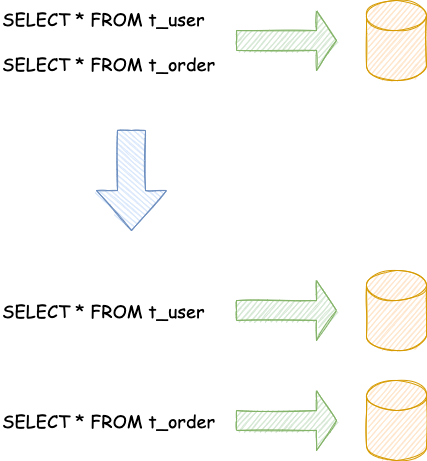

数据分片介绍

随机推荐

The single value view in Splunk uses to replace numeric values with text

How to realize the high temperature alarm of the machine room in the moving ring monitoring system

Virtual address space

Pvtv2--pyramid vision transformer V2 learning notes

Input of mathematical formula of obsidan

Download and install orcale database11.2.0.4

Le système mes est un choix nécessaire pour la production de l'entreprise

One click deployment of highly available emqx clusters in rainbow

The field value in Splunk subquery fuzzy matching CSV is*

调用华为游戏多媒体服务的创建引擎接口返回错误码1002,错误信息:the params is error

一种适用于应用频繁测试下快速查看Pod的日志的方法(grep awk xargs kuberctl)

[IELTS speaking] Anna's oral learning records Part3

Snyk dependency security vulnerability scanning tool

GOLand idea intellij 无法输入汉字

How to integrate app linking services in harmonyos applications

ES6_ Arrow function

One click installation of highly available Nacos clusters in rainbow

In go language, function is a type

为什么要选择云原生数据库

let const