当前位置:网站首页>13.56MHZ刷卡芯片CI521兼容cv520/ci520支持A卡B卡MIFARE协议

13.56MHZ刷卡芯片CI521兼容cv520/ci520支持A卡B卡MIFARE协议

2022-08-02 14:09:00 【K18025398187】

CI521是一款高度集成的13.56MHZ刷卡芯片,pin对pin兼容CV520无需软硬件修改,支持A/B/MIFAR卡协议

简介

Ci521是一个高度集成的,工作在13.56MHz的非接触式读写器芯片,阅读器支持ISO/IEC 14443 A/B/MIFARE。

无需外围其他电路,Ci521的内部发送器可驱动读写器天线与ISO/IEC 14443 A/B/MIFARE卡和应答机通信。接收器模块提供一个强大而高效的电路,用以解调译码ISO/IEC 14443 A/B/MIFARE 兼容卡及应答机信号。数字模块处理完整的

ISO/IEC 14443 A/B帧和错误检测功能(奇偶和CRC)。 Ci521支持MIFARE产品。Ci521支持非接触式通信,与MIFARE系列双向通信速率高达848kBd。 Ci521提供SPI(串行外设接口)主机接口。

参数和特性

- 高度集成的模拟电路,解调和译码响应

- 带缓冲的输出驱动器,使用最少的外围元件与天线连接

- 支持ISO/IEC 14443 A/B/MIFARE

- 读写器模式的操作距离取决于天线的尺寸和圈数, 典型操作距离为50mm,

- 读写器模式下支持MIFARE系列卡

- 支持ISO/IEC 14443 A/B/Mifare更高速率通信,最高达848kBd

- 支持SPI接口,通信速率高达10Mbit/s

- 64字节发送和接收FIFO缓冲区

- 灵活的中断模式

- 低功耗硬复位功能

- 软件掉电模式

- 可编程定时器

- 内部振荡器,连接27.12MHz石英晶体

- 2.3V至3.6V供电电压

- CRC协处理器

接口

串行外设接口(兼容SPI)支持与主机高速通信,最高可达10Mbit/s。当与主机通信时,Ci521作为从机,接收主机的寄存器配置以及发送或接收RF接口相关的通信数据。兼容SPI的接口实现Ci521和微控制器间的高速串行通信。该接口协议与SPI标准一致。

SPI通信时Ci521作为从机,SPI时钟必须由主机产生。MOSI和MISO上的数据均为MSB在前,数据必须在时钟的上升沿时保持稳定,在下降沿时可修改。Ci521在时钟下降沿时提供数据,上升沿时保持稳定。

典型应用案例

封装图

边栏推荐

猜你喜欢

随机推荐

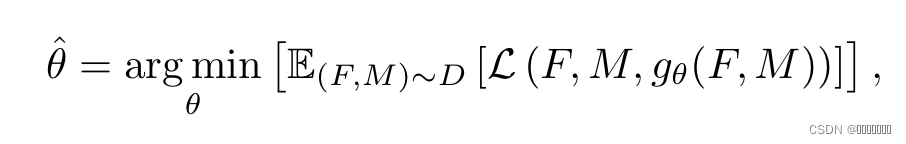

基于GPT的隐变量表征解码结构

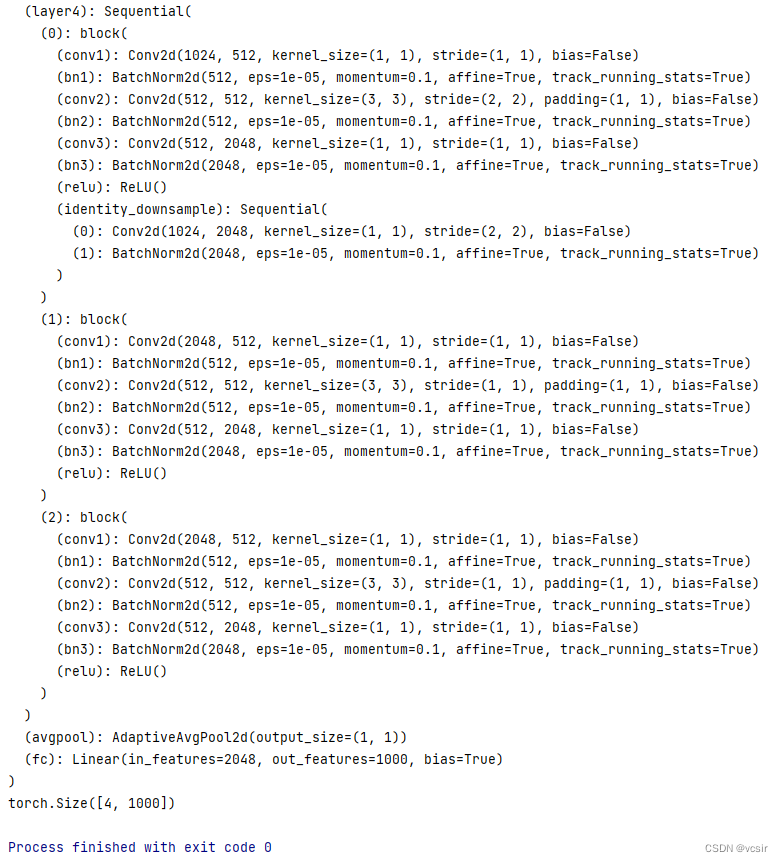

让深度学习歇一会吧

PyTorch(12)---损失函数和反向传播

tensorflow实战之手写体识别

文本匹配任务

LLVM系列第六章:函数返回值Return

自定义圆形seekBar,超简单

spark on yarn

flutter中App签名

神经网络可以解决一切问题吗:一场知乎辩论的整理

vscode compiles the keil project and burns the program

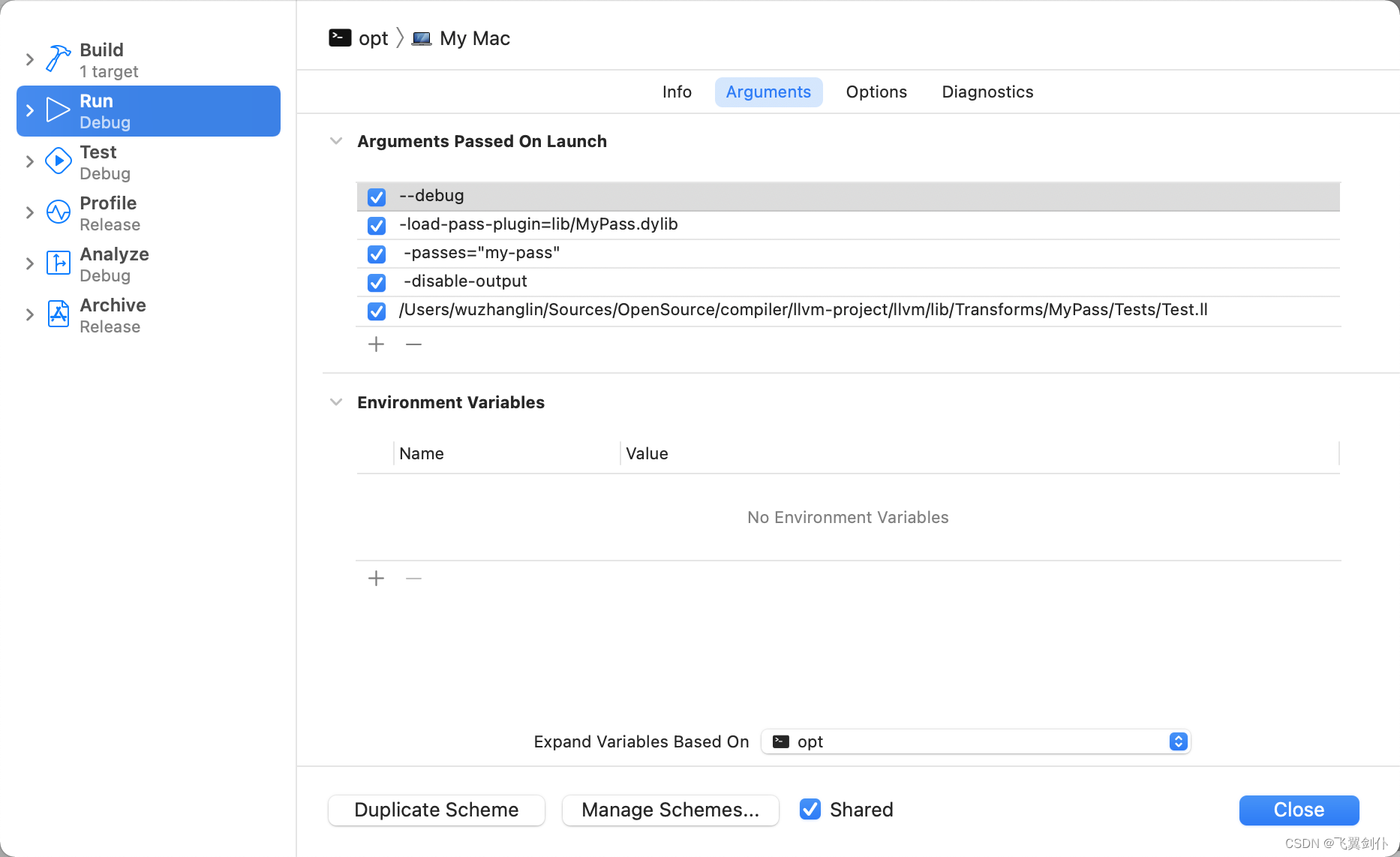

LLVM系列第十八章:写一个简单的IR处理流程Pass

LLVM系列第二十三章:写一个简单的运行时函数调用统计器(Pass)

arm push/pop/b/bl汇编指令

PyTorch④---DataLoader的使用

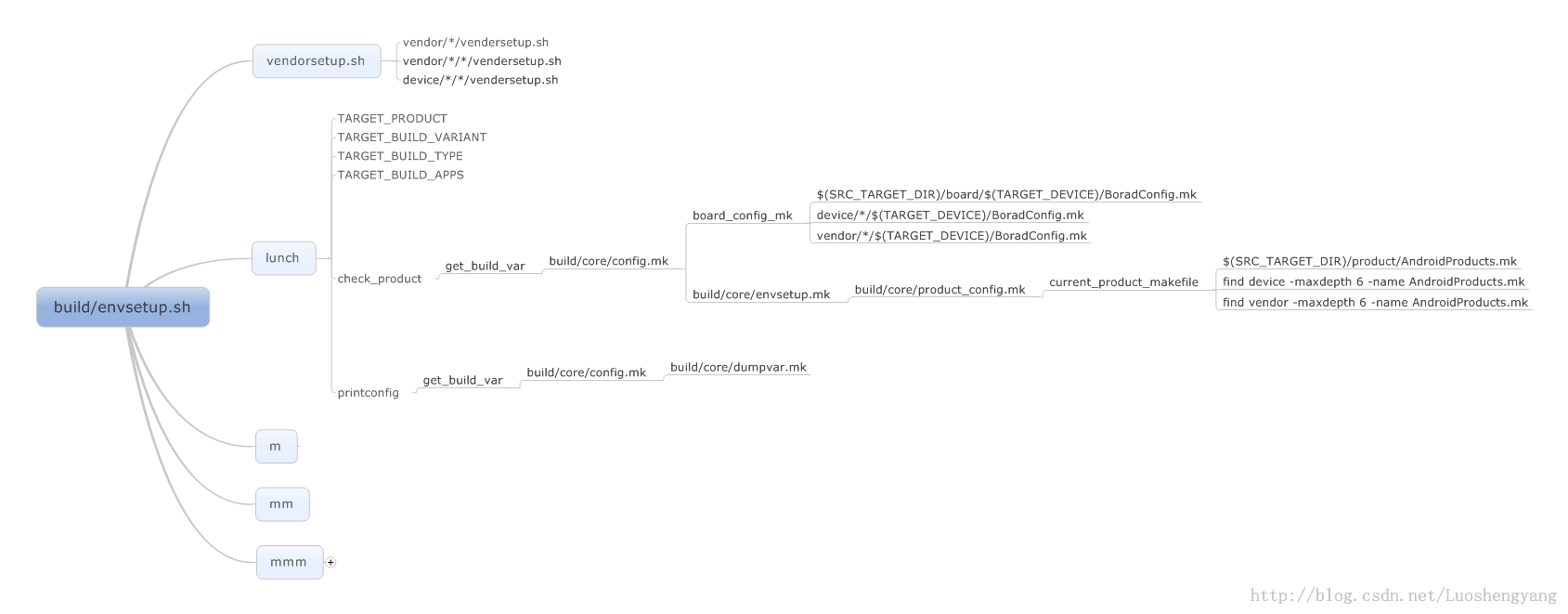

设备驱动框架简介

kotlin Android序列化

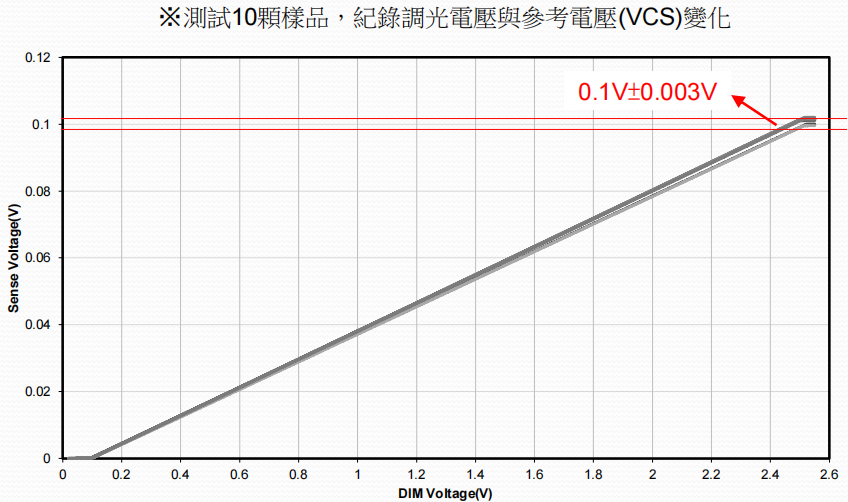

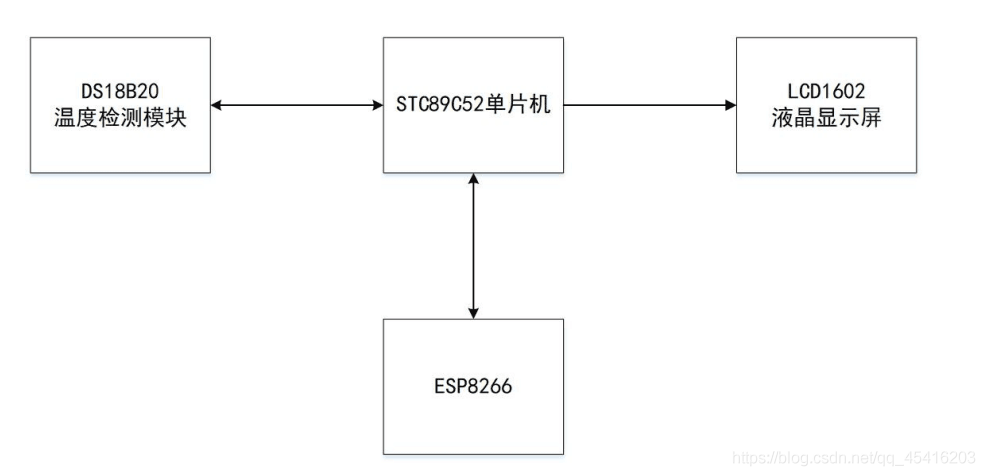

FP7195降压恒流PWM转模拟调光零压差大功率驱动方案原理图

NDK报错问题分析方案(一)

小T成长记-网络篇-1-什么是网络?