当前位置:网站首页>【数字IC验证快速入门】23、SystemVerilog项目实践之AHB-SRAMC(3)(AHB协议基本要点)

【数字IC验证快速入门】23、SystemVerilog项目实践之AHB-SRAMC(3)(AHB协议基本要点)

2022-07-07 13:22:00 【luoganttcc】

导读:作者有幸在中国电子信息领域的排头兵院校“电子科技大学”攻读研究生期间,接触到前沿的数字IC验证知识,旁听到诸如华为海思、清华紫光、联发科技等业界顶尖集成电路相关企业面授课程,对数字IC验证有了一些知识积累和学习心得。为帮助想入门前端IC验证的朋友,思忱一二后,特开此专栏,以期花最短的时间,走最少的弯路,学最多的IC验证技术知识。

文章目录

一、内容概述

- 基本 AHB 信号

- AHB 传输

二、AHB 详细介绍

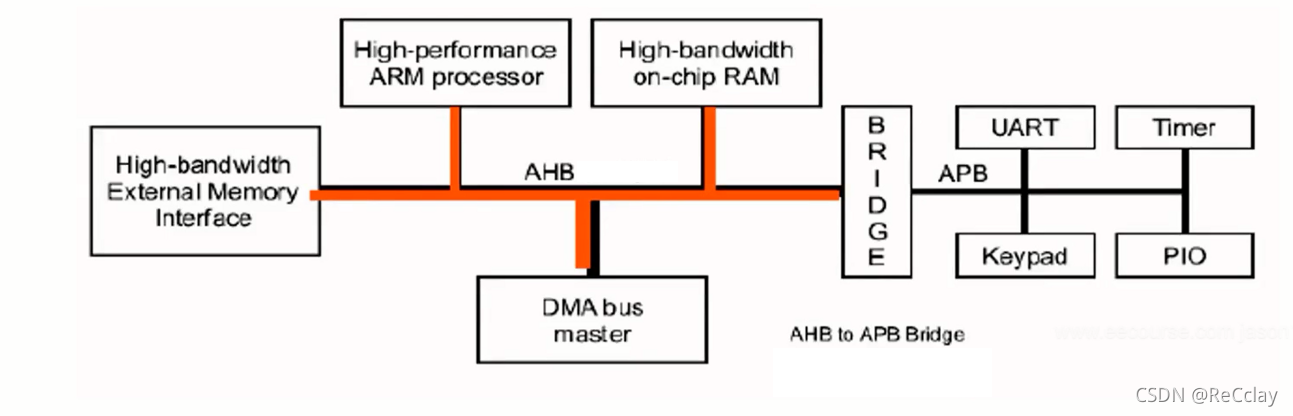

2.1、一个典型的AMBA 2.0系统

2.2、AHB 总线互连

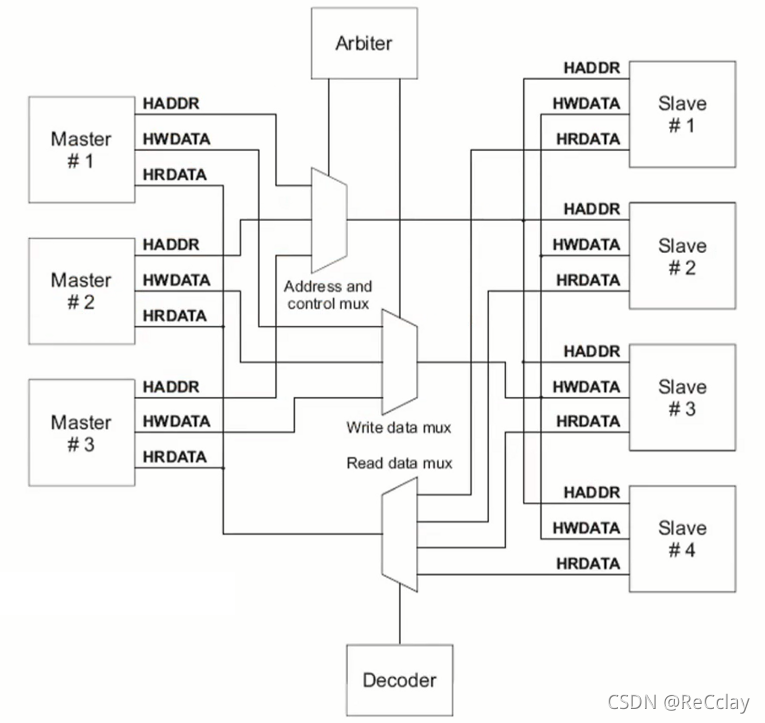

AHB总线从上图可以看到主要有三种类型的信号需要传输:

- HADDR

- 方向为 Master 到 Slave

- HWDATA

- 方向为 Master 到 Slave

- HRDATA

- 方向为 Slave 到 Master

总线上有多个Master和Slave,但是总线每个时刻只能有一个Master访问Slave,因此需要一个Arbiter来仲裁地址(HADDR)和写数据(HWDATA)。具体手段,在上图中就是通过Arbiter来选择MUX的某个输入信号,然后将MUX的输出信号送到各个Slave(共享总线的体现),各个Slave分别去译码,译中了之后会进行接收。每个 Slave 地址空间在系统中是唯一的。

各个Slave 的读数据(HRDATA)信号输入到MUX的输入端,然后通过Decoder来选择MUX的某个输入信号,然后将MUX的输出信号送到各个Matser(共享总线的体现)。这个Decoder是HADDR过来的,会去做译码,通过译码会知道这个命令是哪个slave所接收的,同样道理会去选择哪个slave返回的数据,然后返回到master中。

2.3、AHB 传输

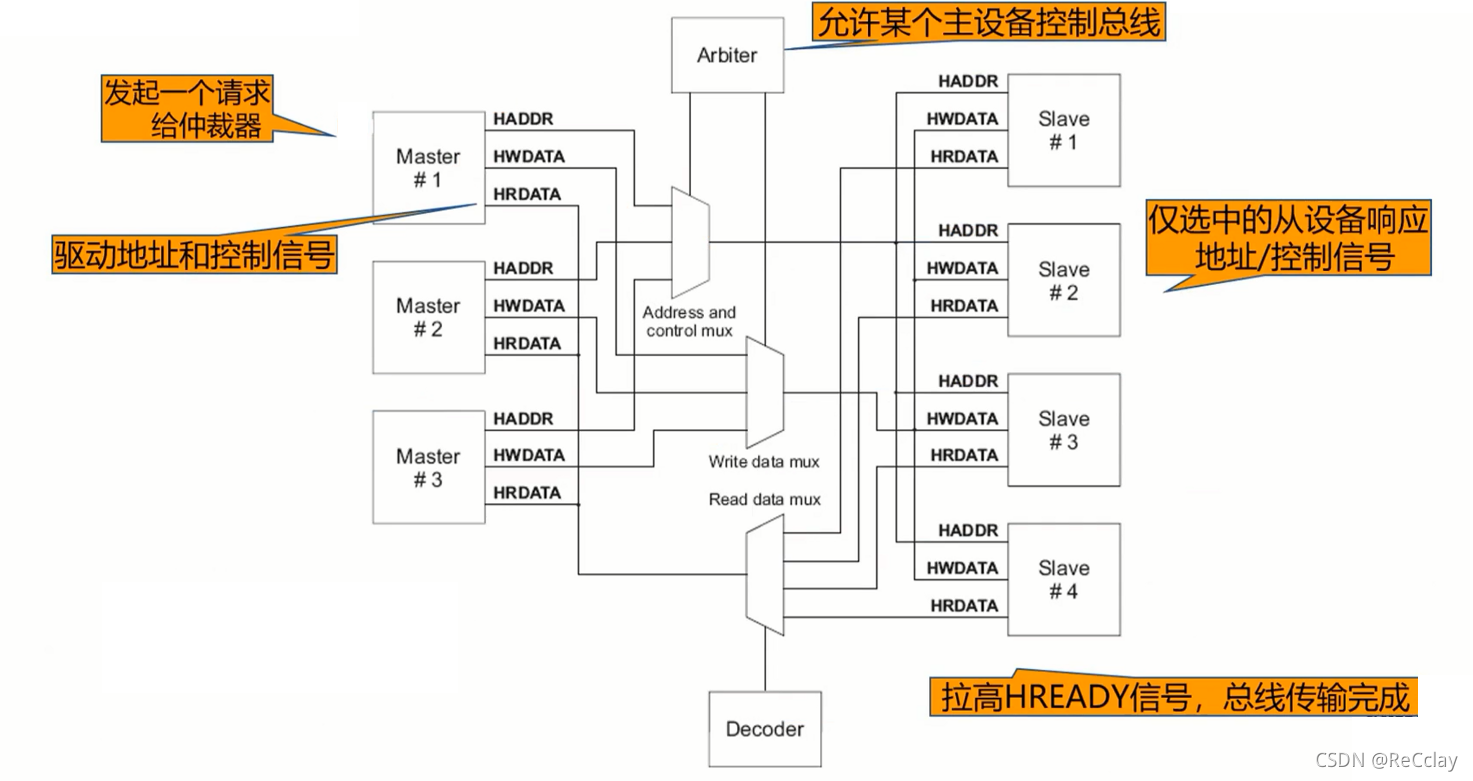

上图着重介绍了AHB传输的流程:首先Master发起一个请求给仲裁器(图中未标出),仲裁器会根据各个Master的请求把结果发送出来,分别去选择对应Master地址MUX和数据MUX输入。然后送到各个Slave,Slave本身会进行译码,决定要不要接收!

允许某个主设备控制总线含义:运行某个命令占用总线。举例来说:Master1运行读命令访问Slave2,得到仲裁了,Slave2返回响应之后,这个命令才算结束。结束之后,Arbiter才会将总线释放,去仲裁下一轮。对于Slave来讲,它会根据地址进行译码!

拉高HREADY信号,总线传输完成含义:Slave完成之后,在返回Data的同时会有一个握手Ready返回。代表我的这次访问已经OK了,告诉Master你的这次访问结束了,这样又可以重新申请总线了。

注:这个图面试的时候突击,学习的时候可以先做了解,更重要的还是后面将要介绍的AHB时序。另外,AHB总线目前很成熟都有现成的IP,通常不会要求面试者去设计,验证也非常成熟,故更多聚焦在Slave口的时序上!

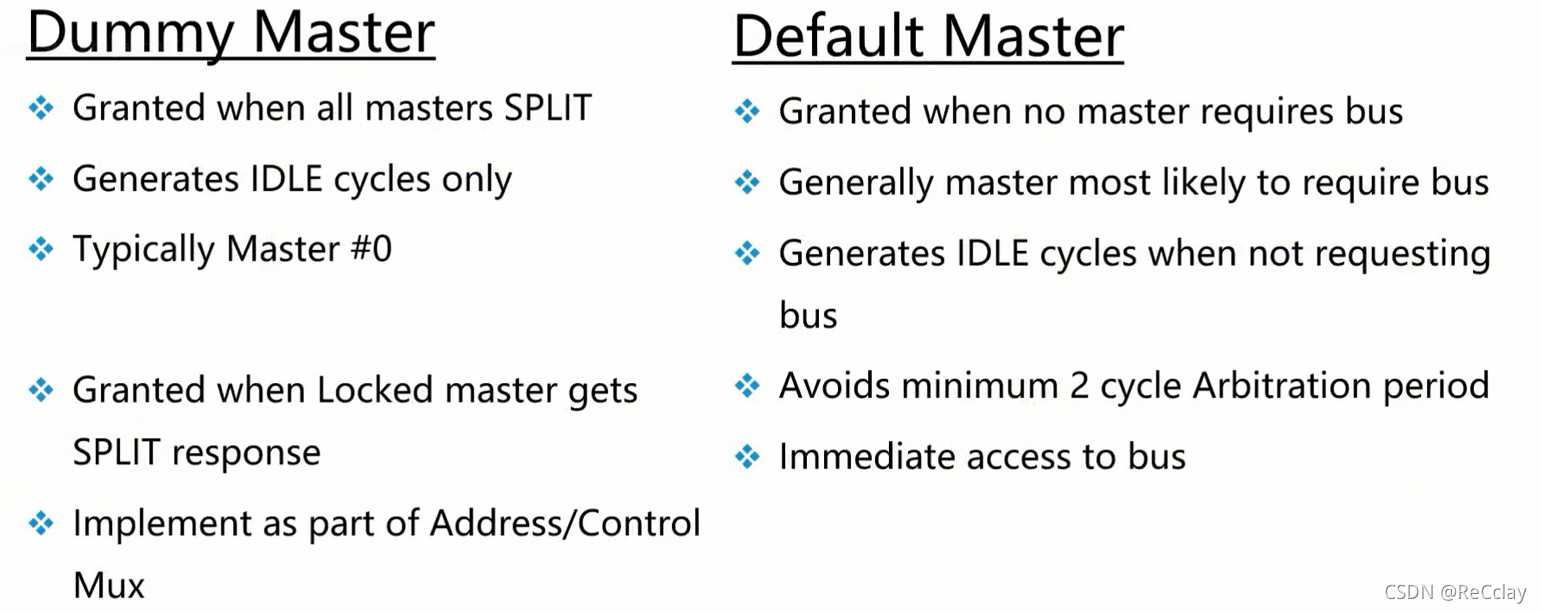

2.4、Dummy/Default Master

2.4.1、Dummy Master(用的不多)

- Granted when all masters SPLIT

- Dummy Master 意即 哑巴的Master,即只有当其他的Master没有响应的时候,它才会响应。防止总线挂死设计的一个Dummy Master。

- Generates IDLE cycles only

- IDLE 是TRANS中的一个类型,会有BUSY/IDLE这些状态

- Typically Master #0

- 通常会把Master0作为Dummy Master

- Granted when Locked master gets SOLIT response

(后面看到AHB时序,再回过头来看这些,因为这里面涉及一些信号,诸如:Locked、IDLE…)

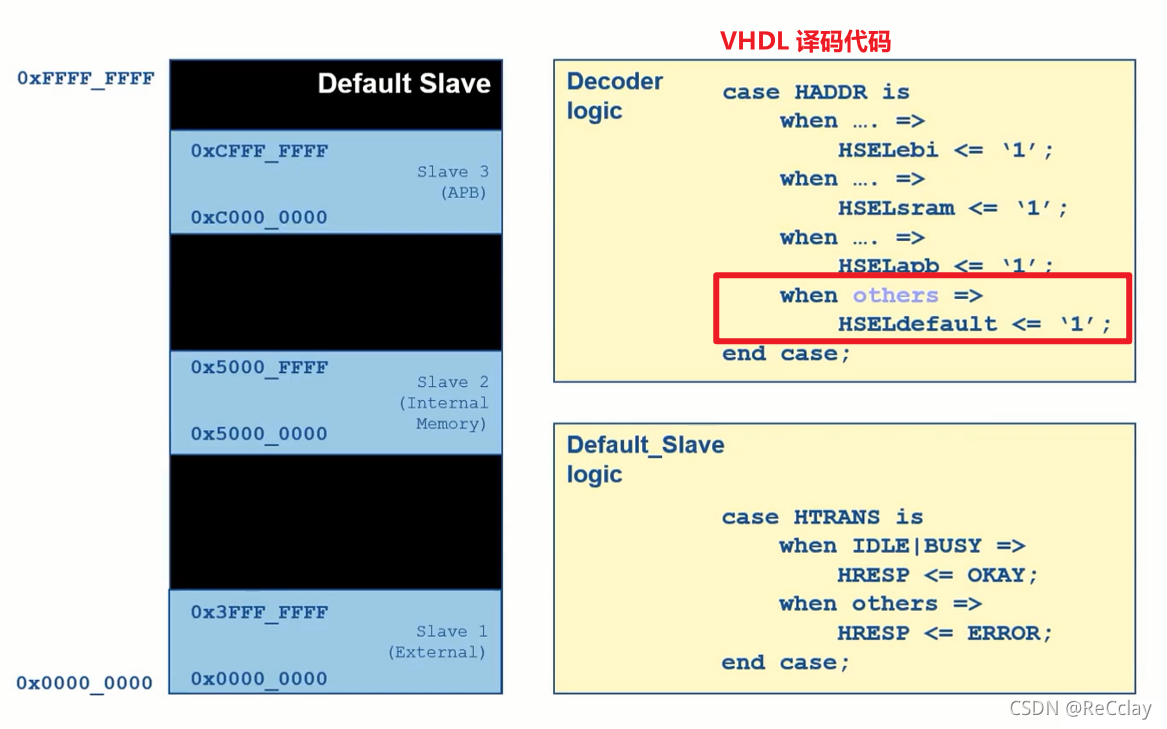

2.5、Default Slave

我们地址空间划分,空间很大,每个IP占据了一部分空间后,还有一部分空间是没有IP占用的,这部分空间叫默认空间。如果没有默认空间,那么命令过来,没有响应返回(握手机制),整个系统就会挂死。

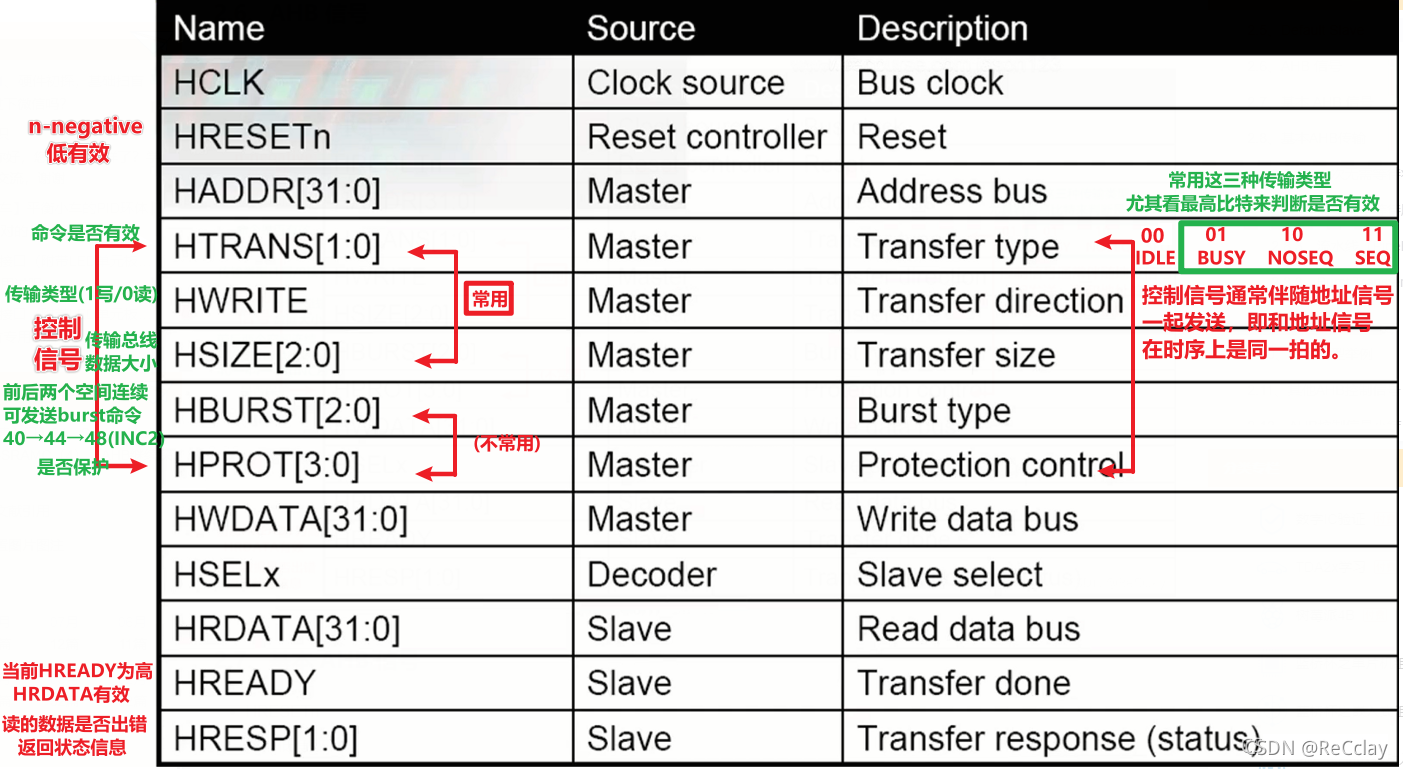

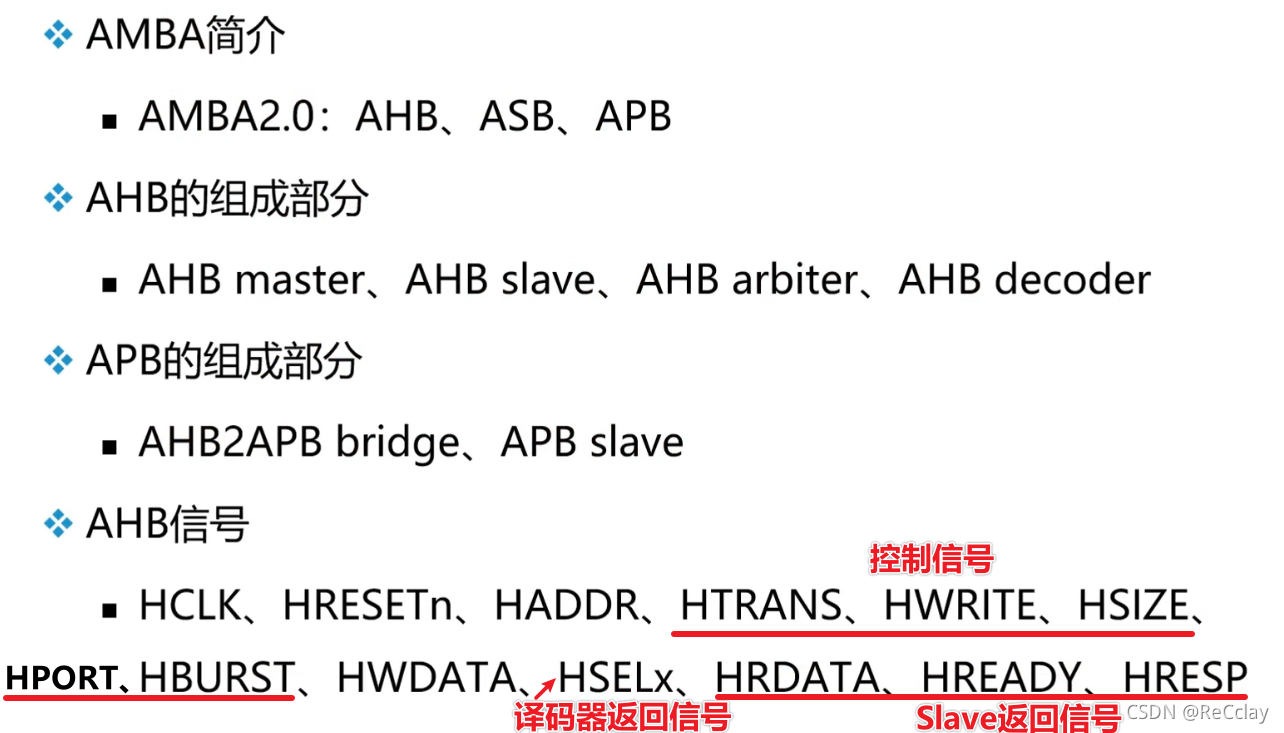

2.6、AHB 信号

2.7、基本 AHB 信号

- HRESETn

- 低有效

- HADDR[31:0]

- 32位系统地址总线

- HWDATA[31:0]

- 写数据总线,从主设备写到从设备(M → S)

- HRDATA[31:0]

- 读数据总线,从从设备读到主设备(S → M)

- HTRANS

- 指出当前传输的状态

- NONSEQ(10)、SEQ(11)、IDLE(00)、BUSY(01)

- NONSEQ(10)、SEQ(11)的使用目前在工业界是不做区分的,处理手法都是一样的!

- 指出当前传输的状态

- HSIZE

- 指出当前传输的大小

- HBURST

- 指出传输的burst类型

- HRESP

- 从设备发给主设备的总线传输状态

- OKAY、ERROR、RETRY(重传,很少用)、SPLIT(分离,很少用)

- 从设备发给主设备的总线传输状态

- HREADY(返回数据是否有效)

- 高:从设备指出传输结束

- 低电平:从设备需延长传输周期

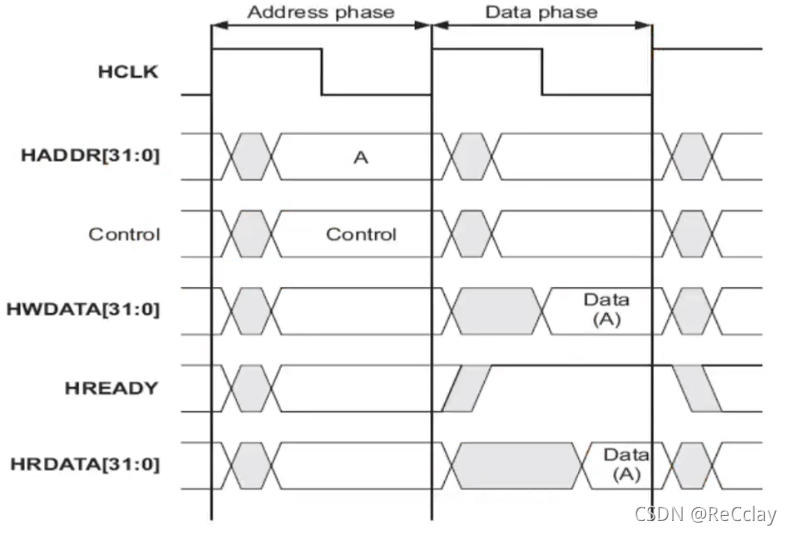

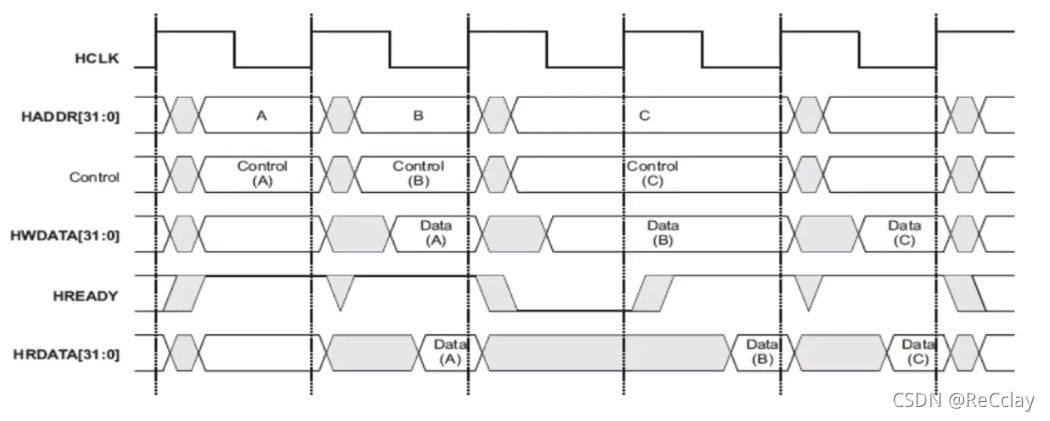

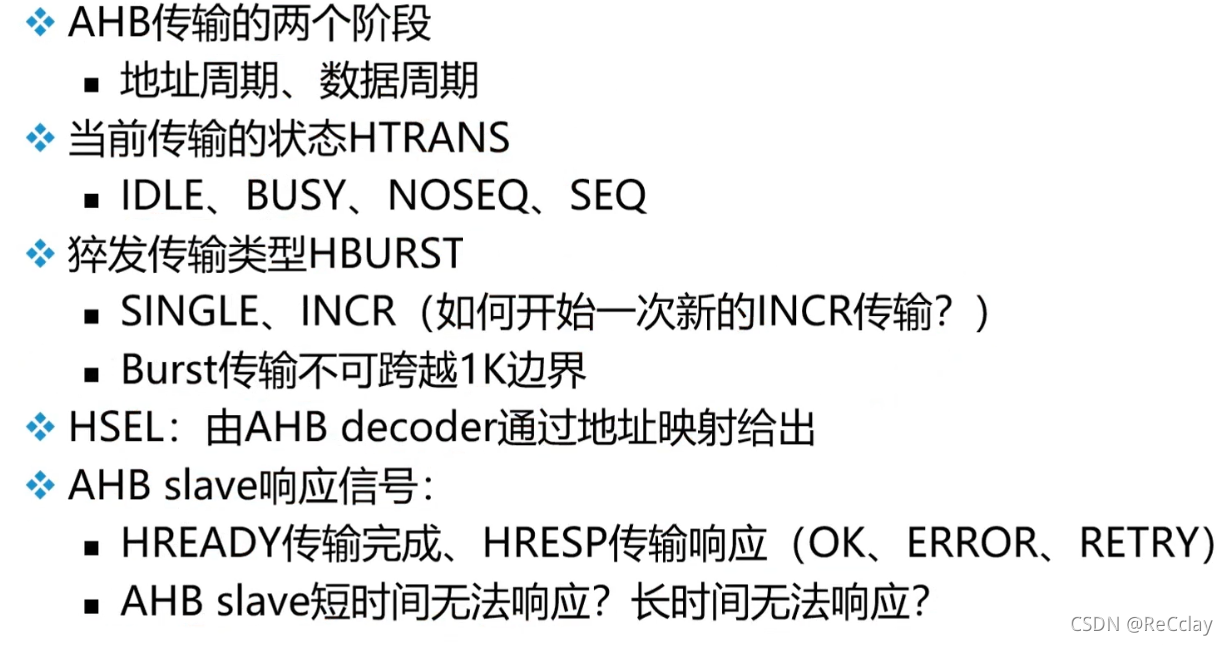

2.8、基本AHB传输

- 两个阶段

- 地址周期,只有一个cycle(控制信号和地址信号在同一拍)

- 数据周期,由HREADY信号决定需要几个cycle

- 流水线传送

- 先是地址周期,然后是数据周期

2.8.1、一次无需等待状态的简单传输

- 第一条竖黑线处:Master release address and control

- 第二条竖黑线处:Slave sample the address and control

- 第三条竖黑线处:Master sample the data

Q:如果slave没有ready?

- A:

HREADY在该周期为低!

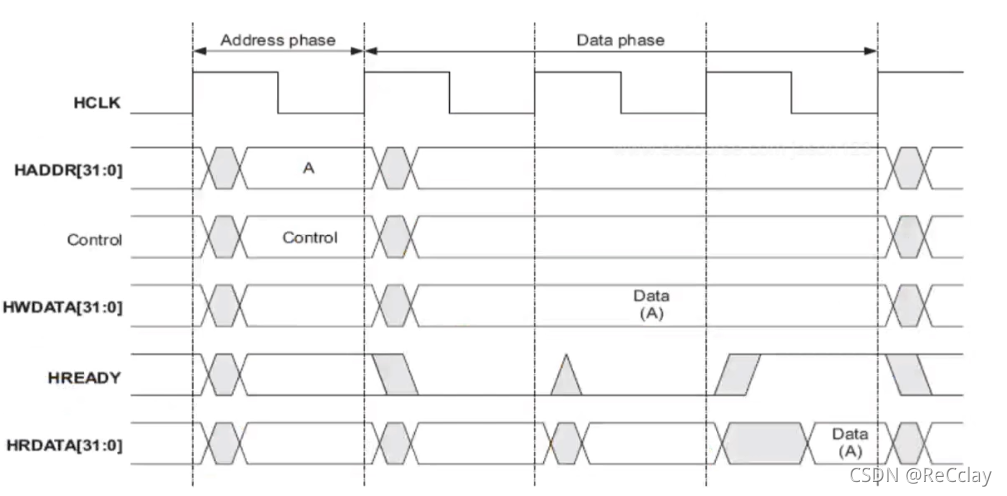

2.8.2、需要两个等待周期的简单传输

- 经过3拍

HREADY才为高,才能进行数据读取和数据写入操作。

2.8.3、流水线(Pipeline)

- 流水,即地址和数据同时发。

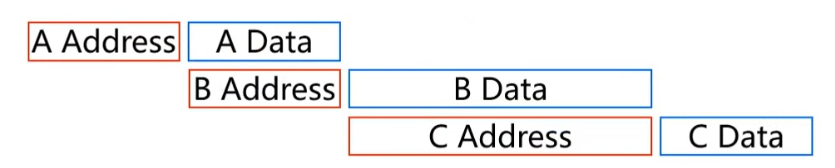

2.8.3、Burst Transfer(基本没用,作为了解即可!)

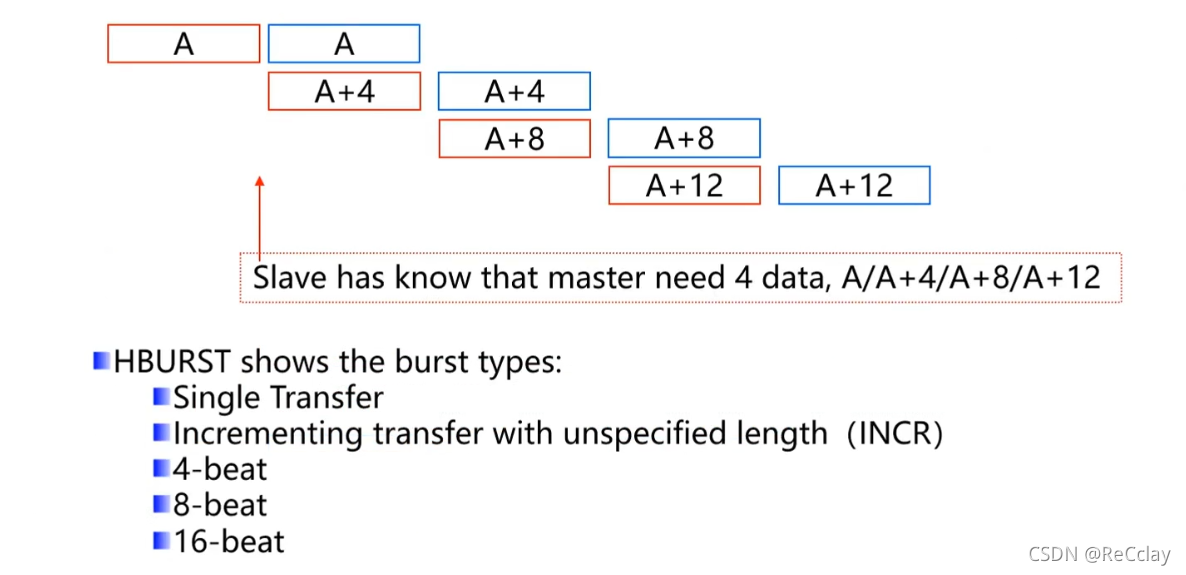

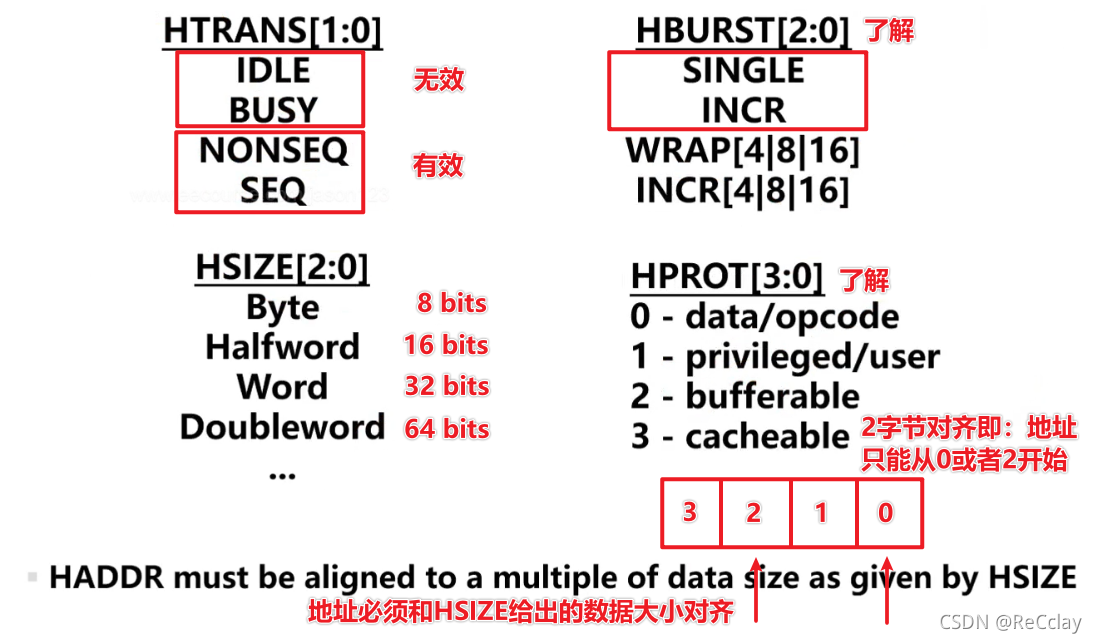

2.9、传输类型

- HTRANS[1:0]:当前传输的状态

- IDLE、BUSY、NONSEQ、SEQ(后两个合并用,不做区分)

- 00:IDLE(用得少)

- 主设备占用总线,但没进行传输

- 两次burst传输中间没有主设备发IDLE

- 01:BUSY(用得少)

- 主设备占用总线,但是在burst传输过程中还没有准备好进行下一次传输

- 依次burst传输中间主设备发BUSY

- 10:NOSEQ【single】

- 表明一次单个数据的传输(single)

- 或者一次burst传输的第一个数据

- 地址和控制信号与上一次传输无关

- 11:SEQ【Burst】

- 表明burst传输接下来的数据

- 地址和上一次传输的地址是相关的

注:实际使用的时候直接判断HTRANS的高位,为1表示有效(即NOSEQ/SEQ不做区分)。对于slave来讲也是不做SEQ和NOSEQ区分的,因为我们通常会把ADDR传过来,不会去关注是single还是burst!

注:这里仅仅作为概念去记忆即可,另外需要知道的一点,只有Burst才有SEQ,Single的时候只有NOSEQ!

2.10、传输类型举例

2.11、其他AHB控制信号

HWRITE

- 高电平(1):写

- 低电平(0):读

HSIZE[2:0]

- 000:8bits 100:128bits

- 001:16bits 101:126bits

- 010:32bits 110:512bits

- 011:64bits 111:1024bits

- 最大值受总线的配置所限制

- 通常使用32bits(010)

HPORT[3:0](不怎么用)【了解即可】

- HPORT[0]:OPCODE/DATA(操作数/数据)

- HPORT[1]:USER/PRIVILGED(普通用户/特权用户)

- HPORT[2]:Bufferable/Non-Bufferable

- HPORT[3]:Cacheable/Non-Cacheable

注:AHB现在多用于小的MCU,HPORT基本不会去用!

2.12、AHB控制信号小结

2.13、Review

Q:地址译码器的地址从哪里来?

- A:系统地址空间划分设计规定出来的,不同项目空间划分不同!每个AHB Slave都有一个HSEL,HSEL同时只会有一个有效!

Q:master 一次发4个地址,是对应不同的slave吗?

- A:4个地址要对应一个slave,四个地址通常来讲是连续的。

Q:HSIZE是说地址还是数据传输位宽?

- A:HSIZE指的是有效传输数据位宽。数据传输位宽一共是32位,通过HSIZE可以规定32位里面是有效传8/16位还是32位,没有24位。

- 如果有效8位,具体4个8位当中的哪个8位,由地址的[1:0]决定。如果地址[1:0]=0,表示数据的[7:0]有效;如果地址[1:0]=1,表示数据的[15:8]有效;如果地址[1:0]=2,表示数据的[23:16]有效;如果地址[1:0]=3,表示数据的[31:24]有效。

地址总线固定是32位(32系统),那么地址空间相当于4G。

Q:HBURST 作用?

- A:实际工程中这个信号其实没啥作用。协议中规定了:命令与命令之间访问地址空间连续,就可以第一个命令推算下一个命令地址。

- eg:

BURST 2;0x000C -> 0x000C 0x000D 0x000E 0x000F ; 0x0010 -> 0x0010 0x0011 0x0012 0x0013;作用:我发了一个命令且地址是0x000C,并告诉这个命令是BURST 2,代表我会连续发2个32位地址空间的访问。由于AHB协议中每个命令是把地址带上的, 故做slave的时候一般不看HBURST信号。

面试常问:画一画AHB时序信号?主要信号名字?每个信号作用?

边栏推荐

- [follow Jiangke University STM32] stm32f103c8t6_ PWM controlled DC motor_ code

- Stm32cubemx, 68 sets of components, following 10 open source protocols

- 【OBS】RTMPSockBuf_Fill, remote host closed connection.

- [make a boat diary] [shapr3d STL format to gcode]

- Ctfshow, information collection: web10

- Ctfshow, information collection: web1

- 15、文本编辑工具VIM使用

- Novel Slot Detection: A Benchmark for Discovering Unknown Slot Types in the Dialogue System

- 【目标检测】YOLOv5跑通VOC2007数据集

- 使用cpolar建立一个商业网站(2)

猜你喜欢

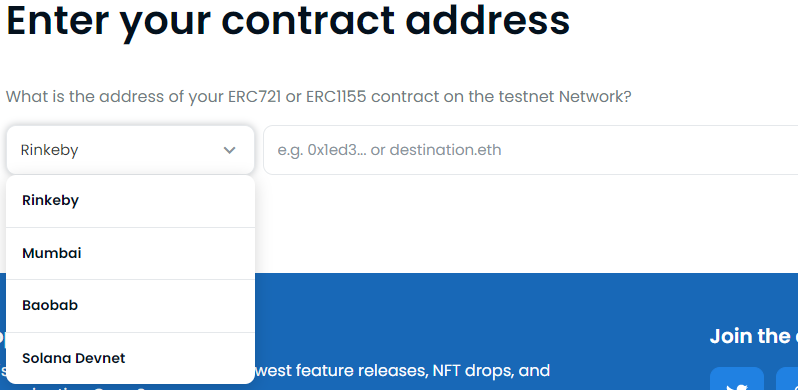

How to release NFT in batches in opensea (rinkeby test network)

With 8 modules and 40 thinking models, you can break the shackles of thinking and meet the thinking needs of different stages and scenes of your work. Collect it quickly and learn it slowly

Change win10 Screensaver

如何在opensea批量发布NFT(Rinkeby测试网)

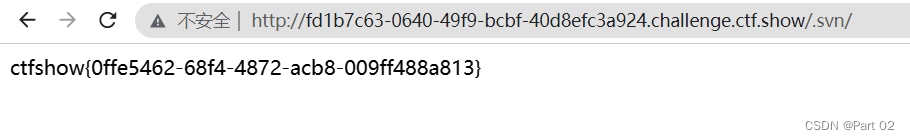

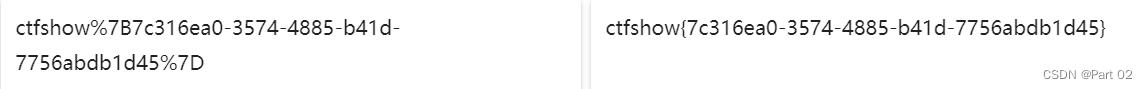

CTFshow,信息搜集:web8

Apache multiple component vulnerability disclosure (cve-2022-32533/cve-2022-33980/cve-2021-37839)

What is data leakage

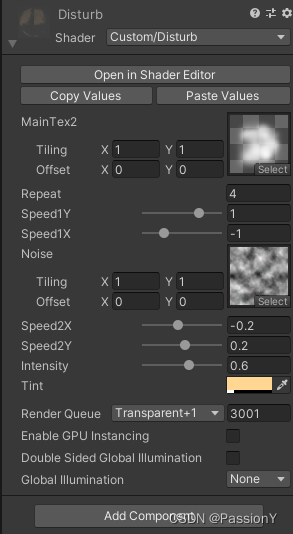

Unity's ASE achieves full screen sand blowing effect

Ctfshow, information collection: web13

CTFshow,信息搜集:web10

随机推荐

Ctfshow, information collection: web1

简述keepalived工作原理

Niuke real problem programming - Day12

“百度杯”CTF比赛 2017 二月场,Web:include

MySQL bit类型解析

Novel Slot Detection: A Benchmark for Discovering Unknown Slot Types in the Dialogue System

Ctfshow, information collection: web4

2. Heap sort "hard to understand sort"

With 8 modules and 40 thinking models, you can break the shackles of thinking and meet the thinking needs of different stages and scenes of your work. Collect it quickly and learn it slowly

Zhiting doesn't use home assistant to connect Xiaomi smart home to homekit

【搞船日记】【Shapr3D的STL格式转Gcode】

jacoco代码覆盖率

Runnable是否可以中断

微信小程序 01

使用Scrapy框架爬取网页并保存到Mysql的实现

最安全的证券交易app都有哪些

众昂矿业:萤石继续引领新能源市场增长

Use cpolar to build a business website (2)

Yyds dry goods inventory # solve the real problem of famous enterprises: cross line

[make a boat diary] [shapr3d STL format to gcode]