当前位置:网站首页>STM32 Basics - memory mapping

STM32 Basics - memory mapping

2022-07-07 10:11:00 【m0_ fifty-nine million nine hundred and forty-nine thousand fou】

Abstract : Want to put STM32 Single chip microcomputer can learn , The internal structure of the chip must be clear . So-called The foundation is not solid , The earth trembled and the mountains swayed . Today, let's take a look at STM32F429 Of Memory map.

STM32F429 Chip system architecture

STM32F429 It's using Cortex-M4 kernel , The kernel is CPU, from ARM Company design .ARM The company doesn't make chips , It's selling its chip technology license . Chip manufacturers (SOC) Such as ST、TI、Freescale, Responsible for designing components outside the kernel and producing the entire chip , These components outside the core are called peripherals or peripherals on chip . Such as GPIO、USART( A serial port )、I2C、SPI And so on are called on-chip peripherals .

From the above figure, we can clearly see that the chip and peripherals are connected through various buses , The main control bus has 8 strip , The controlled bus has 7 strip . Master bus Through one Bus matrix To connect Controlled bus , Bus matrix be used for Master bus Access arbitration management between , The arbitration adopts a circular scheduling algorithm . For example, data from Cotex-M4 To high-speed peripherals USB, The data is handed over to... After the bus matrix , The bus matrix will be awarded USB, And then through USB Where AHB1 Transferred to the USB.

Three buses

Instruction bus 、 data bus 、 The system bus

ICode Focus on transmission instructions ,DCode and System Focus on data transmission , As for the more detailed distinction , Don't care. . actually ICode、DCode and System The interior contains three parts , Address bus 、 Control bus 、 data bus .

High speed bus

Hang directly on Bus matrix What's on it ?

ICode、DCode、System;FLASH Connect the bus ;SRAM Connect the bus ; High speed peripheral connection bus AHB1/AHB2/AHB3; Connect “ Bridge ” Bus of .

these High speed bus Direct and Bus matrix come together , In fact, these high-speed buses are actually Bus matrix Extension of , Or part of the bus matrix .

Memory mapping

This picture is too important , Understand this picture , Yours STM32 You can already master 50% 了 , Let's focus on this picture . This picture is from STM32F429 Refer to manual No 84 page , Because the original is in English , Got a translated version .

3 Sorting and sharing of embedded IOT learning resources :C Language 、Linux Development 、 data structure ; software development ,STM32 Single chip microcomputer 、ARM Hardware development 、 Internet of things communication development 、 Comprehensive project development tutorial materials ; The real question of the written interview . Click the plug-in below to get it for free ↓↓↓

Order me to collect s.pdb2.com/l/CMIsoKcnATFIF4M

1、STM32 Storage space

How much memory space can the chip access , Who made the decision ? This is made by the chip CPU The number of address buses depends on ,STM32 The address bus inside the chip is 32 root .

1 Root address line : The address that can be transmitted is 0 and 1 Of , Then you can theoretically access 2 Bytes .

2 Root address line : The transmission address can be 00、01、10、11, Theoretically, you can access 4 Bytes .

3 Root address line : The address that can be transmitted is 000、001、010、011、100、101、110、111, Theoretically, you can access 8 Bytes .

32 Root address line : Can produce 00000000 00000000 00000000 00000000 — 11111111 11111111 11111111 11111111 Of 2^32 An address , The range is just 4G, So we say STM32 Of 32 Root address line , Theoretically, you can access 4G Bytes of memory space .

You can see it on the far right of the figure above STM32 The address is from 0x00000000 To 0xFFFFFFFF, This is it. 4GB Storage space . however STM32 There is really 4GB Is there enough storage space ?

What are you thinking ? The answer, of course, is not , our PC Computers are just 4GB Of memory . How can a small single chip microcomputer have 4GB Storage space ! This 4GB Yes. STM32 Theoretically allocated address space . In other words, there is not such a large storage unit . In the second row of the figure above, you can see that there are many reserved addresses , These addresses did not assign him a storage unit .

All memory is connected to the address line , But in fact, if you only take one 10M The memory of , And from 0 Address start mapping , that 32 Generated by the root address line 0~10M The address signal is actually meaningful , Because these address signals have corresponding real memory , And the resulting 10M The above address signal is actually meaningless , Because it doesn't correspond to real memory .

for instance , The government has changed you 10 The area of the building is used to build a house , But actually you don't have that much money , Only covered 3 building , Other 7 The reserved area of this house can only be put there , So you should understand .

STM32 Medium 32 yes 32 Does the root address line mean ?

answer : No ,STM32 Of 32 No 32 Root address line means , It means MCU Inside the chip CPU When processing data , Data that can be processed every time The seat width is 32 individual bit. That's why ,STM32 The internal register size is 32 Bit , Just equal to the bit width .

A chip is 32 Bit , But its address line can only 16 root 、 perhaps 8 root , about STM32 Come on , It happens that ,CPU Data that can be processed A wide And the number of address lines is just 32, So many friends are often confused , Think it's the same thing .

2、 What is memory mapping

Mapping is actually Corresponding It means . in fact The memory itself does not have an address , Assign the theoretical address of the chip to the memory , This is it. Memory mapping .

For example, to understand : For example, the one mentioned earlier 10M Examples of memory , This 10M Memory has no address , I will 10M Memory mapping to theory 32 The root address line can transmit 4G An address signal , Each address signal accesses one byte ,4G Address signals can access 4G Bytes , So theoretically, the accessible range is 4G.

Address 0 Later 10M Range , this 10M There is a memory of 0—10M The address of , Generated by the address line 0~10M Address signals between , You can access 10M This real memory . As for the production of chips , How to realize the mapping we described in terms of process and Technology , We don't need to care about .

3、STM32F429 Memory mapping for

STM32 All of the Inside and outside the film It's all memory , So all these memories need to be mapped , It's just theoretical 4G Wide range and actual memory space , In other words, the actual memory space does not 4G.

Memory is very expensive , One STM32 If there is a single chip microcomputer 4G Memory words , That's very expensive , And SCM products do not need such a large storage space .

Theoretically The address starts with the house number , Every byte in the memory is a room , After the memory is produced , These rooms have no address ( House number ), The mapping process is actually to assign these house numbers to these rooms , After distribution , Each house number can only access its own room , An address that is not assigned is a reserved address , The so-called reserved address means , There is no corresponding actual storage space .

Can you keep some addresses unallocated ?

Certainly. , Because theoretically there can be 4G The address of , But it's actually impossible to give you 4G Storage space , Otherwise, you can't afford to buy this chip ,PC The memory of the machine is just 4G/8G, How can SCM really give you 4G Storage space ?

Register mapping

The memory itself has no address , The process of assigning addresses to memory is called memory mapping , What is register mapping ? What exactly is a register ?

In memory Block2 This area , That is, the address from 0x4000000—0x5FFFFFF This area , The design is peripherals on chip , They use Four bytes are a unit , common 32bit, Each unit has its own function , When we control these units, we can drive the peripherals to work . You can find the starting address of each unit , then adopt C Language pointer to access these units , If you access through this address every time , Not only bad memory, but also easy to make mistakes , Smart engineers are based on the different functions of each unit , Give this memory unit an alias in the name of function , This alias is what we often call register , This process of aliasing memory units with specific functions that have been assigned addresses is called register mapping .

This picture is clear enough !

So if I want to go 0x40020410 Write a value to this address 0xFFFF, How to operate it ?

Just need the following sentence ?

*(unsigned int*)(0x4002 0410) = 0xFFFF;

I always thought this sentence was very clear , But I found that some people can't understand this sentence , Let me explain :

First, the compiler doesn't know 0x40020410 It's something , It may mean kitten , It may also mean a puppy . But we know this 16 A hexadecimal number is an address, right ? So how to turn it into an address ?

Is it right to add (unsigned int*) become (unsigned int*)(0x40020410) Just turn this number into a pointer, that is, an address ? But we operate on the contents of this address , Is there another one in front asterisk become *(unsigned int*)(0x40020410) That's all right. , Then you can assign a value to it :*(unsigned int*)(0x4002 0410) = 0xFFFF;

Address remapping

Bootstrap (bootstrap) Computer equipment uses hardware loaded programs , Used to initialize enough software to find and load a fully functional operating system . It is also used to describe the process of loading bootstrap program . What is the bootstrap of single chip microcomputer , The bootstrap of single chip microcomputer is the startup of single chip microcomputer .

We said , SCM programs are basically from 0 The address of the starting operation ,F429 Of 0x00000000-0x001FFFFF What memory does the address map to , Then the instruction should be read from the memory , Began to run .

As for the 0x00000000-0x001FFFFF What memory is mapped to , This depends on F429 chip BOOT1、BOOT0 The level values of these two pins , To put it bluntly , adopt BOOT1 and BOOT0 The level value of the pin , You can choose to 0x00000000-0x001FFFFF Map to different memory .

STM32 Intraslice FLASH In two parts : Main memory block 、 Information block . Main memory block ( Lord Flash) For storing programs , Our program is written here . The information block is divided into two parts : System memory ( System FLASH)、 Option bytes . The system memory stores the startup program stored in the bootstrap mode of the system memory (BootLoader), When using ISP When loading the program , It is this program that executes . This area is written by the chip factory BootLoader, Then lock it , Users cannot change this area . The option byte stores the configuration information of the chip and the protection information of the main memory block .

Lord FLASH The address of

Lord FLASH The address is 0x0800 0000-0x081FFFFF,Jlink Download FLASH Whether the setting is through Jlink Downloaded to the address 0x08000000 The place of , Size is 0x00100000, That is to say 1MB.

doubt : Obviously, the code is downloaded to 0x80000000 In the next storage space , Why is the operation from 0x00000000 The address is running ? Why not from 0x80000000 It started running ?

About this question , That's what we said The bootstrap of single chip microcomputer .

Normally, it is mapped to the master FLASH On , So it's all from the Lord FLASH It started on , In order to learn from FLASH start-up , We need to download the code to the main FLASH On .

What is address remapping

If 0x00000000-0x001FFFFF It was mapped in System memory perhaps The embedded SRAM Upper , Now change BOOT0、BOOT1 The level of is 0、x.0x00000000 -0x001FFFFF It is remapped in Lord FLASH On , This is the MCU Address remapping .

Remapping is originally mapped with Zhang San , Now change to map with Li Si . In other words, remapping is 0x00000000 -0x001FFFFF(1MB) Originally mapped to System memory 0x1FFF 0000-0x1FFF7A0F(30KB) above , Now it maps to Lord FLASH 0x08000000 -0x081FFFFF(1MB) above .

Select from Lord FLASH Startup time , obviously FLASH Will be mapped to two addresses .

- The original mapped address (1MB):0x08000000-0x081F FFFF, Conduct Jlink Use this address when downloading

- Remapped address (1MB):0x00000000-0x001F FFFF, Startup time CPU Is to read instructions from the remapped address

Both addresses are valid , Remap to FLASH After the ,CPU from 0 When the address starts running , From FLASH Upper read instruction , Of course, the premise is that we need to download the code FLASH in .

This explains Why are we keil The download address of the program set in is 0x8000000, But the power on of single chip microcomputer is really from 0 Start execution . Because we set up... On the hardware BOOT0=1,BOOT1=X, This leads to the main FLASH District ( Also called main flash memory , size 1MB) It's mapped to 0x00000000-0x001FFFFF(1MB), So the code is downloaded to 0x80000000 In the next storage space , But the operation is from 0x00000000 Address running .

doubt : When the download , Can I use 0x00000000 Address to download ?

answer : This will not do , Because when downloading ,0x00000000-0x001FFFFF Has not been remapped to FLASH On , Only use 0x08000000 To download .

It says that we use JLink Downloader download code , But sometimes we also hear that we can download programs through serial port , What's going on ?

Download the program through serial port , That's what we're talking about ISP Program in the system . Boot from system memory , namely STM32 Of ISP 了 . At this time, the hardware circuit B00T0=1,B00T1=0. Because the serial port can not directly download the program to the main port FLASH Inside , So we need to use the ST Embedded in the system storage area of the company Bootloader To guide the download of the program to the main FLASH Inside .JLink Can directly download the program to the built-in FLASH Inside , Because JLink There is... Inside the downloader Bootloader To guide the download of the program to FLASH Inside . After downloading the program, you need to configure BOOT Pin for BOOT0=0,BOOT1=X( That is, start from the main flash memory ), The program can be started normally after reset . If you don't modify BOOT Pin, that is B00T0=1,B00T1=0, that 0x0000 0000 - 0x001FFFFF Whether it is remapped to the system memory , And the program code is in the main FLASH Inside . The program will not work properly after you reset , It can only be configured after downloading the program through serial port BOOT Pin for BOOT0=0,BOOT1=X, The code can be executed normally after reset . Do you understand ?

summary : Use JLink Download code ,JLink Inside the downloader Bootloader Download the boot program to Lord FLASH Inside . Use serial port to download code , Because the serial port does not Bootloader, Then use ST The official built-in memory area of the chip system Bootloader Code , Stop the program boot download FLASH. And because the program is from 0 Started , So when we run the program after reset, we must let BOOT0=0,BOOT1=X, take 0x00000000-0x001FFFFF Is remapping to Lord FLASH Where our code exists , from 0 Start executing code .

The figure below shows the use of FlyMcu Serial port download program , This serial port is USB-TTL, When downloading the program, let BOOT0=0,BOOT1=X that will do . It doesn't mean that programming in the system needs to B00T0=1,B00T1=0 Do you ? This is because we use this software , This software can be through DTR and RTS change BOOT Pin level , Achieve without modification BOOT Pin can download the running code , In fact, the software has made changes for us BOOT Pin operation , See the above description for specific introduction .

About ISP And IAP

The difference between the two has been explained in detail above , Here is a summary .

ISP In system programming , It refers to programming the chip directly on the target circuit board , You usually need a bootstrap program (BootLoader) To execute .ISP It's also called ICP In circuit programming 、 Online programming .

IAP Programming in applications , After the final product leaves the factory , The user program is programmed by the end user in use , Realize online upgrade .IAP It is required to divide the procedure into two parts : Bootstrap 、 User programs . The boot program is always the same .IAP It's also called programming in a program .ISP And IAP The difference is that ,ISP Generally, it is to reprogram the whole chip , Using the bootstrap program of the chip factory . and IAP Just part of the update program , It is developed by the electric appliance factory IAP Bootstrap . Taken together ,ISP More limited , and IAP Because it is a self-developed program , It's easier to change the program .

End

Reprinted from : Younger martial brother Guoguo

The article comes from dry goods |STM32 Basic knowledge of — Memory mapping

Link to the original text : https://mp.weixin.qq.com/s/BaC2

边栏推荐

- Deconvolution popular detailed analysis and nn Convtranspose2d important parameter interpretation

- Integer inversion

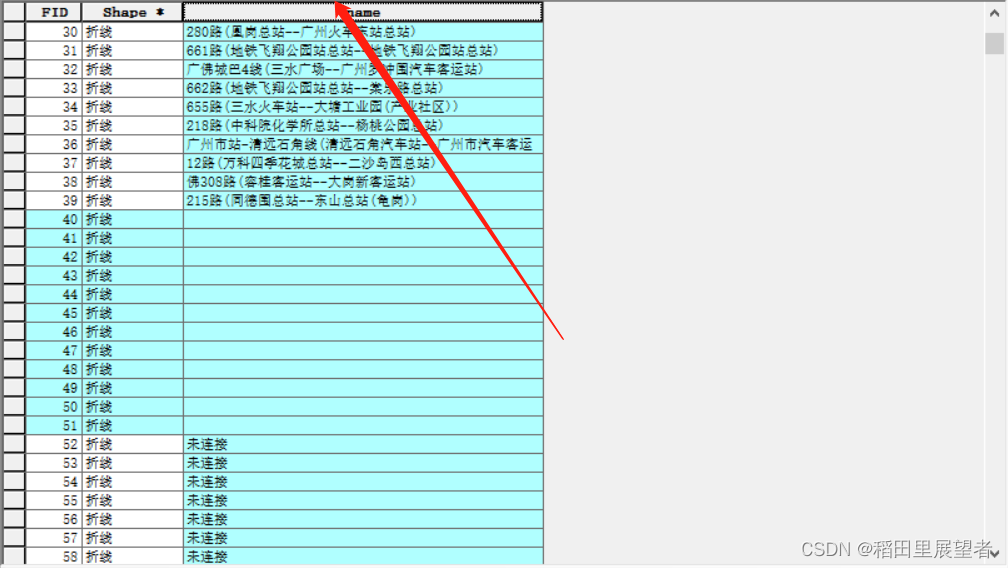

- ArcGIS operation: batch modify attribute table

- ORM模型--数据记录的创建操作,查询操作

- The Himalaya web version will pop up after each pause. It is recommended to download the client solution

- Methods of adding centerlines and centerlines in SolidWorks drawings

- 单片机(MCU)最强科普(万字总结,值得收藏)

- LLVM之父Chris Lattner:为什么我们要重建AI基础设施软件

- [ORM framework]

- LLVM之父Chris Lattner:為什麼我們要重建AI基礎設施軟件

猜你喜欢

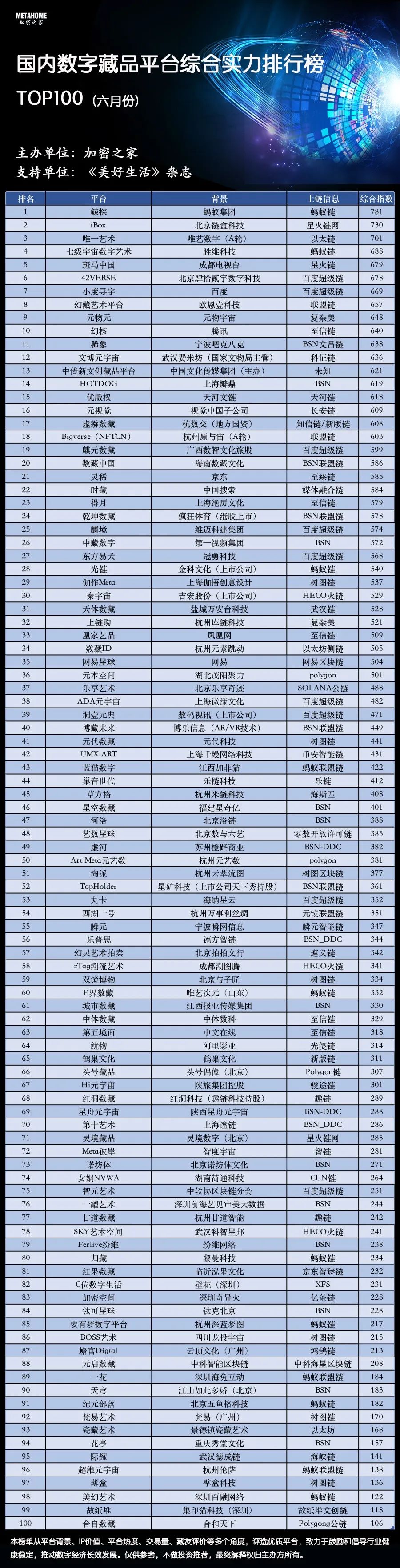

官媒关注!国内数字藏品平台百强榜发布,行业加速合规健康发展

ArcGIS operation: batch modify attribute table

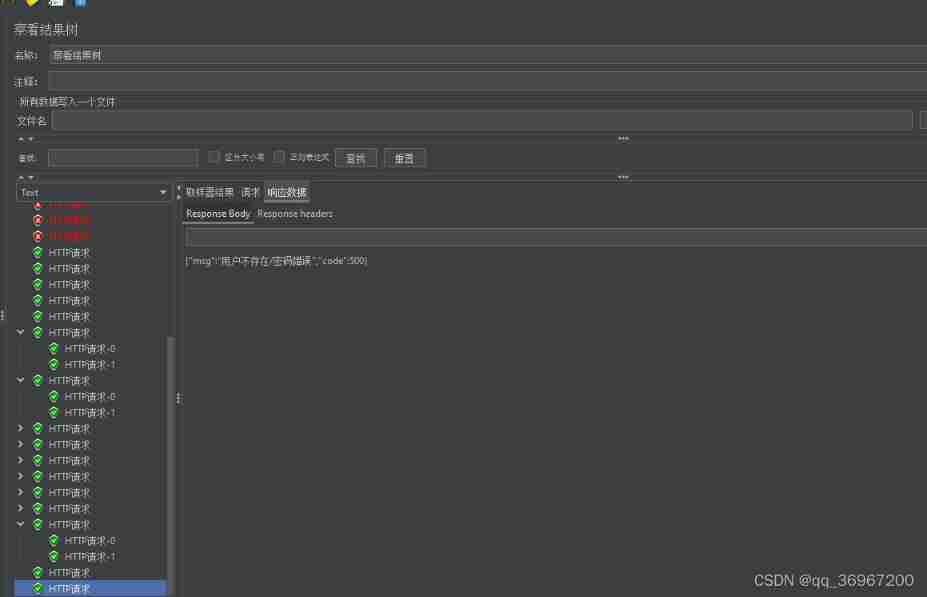

Basic use of JMeter to proficiency (I) creation and testing of the first task thread from installation

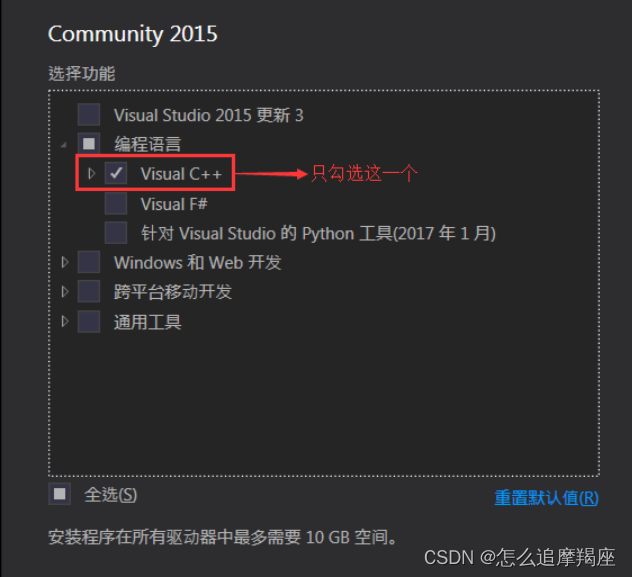

Win10 installation vs2015

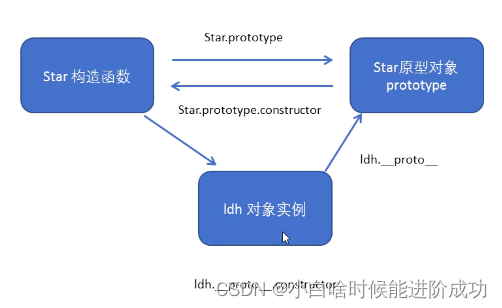

Es classes and objects, prototypes

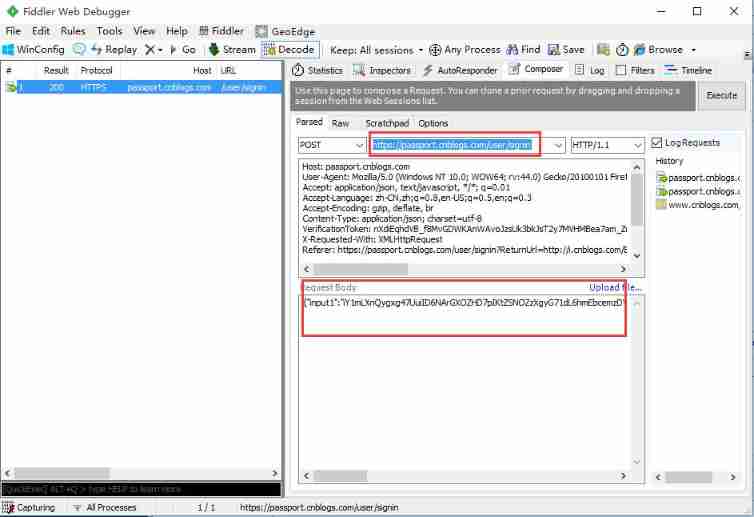

Fiddler simulates the interface test

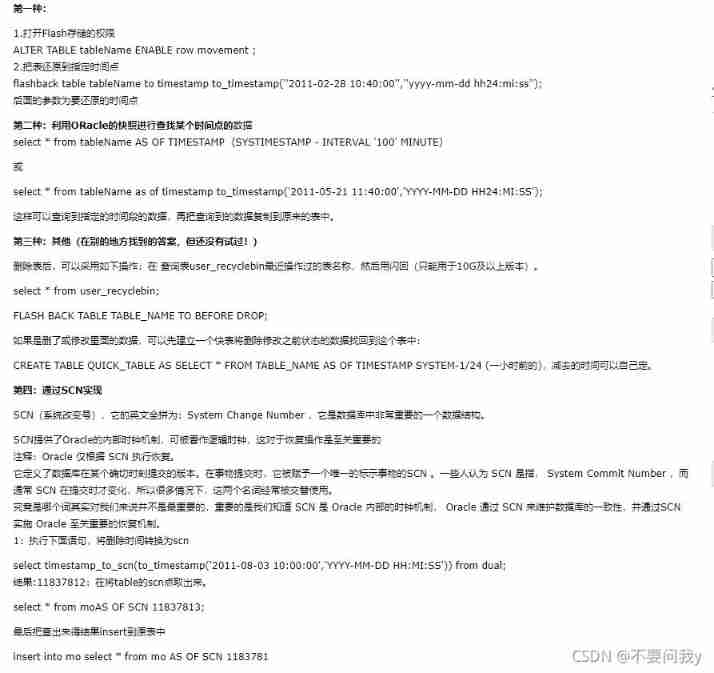

Delete a record in the table in pl/sql by mistake, and the recovery method

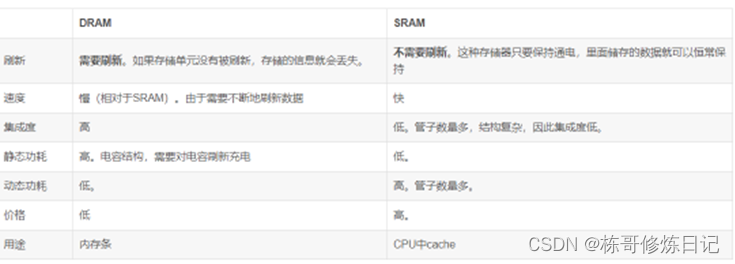

内存==c语言1

Fiddler break point

能源路由器入门必读:面向能源互联网的架构和功能

随机推荐

There is a problem using Chinese characters in SQL. Who has encountered it? Such as value & lt; & gt;` None`

Why does the starting service report an error when installing MySQL? (operating system Windows)

Why are social portals rarely provided in real estate o2o applications?

中国首款电音音频类“山野电音”数藏发售来了!

ORM模型--关联字段,抽象模型类

企业实战|复杂业务关系下的银行业运维指标体系建设

The Himalaya web version will pop up after each pause. It is recommended to download the client solution

Arcgis操作: 批量修改属性表

Do you have a boss to help look at this error report and what troubleshooting ideas are there? Oracle CDC 2.2.1 flick 1.14.4

Bit operation ==c language 2

Delete a record in the table in pl/sql by mistake, and the recovery method

Fiddler simulates the interface test

Internship log - day04

Qualifying 3

Performance optimization record of the company's product "yunzhujia"

The landing practice of ByteDance kitex in SEMA e-commerce scene

喜马拉雅网页版每次暂停后弹窗推荐下载客户端解决办法

ORM -- database addition, deletion, modification and query operation logic

Wallys/IPQ6010 (IPQ6018 FAMILY) EMBEDDED BOARD WITH ON-BOARD WIFI DUAL BAND DUAL CONCURRENT

Luogu p2482 [sdoi2010] zhuguosha