当前位置:网站首页>Chapter 6 data flow modeling

Chapter 6 data flow modeling

2022-07-01 23:33:00 【Jiangnan small workshop】

Data flow modeling

Continuous assignment

The continuous assignment statement is verilog The basic statement of data flow modeling , Used to deal with Wire network Assign a value .

This thing is equivalent to gate level description , But it describes the circuit from a higher abstract point of view .

Consecutive assignment statements must be in the form of the keyword

assignStart .Continuous assignment statements have the following characteristics :

- The value on the left must be a scalar / Vector network / The splicing of scalar and vector line nets , Choose one of the three , It cannot be a vector or a vector register .

- Always active , As long as one operand changes , The expression is immediately recalculated , Reassign .

- Operands can be scalars / Vector nets or registers / Function call .

- The assignment delay can be used to control the time when a new value is assigned to the network , Similar to door delay .

give an example

//out It's a network ,in1, in2 It is also a network assign out = in1 & in2; // addr yes 16 Bit vector line network // addr1_bits, addr2_bits All are 16 Bit vector register assgin addr[15:0] = addr1_bits[15:0] ^ addr2_bits[15:0]; // Splicing assign { c_out, sum[3:0]} = a[3:0] + b[3:0] + c_in;

Implicit continuous assignment

See this hidden word , I know , There must be something missing .

Online statement at the same time , Assign a value to it . The network can only be declared once , Therefore, there can only be one implicit continuous assignment .

// Normal assignment wire out; assgin out = in1 & in2; // It is equivalent to wire out = in1 & in2;

Implicit network declaration

Empathy , Since you can hide

assgin, That can be hiddenwireDo you ?Of course, it can be

// out No network statement is made for it , The simulator will infer out Is an implicitly declared network wire in1,in2; assgin out = in1 & in2;

Delay

- Delay in consecutive assignment statements , Used to control the time interval between any operand changes and the statement lvalue is given a new value ( To put it bluntly , When does the value on the left change , This time can be artificially defined ).

- Specify the method of assignment delay :

- Normal assignment delay

- Implicit continuous assignment delay

- Network declaration delay

Delay of ordinary assignment

- Specify the value of the delay in the continuous assignment statement , The delay value is located at

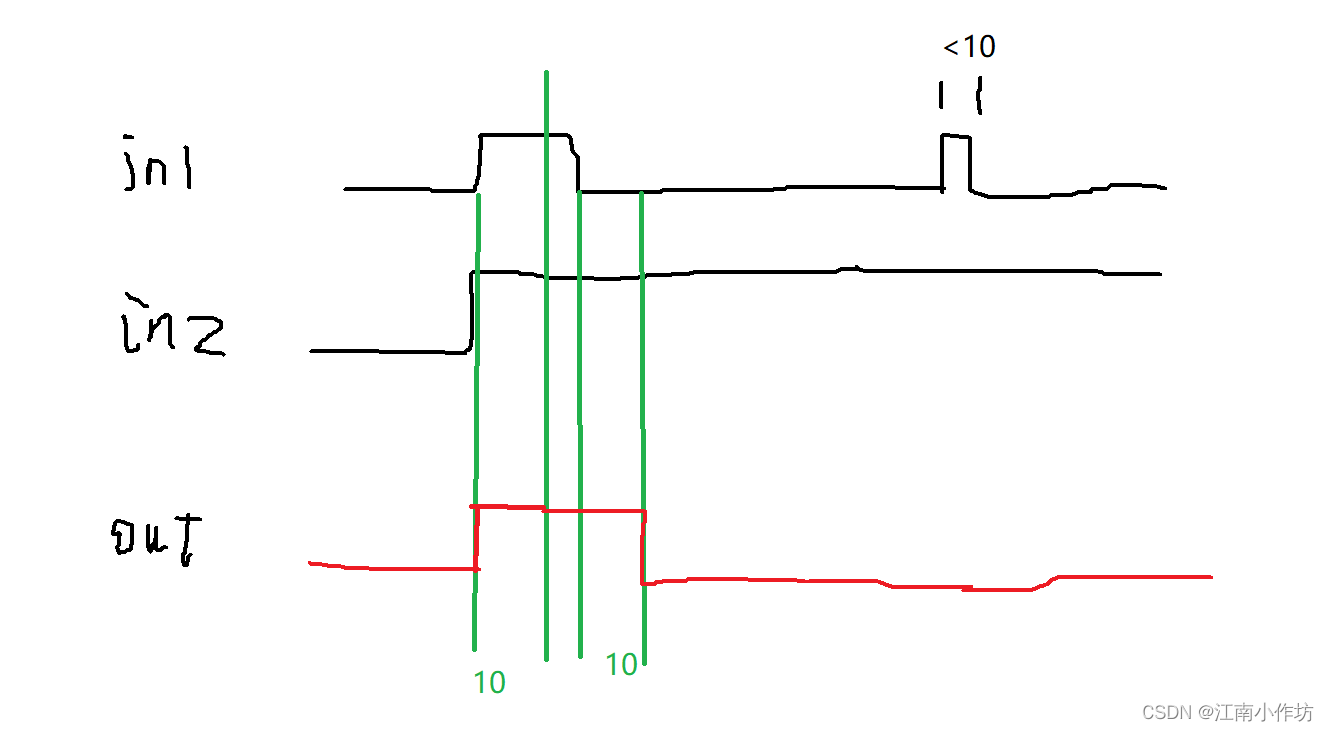

assginBack .assgin #10 out = in1 & in2; - Inertia delay : In the example above ,

in1 & in2The new value of , Before assigning to the left , Yes 10 Time unit delay , If in this 10 In units of time ,in1 & in2The value of has changed again , The new value of the assignment expression is retrievedin1 & in2The current value of the . This property is inertia delay .

- As shown in the figure , Signals smaller than the delay time are shielded , Because I just planned 10 Time unit assignment 1 to out, result in1 I become 0 了 , therefore out by 0. It can be used to shield pulse signals with short time .

Delay of implicit continuous assignment

- Empathy , The concept is the same , It's just that the assignment method has changed .

// Implicit continuous assignment wire #10 out = in1 & in2; // Equivalent to wire out; assign #10 out = in1 & in2;

Delay of network declaration

- Empathy , The concept is the same

// Network delay wire #10 out; assgin out = in1 & in2; // Equivalent to wire out; assign #10 out = in1 & in2;

expression

Data flow modeling uses expressions to describe the design . expression 、 Operators and operands are the basis of data flow modeling .

expression : Composed of operators and operands , The purpose is to calculate a result according to the meaning of the operator .

a ^ b addr[20:17] + addr[20:17] in1 | in2Operands : Operands can be any data type defined ,

The operator : An operation on an operand produces a result .

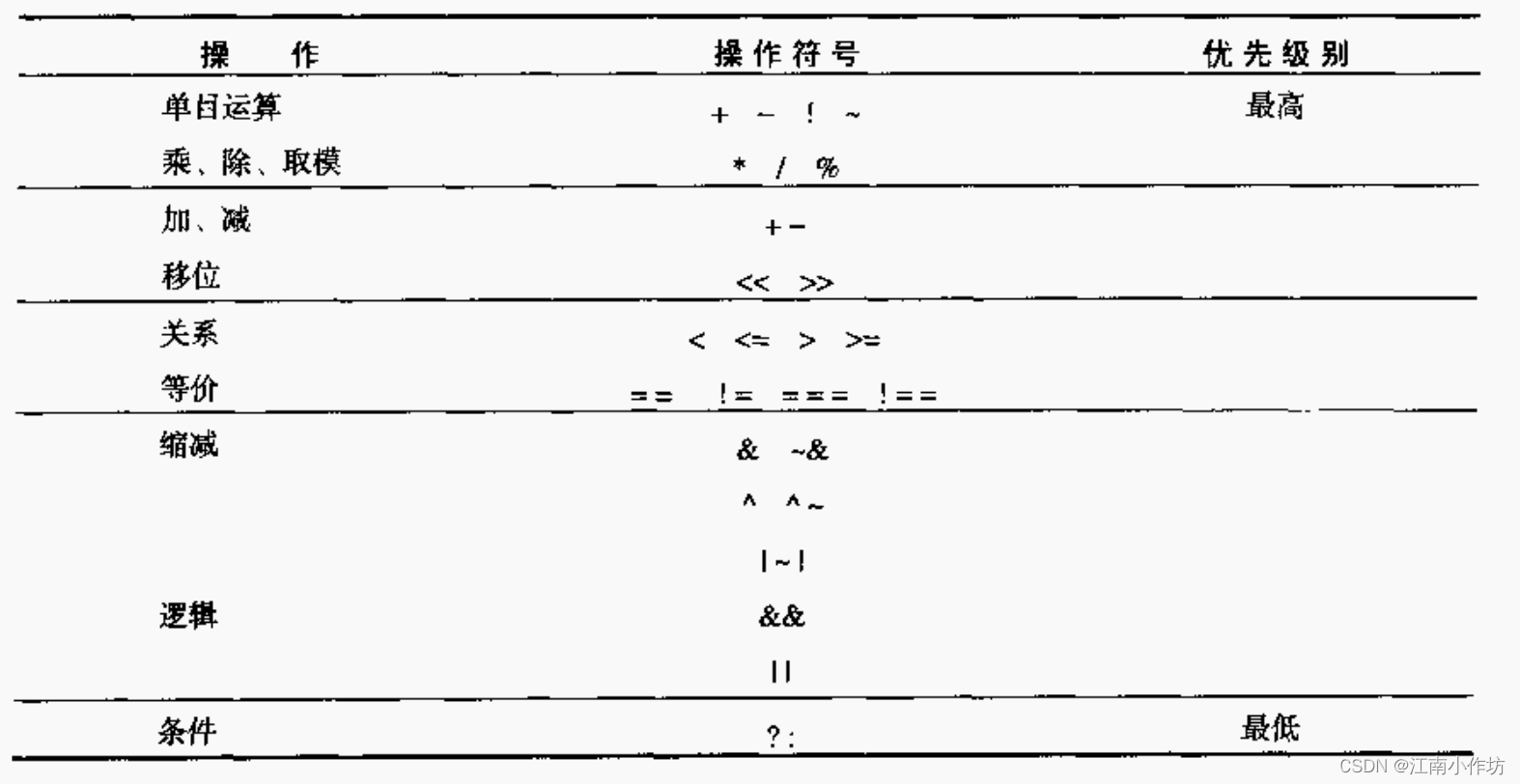

Operator type

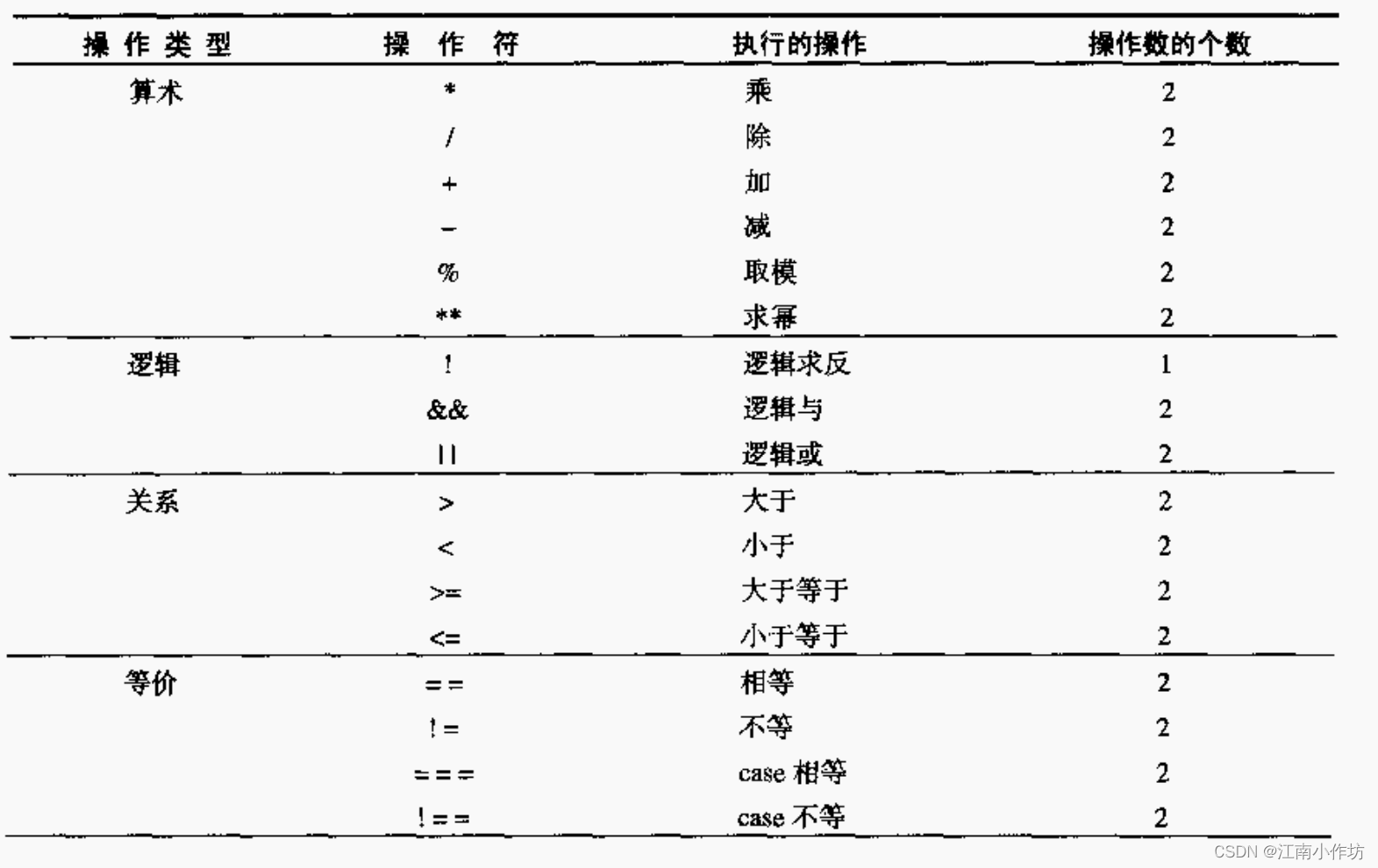

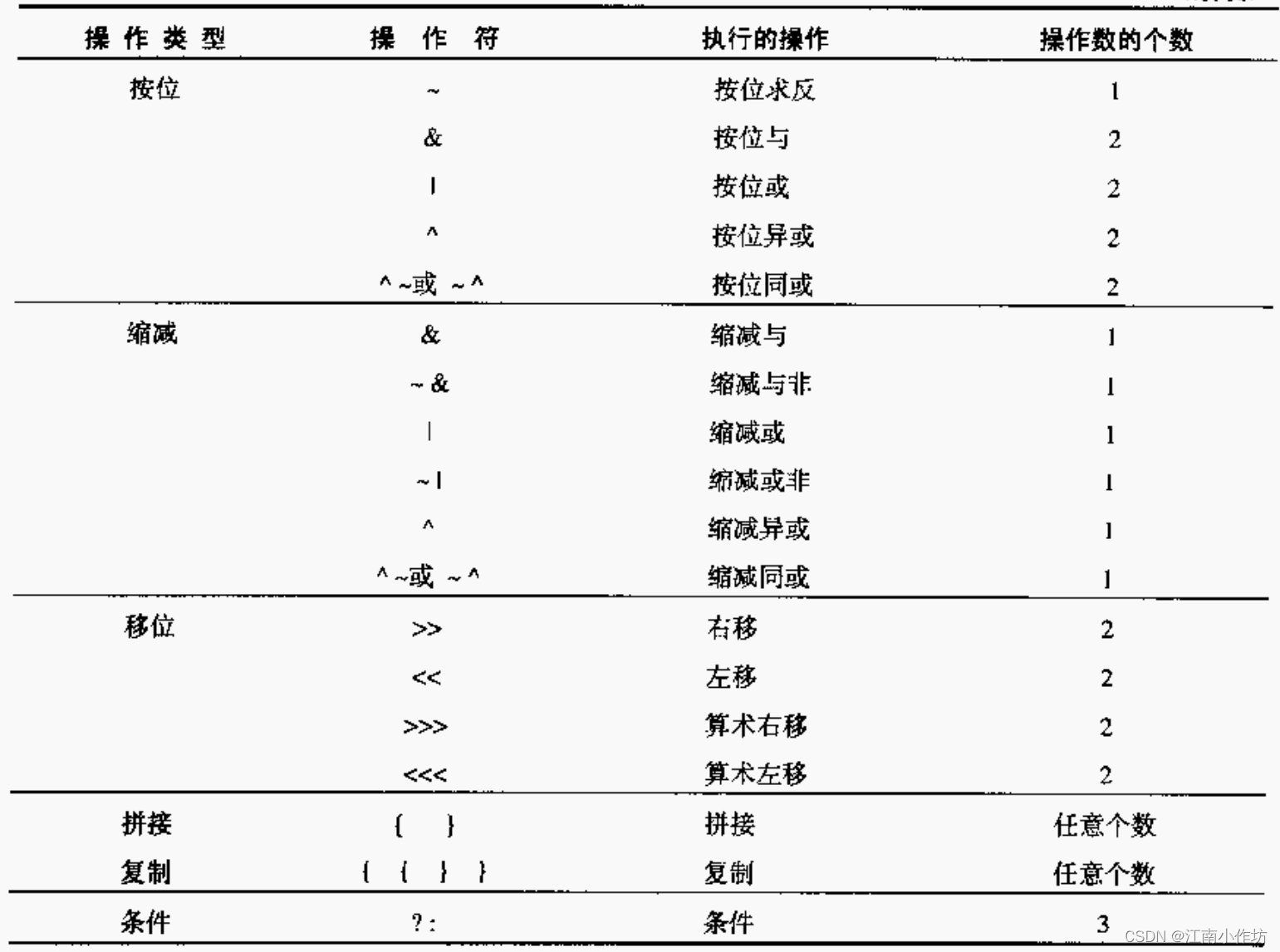

- There are several types of operators : The arithmetic 、 Logic 、 Relationship 、 Equivalent 、 Bitwise 、 cut 、 displacement 、 Splicing and conditional operators .

- Pick a few unfamiliar records

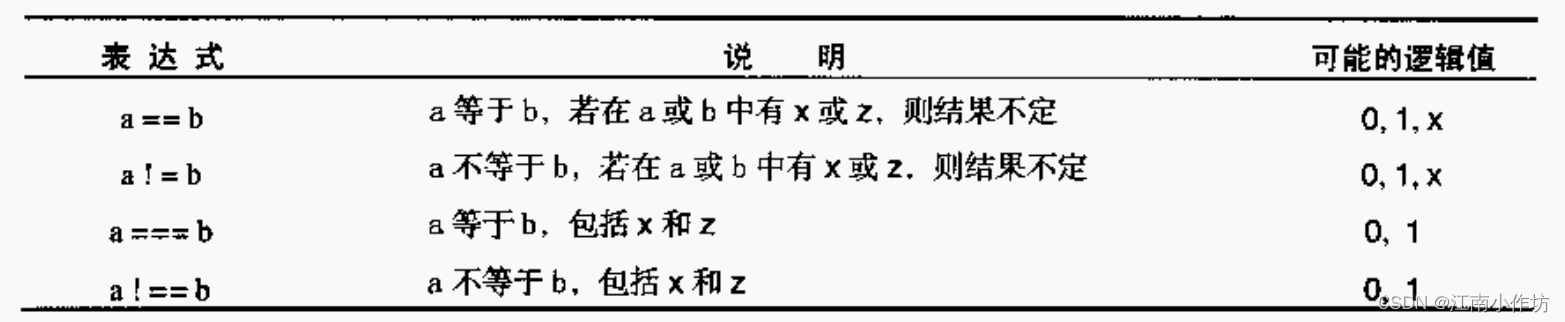

Equivalent operator

- Relevant instructions are shown in the figure

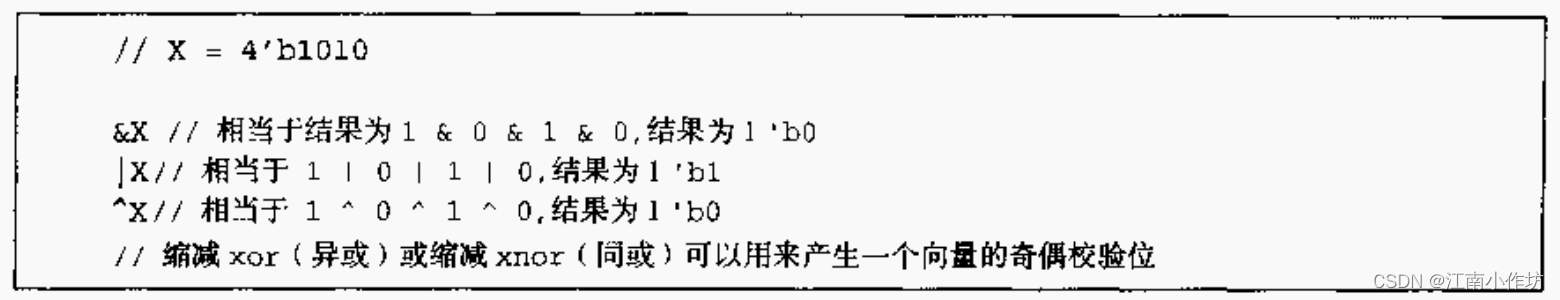

Reduction operator

- There is only one operator , Operate on vector operands bit by bit , Produce one by one results .

Conditional operators

With three operands , usage :

condition_expr ? true_expr : false_expr;namely : Evaluate conditional expressions , If it is true , The calculation

true_expr; For false , Calculationfalse_expr; For uncertainty x, Then both expressions are evaluated , Then the two results are compared bit by bit . If equal , Then the value of this bit in the result is the value of this bit in the operand ; If you don't want to wait , Then the value of this bit in the result is x.Conditional expressions are similar to multiplexers

Be careful :if-else You can replace conditional expressions , But only in block statements , Cannot replace .

priority

- It is recommended to separate the expressions with parentheses .

give an example

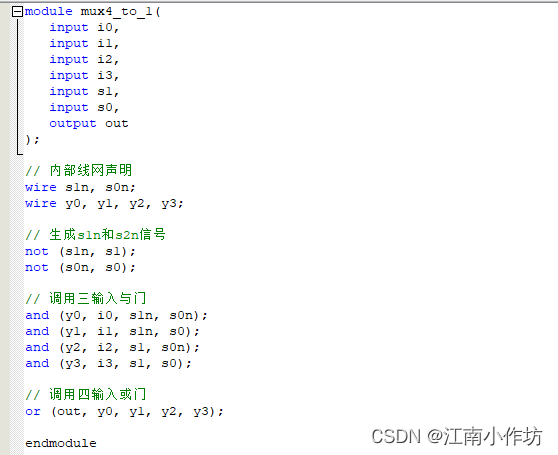

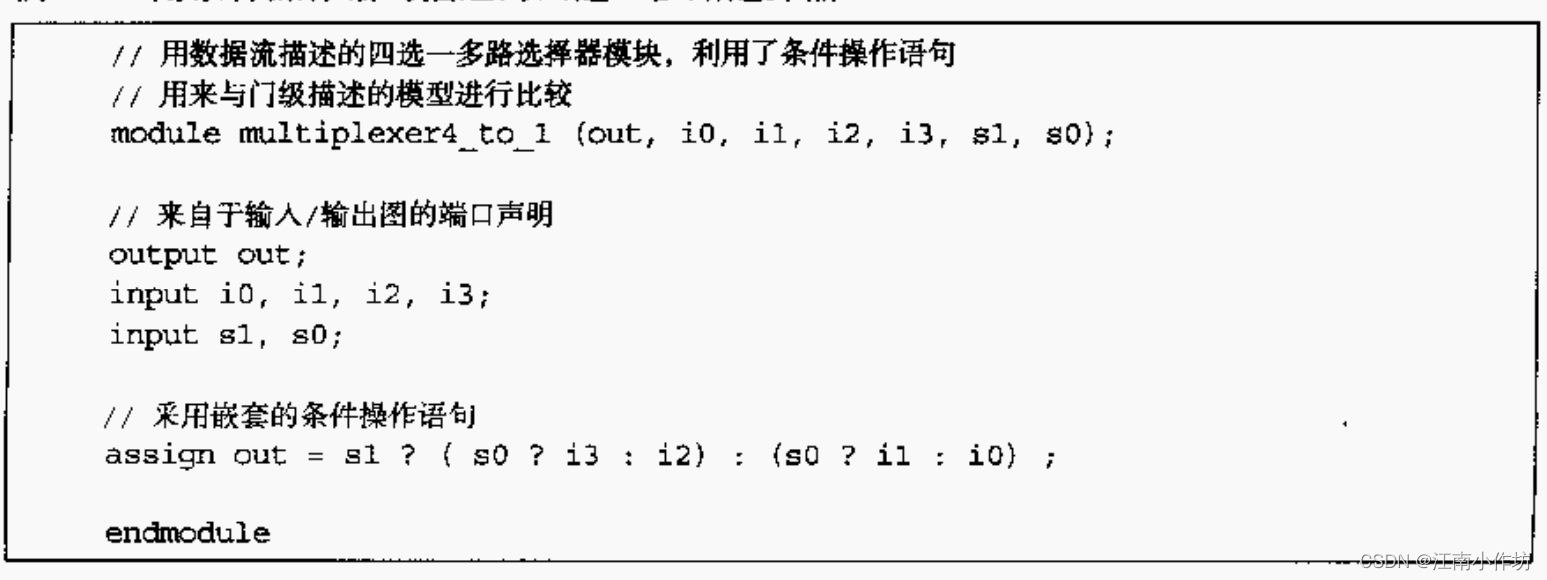

Choose a multi-path selector

- Here's the picture , This is the door level modeling description learned earlier

- Use logical equations to describe

- Use the conditional operator

- so , Modeling with data flow is very simple .

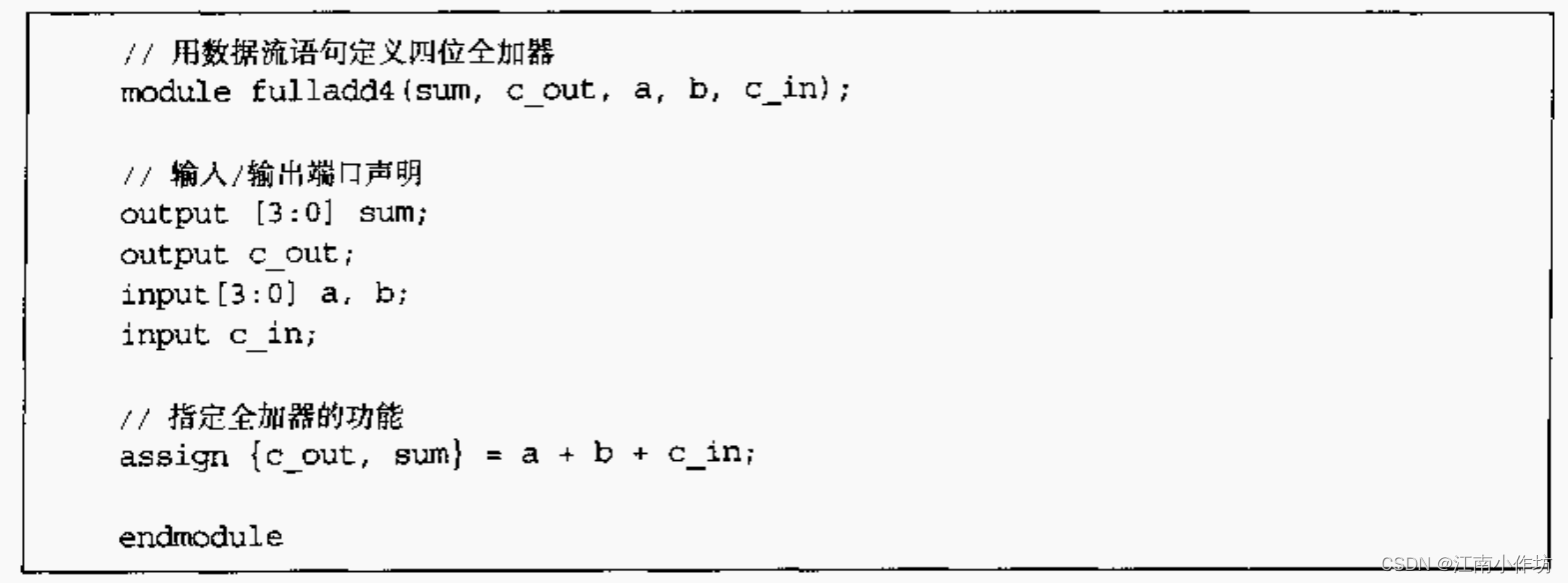

Four position full adder

- Empathy , Use data flow operation statements to describe a four bit full adder

Pulse carry counter

summary

边栏推荐

- 门级建模—课后习题

- Redis 主从同步

- 2022-07-01:某公司年会上,大家要玩一食发奖金游戏,一共有n个员工, 每个员工都有建设积分和捣乱积分, 他们需要排成一队,在队伍最前面的一定是老板

- 云信小课堂 | IM及音视频中常见的认知误区

- 有没有一段代码,让你为人类的智慧所折服

- 股票开户哪个证券公司最好,有安全保障吗

- Huisheng Huiying 2022 intelligent, fast and simple video editing software

- Matplotlib common settings

- 2022-07-01: at the annual meeting of a company, everyone is going to play a game of giving bonuses. There are a total of N employees. Each employee has construction points and trouble points. They nee

- [micro service sentinel] sentinel integrates openfeign

猜你喜欢

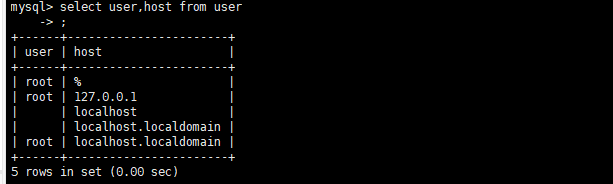

Linux基础 —— CentOS7 离线安装 MySQL

2022年最佳智能家居开源系统:Alexa、Home Assistant、HomeKit生态系统介绍

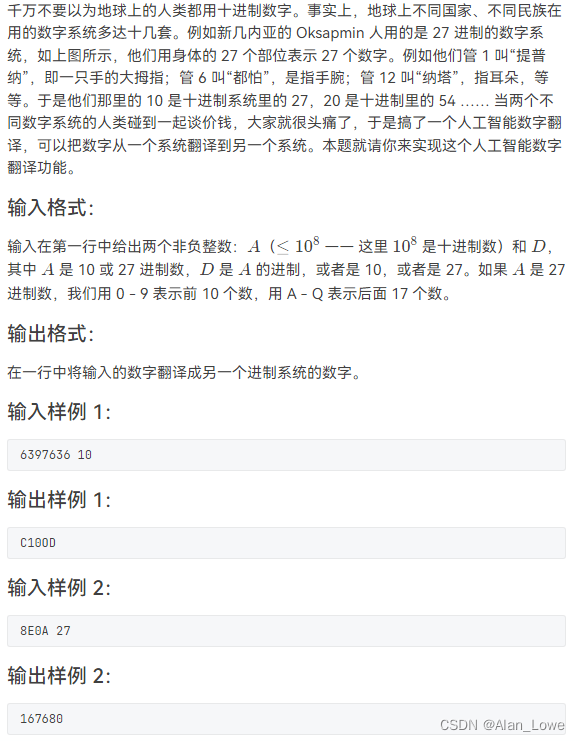

2021 RoboCom 世界机器人开发者大赛-高职组复赛

2022 R1 fast opening pressure vessel operation test questions and answers

Yunxin small class | common cognitive misunderstandings in IM and audio and video

硅谷产品实战学习感触

Future trend and development of neural network Internet of things

Notes on problems - /usr/bin/perl is needed by mysql-server-5.1.73-1 glibc23.x86_ sixty-four

2021 RoboCom 世界机器人开发者大赛-本科组初赛

写给当前及未来博士研究生一些建议整理分享

随机推荐

Practical application and extension of plain framework

Redis数据类型和应用场景

【C#】依赖注入及Autofac

深度学习 | 三个概念:Epoch, Batch, Iteration

Airserver latest win64 bit personal screen projection software

每日三题 6.28

Development trend and future direction of neural network Internet of things

PostgreSQL notes (10) dynamically execute syntax parsing process

内存泄露和内存溢出的区别是什么?

[untitled]

门级建模—课后习题

神经网络物联网的发展趋势和未来方向

Postgresql源码(58)元组拼接heap_form_tuple剖析

Depth first search and breadth first search of graph traversal

2021 RoboCom 世界机器人开发者大赛-本科组初赛

安全协议重点

2022-07-01: at the annual meeting of a company, everyone is going to play a game of giving bonuses. There are a total of N employees. Each employee has construction points and trouble points. They nee

硅谷产品实战学习感触

Daily three questions 6.30

Zero foundation tutorial of Internet of things development