当前位置:网站首页>如何成为一名高级数字 IC 设计工程师(5-3)理论篇:ULP 低功耗设计技术精讲(下)

如何成为一名高级数字 IC 设计工程师(5-3)理论篇:ULP 低功耗设计技术精讲(下)

2022-07-07 06:53:00 【新芯设计】

--总的功耗Ptotal = 静态功耗Pdynamic + 动态功耗Pstatic = 静态漏电 + 翻转功耗 + 短路功耗

----静态功耗 = 静态漏电(Leakage Power)

------主要由 Isub 和 Igate 组成的

------和温度、VGS - VTH 呈正相关

------经验公式:温度每上升 20 摄氏度,静态漏电翻倍

----动态功耗 = 翻转功耗(Switch Power) + 短路功耗(Internal Power)

----翻转/开关功耗

------信号翻转产生的功耗

------Pdyn = (CL)(Vdd^2)(Ptrans)(Fclock)

------负载电容、供电电压、翻转概率(每个时钟通过整个电路的平均转换次数)、时钟频率

------可以通过减少高功耗信号的负载来降低功耗

----短路/内部功耗

------信号在变化过程中,MOS 管同时导通产生的功耗

------Pdyn = (Tsc)(Vdd)(Ipeak)(Fclock)

------短路时间、供电电压、翻转电流、系统时钟

------和信号的转换时间 Transition、翻转概率呈正相关

功耗源主要是浪涌电流、静态功耗和动态功耗,动态功耗又分为短路功耗(内部功耗)和开关功耗(翻转功耗)。

浪涌电流指的是器件上电时产生的最大瞬时输入电流,亦称之为启动电流,通常是正常满载电流的数倍以上。

静态功耗:1、在数字 CMOS 电路中,由晶体管的漏电流引起的功耗;2、待机电流:指的是在关断主电源或者主系统之后,进入待机模式下产生的电流。

由于静态功耗一般与工艺器件有关,不加以讨论&#x

边栏推荐

- Unity shader (basic concept)

- esp8266使用TF卡并读写数据(基于arduino)

- NETCORE 3.1 solves cross domain problems

- 信息安全实验四:Ip包监视程序实现

- Regular matching starts with XXX and ends with XXX

- MySql数据库-索引-学习笔记

- Locust performance test 3 (high concurrency, parameter correlation, assembly point)

- 浏览器中如何让视频倍速播放

- JS judge whether checkbox is selected in the project

- How to speed up video playback in browser

猜你喜欢

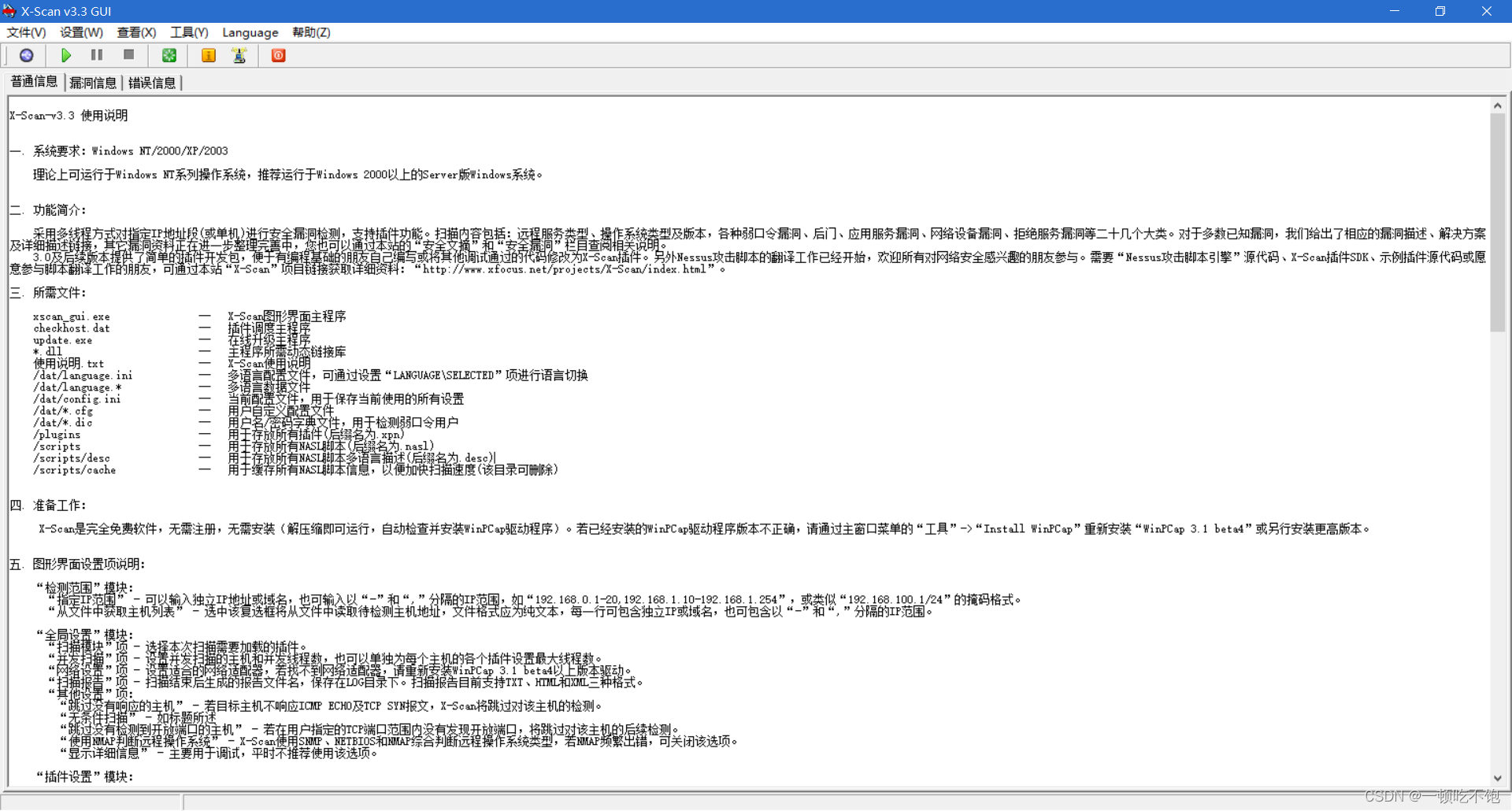

Information Security Experiment 2: using x-scanner scanning tool

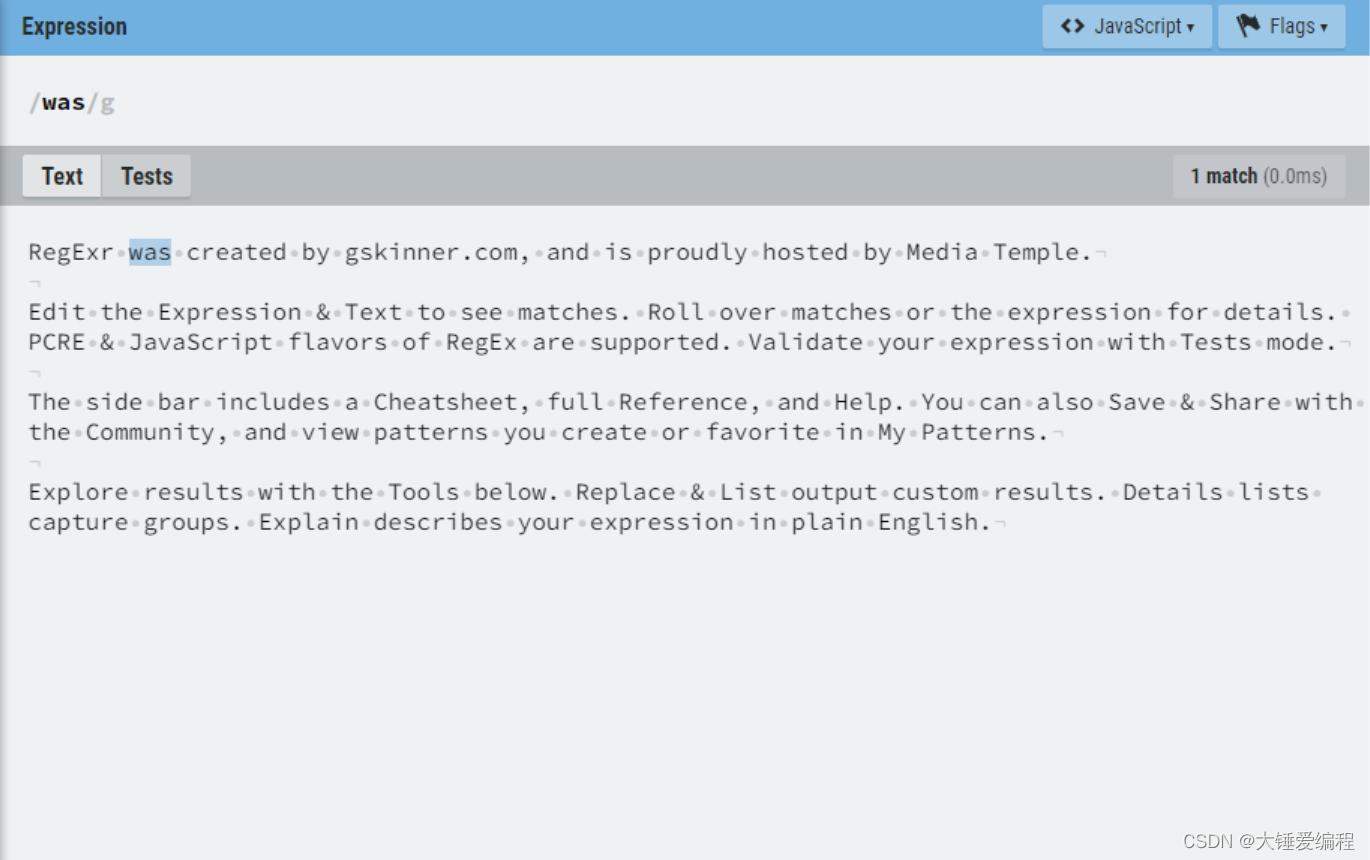

Regular matching starts with XXX and ends with XXX

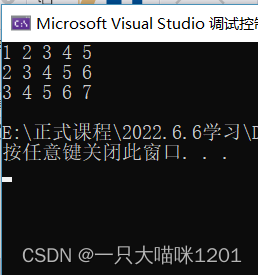

C language pointer (Part 1)

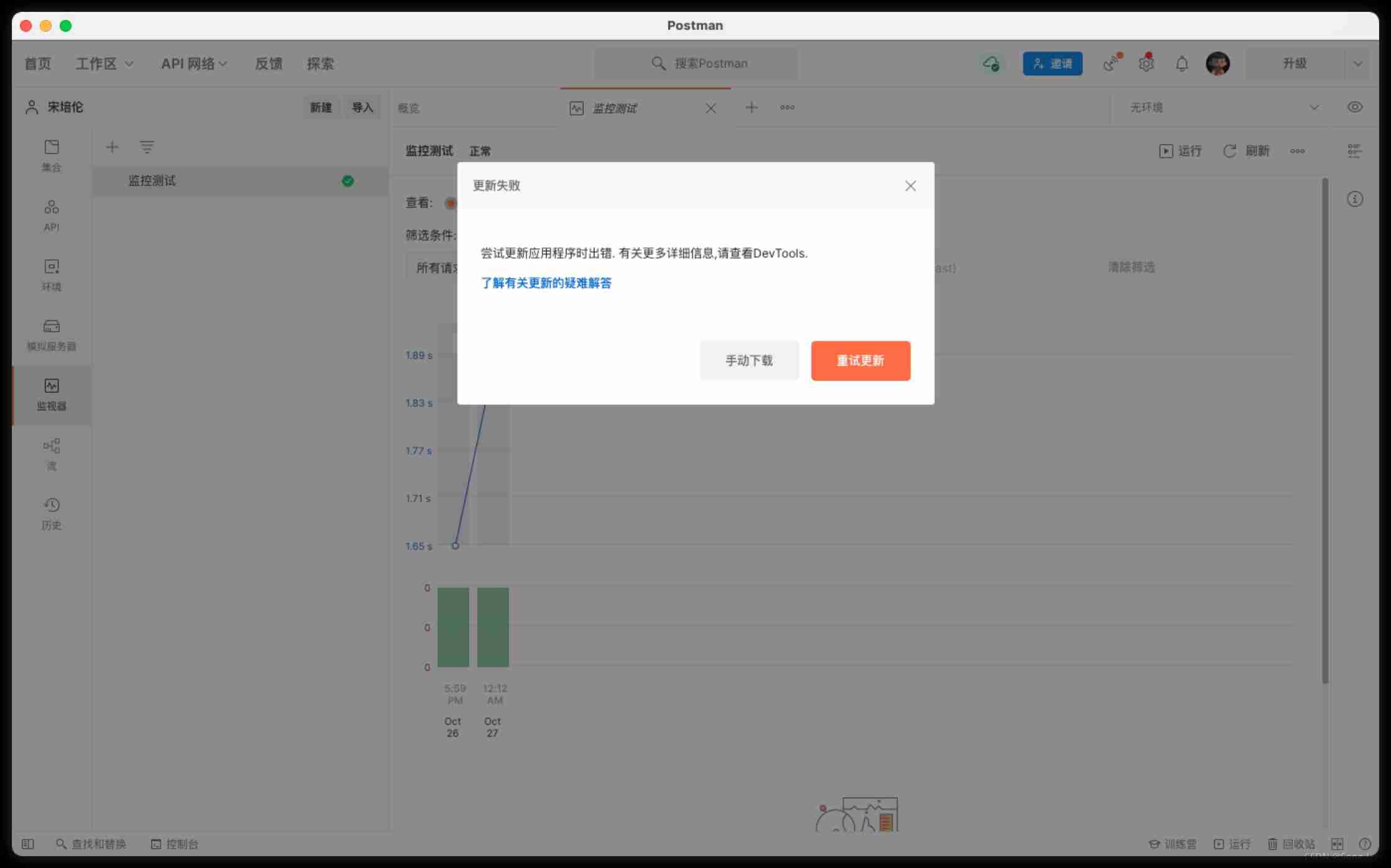

Postman interface test (I. installation and use)

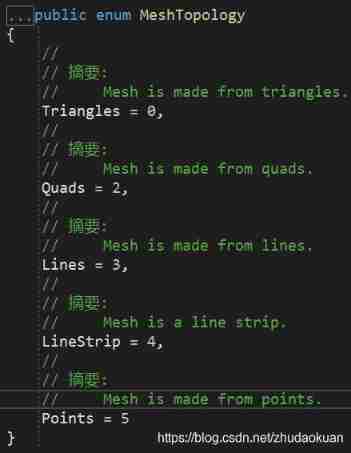

Unity uses mesh to realize real-time point cloud (I)

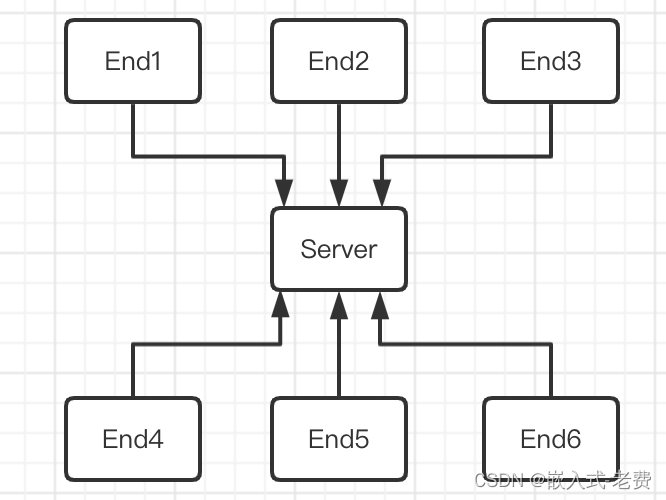

stm32和电机开发(从单机版到网络化)

MySQL common statements

MySql数据库-事务-学习笔记

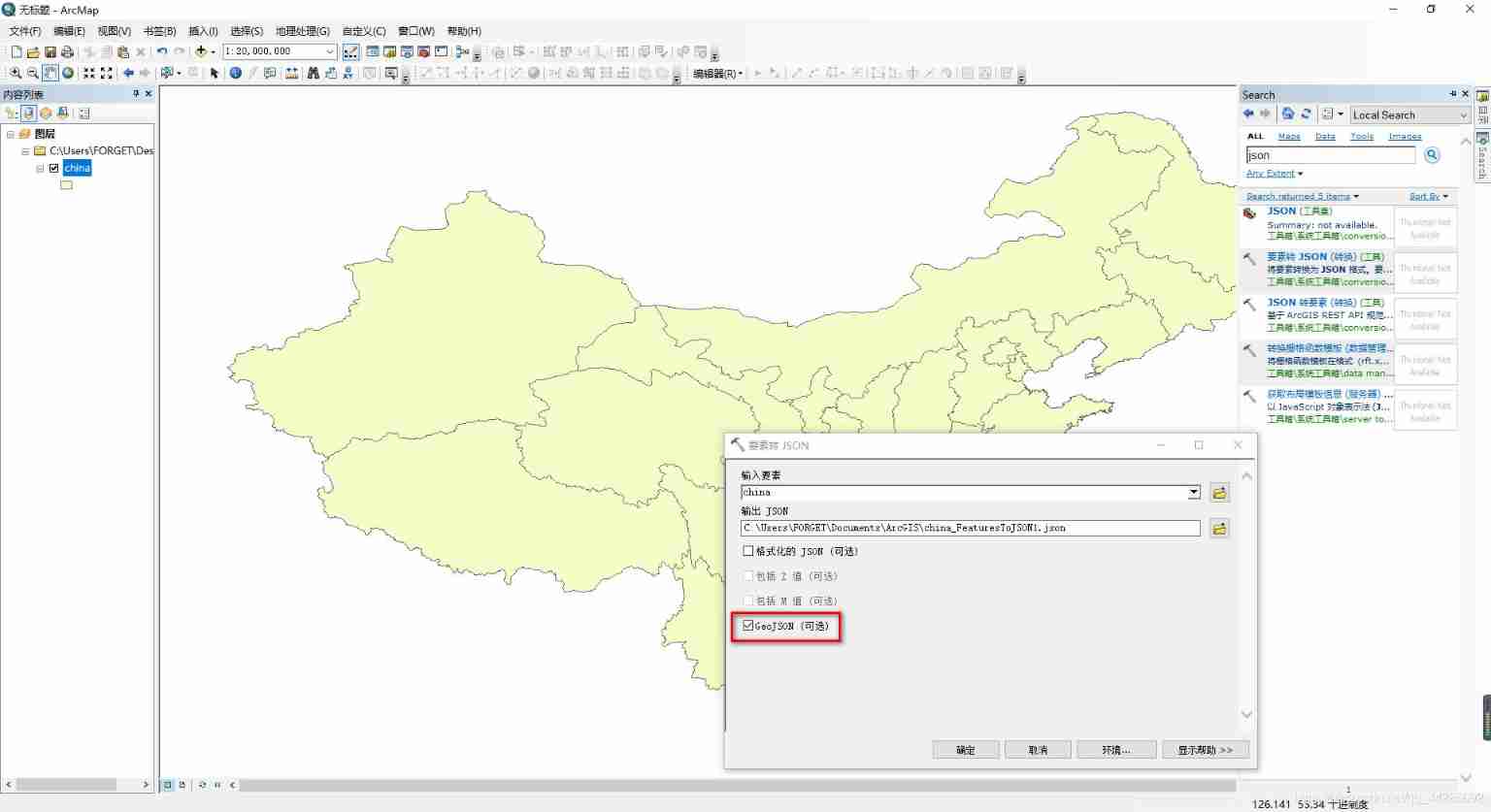

Cesium load vector data

C language pointer (Part 2)

随机推荐

golang select机制和超时问题怎么解决

Error: selenium common. exceptions. WebDriverException: Messag‘geckodriver‘ execute

网易云微信小程序

DRF defines views and routes

sqlplus乱码问题,求解答

Information Security Experiment 2: using x-scanner scanning tool

Oracle installation enhancements error

How to speed up video playback in browser

Dynamics 365Online ApplicationUser创建方式变更

Regular matching starts with XXX and ends with XXX

MySql数据库-事务-学习笔记

JS judge whether checkbox is selected in the project

Jenkins automated email

IIS faked death this morning, various troubleshooting, has been solved

C language pointer (exercises)

IIS redirection redirection appears eurl axd

Implementation of corner badge of Youmeng message push

如何使用clipboard.js库实现复制剪切功能

asp. How to call vb DLL function in net project

Sublime Text4 download the view in bower and set the shortcut key