当前位置:网站首页>SOC serial port configuration

SOC serial port configuration

2022-06-28 07:40:00 【youbin2013】

SOC Serial port configuration

1 UART working principle

SoC A total of 12 On the road UART. this 12 road UART Can be configured as intelligent UART Pattern , Because our driver is transparent data communication , So do not use intelligent mode .12 road UART Can work independently and in parallel , Every way UART There's an independent FIFO, Its size is 4k*8bit, Sending and receiving are respectively 2k*8bit; The communication data format can be configured , The default is a start bit 、 Eight data bits 、 No verification 、 A stop bit ; Communication baud rate can be set by software , The typical baud rate is 38.4Kbps、76.8Kbps、115.2Kbps、614.4Kbps; Maximum baud rate 1Mbps; Have corresponding handshake marks for communication sending and receiving ; Communication receiving error 、 send out FIFO Empty and receive FIFO An interrupt occurs when the threshold is reached , And the interrupt source information can be obtained by querying the internal interrupt flag register through the software ; It can communicate with the universal asynchronous serial communication controller . Its architecture is shown in the figure 1 Shown .

chart 1 UART Architecture

Data is received through the cache first FIFO, Then enter the receiving link , After filtering, it is sent to the controller , Data is sent to the send cache through the send link FIFO, Signal output .

2 The configuration process

Soc Of UART Support non intelligent mode and intelligent mode , We use non intelligent mode , The configuration process is as follows :

- To configure UART Clock enable , Configure peripheral clock enable register (0x40C00000) Of 15-4bit by 0xfff, Can make 12 Serial port clock .

- To configure UART Clock source selection of , Configure peripheral configuration registers (0x40C00004) Of the 4 Position as 1, choice UART The module clock is AHB Module master clock .

- Configure serial port pin multiplexing register IOMUX Of 3-0bit by 0x0, Configure to UART Serial port pin function .

- Reset UART function , towards UART Serial port command register CMD writes 0xff, And delay to wait for the completion of reset .

- To configure UART Baud rate ,, First analysis PLL Setting value of master clock , If it is a bypass clock , Directly calculate the baud rate value through the peripheral clock , If it is a PLL clock , Calculate the baud rate value through the value of the master clock , The baud rate is calculated by :(PERIPHERAL_CLK/(16*BaudRate)) & 0xff;PERIPHERAL_CLK Indicates the serial port peripheral clock , Bypass is 50MHz, Master clock mode the mode of the master clock 1/2.

- To configure UART Non intelligent mode ,1 Stop bits , Even check ,FIFO Pattern , Normal operation mode , And enable the receiving function , Configure the general control register UCR(0bit by 0x0,3-1 by 0x0,8bit by 0x0,9bit by 0,10bit by 1,11bit by 0).

- If interrupt is used , To configure FIFO Threshold register ITL, The scope is 1-2048.

- If interrupt is used , Configure the serial port interrupt enable register IER, To configure 1bit by 1 Enable to trigger interrupt when the threshold is reached .

- If interrupt is used , Read the interrupt flag register in the interrupt service function to clear the interrupt flag .

- If interrupt is used , Configure corresponding interrupt ID(uart0-uart11 by 62-73) The interrupt allocator register corresponding to number and CPU Interrupt interface controller register .

- Design of serial port sending function , Polling for UART The value of the status register , If the serial port sends FIFO When it is full, no data will be written to send FIFO in , If sent FIFO If not, write the data to the sending FIFO in .

- Design of serial port receiving function , Polling for UART The value of the status register , If the serial port receives FIFO If it is not empty, it will receive FIFO All data in the are read out to the user , If you receive FIFO empty , Do not read data to users .

3 Data structure encapsulation

according to UART The distribution of module register addresses in the memory allocation graph , Define its address as an integer macro definition , The register is defined as the structural union of each functional bit field . In this way, the integer address is converted to the structural union pointer of the register , You can write the underlying driver through the register bit field , chart 1 Represents the definition and type conversion of the macro definition register , chart 2 Represents the register structure union definition .

chart 1

chart 2

appendix : Source code

soc_uart.h The header file :

/*

* soc_uart.h

*

* Created on: 2020 year 5 month 25 Japan

* Author: dz

*/

#ifndef COMMON_SOC_UART_H_

#define COMMON_SOC_UART_H_

#include "soc.h"

/*------------------------- Check mode ----------------------------*/

typedef enum

{

even_parity = 0, // Receive and send are even parity check

odd_parity = 1, // Both receive and send are odd parity

txeven_rxodd_parity = 2, // Send even parity , Receive odd parity

txodd_rxeven_parity = 3, // Send odd parity , Receive even parity

txeven_rxnone_parity = 4, // Send even parity , Receive no verification

txodd_rxnone_parity = 5, // Send odd parity , Receive no verification

none_parity = 6, // No verification is generated

} UART_PARITY_TYPE;

/*------------------------- Number of stop bits ----------------------------*/

typedef enum

{

one_stop = 0, //1 Bit stop bit

two_stop = 1, //2 Bit stop bit

} UART_STOP_TYPE;

typedef struct _Uart_Config_Type{

Uint32 BaudRate;

UART_STOP_TYPE stop; // Number of stop bits

UART_PARITY_TYPE parity; // Parity mode

BOOL isLoop; // Whether self loop mode

BOOL isIntelligenceMode; // Whether intelligent working mode

BOOL isEnableReceived; // Is it possible to receive

BOOL isRamMode; // Whether to use RAM Pattern

}Uart_Config_Type;

Uint32 FIND_UART(Uint8 Numb,REG_UART_TYPE** UARTx);

Uint32 UART_GetFlagStatus(Uint8 Numb,UCRUSR_REG *ucr_value);

Uint32 UART_SendData(Uint8 Numb, Uint8* buff, Uint32 length);

Uint32 UART_ReceiveData(Uint8 Numb, Uint8* buff, Uint32* length);

void UART_Init(Uint8 Numb,Uint32 BaudRate,Uint32 parity);

void UART_INT_Enable(Uint8 Numb, Uint32 type);

Uint8 UART_Get_IntStatus(Uint8 Numb);

#endif /* COMMON_SOC_UART_H_ */

soc_uart.c Drive source file :

/*

* soc_uart.c

*

* Created on: 2020 year 5 month 25 Japan

* Author: dz

*/

#include "soc_uart.h"

Uint32 FIND_UART(Uint8 Numb,REG_UART_TYPE** UARTx)

{

if(Numb > 11)

{

return 2;

}

switch(Numb)

{

case 0:

{

*UARTx = REG_UART0;

}break;

case 1:

{

*UARTx = REG_UART1;

}break;

case 2:

{

*UARTx = REG_UART2;

}break;

case 3:

{

*UARTx = REG_UART3;

}break;

case 4:

{

*UARTx = REG_UART4;

}break;

case 5:

{

*UARTx = REG_UART5;

}break;

case 6:

{

*UARTx = REG_UART6;

}break;

case 7:

{

*UARTx = REG_UART7;

}break;

case 8:

{

*UARTx = REG_UART8;

}break;

case 9:

{

*UARTx = REG_UART9;

}break;

case 10:

{

*UARTx = REG_UART10;

}break;

case 11:

{

*UARTx = REG_UART11;

}break;

default:

{

*UARTx = REG_UART0;

}

break;

}

return 0;

}

Uint32 UART_GetFlagStatus(Uint8 Numb,UCRUSR_REG *ucr_value)

{

REG_UART_TYPE* Uart;

Uint32 rel = 0;

rel = FIND_UART(Numb,&Uart);

if(rel == 0)

{

ucr_value->all = Uart->UCR.all;

}

else

{

return rel;

}

return 0;

}

Uint32 UART_SendData(Uint8 Numb, Uint8* buff, Uint32 length)

{

Uint32 i = 0;

Uint32 Flag_Full = 0;

REG_UART_TYPE* Uart;

Uint32 rel = 0;

UCRUSR_REG ucr_reg;

if((length<1)||(length>255))

return 4;

rel = FIND_UART(Numb,&Uart);

if(rel == 0)

{

do

{

UART_GetFlagStatus(Numb,&ucr_reg);

Flag_Full = ucr_reg.bit1.FIFOTF;

if(1 == Flag_Full)

{

return 5;

}

else

{

Uart->FIFO = *(buff+i);

i = i + 1;

}

}while(i < length);

}

else

{

return rel;

}

return 0;

}

Uint32 UART_ReceiveData(Uint8 Numb, Uint8* buff, Uint32* length)

{

Uint32 rel = 0;

REG_UART_TYPE* Uart;

UCRUSR_REG ucr_reg;

Uint32 Length_Tmp = 0;

Uint32 Flag_Empty = 1;

Uint32 Flag_Error = 0;

rel = FIND_UART(Numb,&Uart);

if(rel == 0)

{

do

{

UART_GetFlagStatus(Numb,&ucr_reg);

Flag_Empty = ucr_reg.bit1.FIFORE;

Flag_Error |= ucr_reg.bit1.PE;

if(0 == Flag_Empty)

{

*(buff + Length_Tmp) = Uart->FIFO;

Length_Tmp = Length_Tmp + 1;

}

}while((Length_Tmp < 255) && (0 == Flag_Empty));

*length = Length_Tmp;

if(0 == Length_Tmp)

{

return 6;

}

if(1 == Flag_Error)

{

return 9;

}

}

else

{

return rel;

}

return 0;

}

void delay(int count)

{

while(count--);

}

void UART_Init(Uint8 Numb,Uint32 BaudRate,Uint32 parity)

{

REG_UART_TYPE* Uart;

Uint32 rel = 0;

Uint32 bypass, fbdiv, refdiv, PERIPHERAL_CLK,main_clk_temp;

Uart_Config_Type Uart_Config_Value;

Uart_Config_Value.BaudRate = BaudRate;

Uart_Config_Value.isEnableReceived = true;

Uart_Config_Value.isIntelligenceMode = flase;

Uart_Config_Value.isLoop = flase;

Uart_Config_Value.isRamMode = flase;

if(parity == 2)

{

Uart_Config_Value.parity = even_parity;

}

else if(parity == 3)

{

Uart_Config_Value.parity = odd_parity;

}

else

{

Uart_Config_Value.parity = none_parity;

}

Uart_Config_Value.stop = one_stop;

rel = FIND_UART(Numb,&Uart);

if(rel == 0)

{

//1, choice UART Clock source

BASE_AHB->PeriphConfig.bit.UARTCLKSEL = 0x1;

//2, To configure UART Clock enable

BASE_AHB->PeriphClken.bit.UART = 0xfff;

//3, Configure pin reuse

UART_IOMUX->bit.UART01 = 0X0;

UART_IOMUX->bit.UART23 = 0X0;

UART_IOMUX->bit.UART45 = 0X0;

UART_IOMUX->bit.UART67 = 0X0;

//4, Reset uart

Uart->CMD = 0xff;

delay(0x100);

//5, Configure baud rate

// analysis PLL Master clock register value

bypass = BASE_AHB->PllMain.bit.BYPASS;

fbdiv = BASE_AHB->PllMain.bit.FBDIV;

refdiv = BASE_AHB->PllMain.bit.REFDIV;

if(bypass == 1)

{

PERIPHERAL_CLK = 50000000;

Uart->BRSR = (PERIPHERAL_CLK/(16*(Uart_Config_Value.BaudRate))) & 0xff;

}

else

{

main_clk_temp = (fbdiv/refdiv) *(50000000/2); // Calculate the system master clock

PERIPHERAL_CLK = main_clk_temp/2; //AHB The attached peripheral clock is half of the system master clock

Uart->BRSR = (PERIPHERAL_CLK/(16*(Uart_Config_Value.BaudRate))) & 0xff; // BRSR<=0xff

}

//6, Configure non intelligent mode ,1 Stop bits , Even check ,FIFO Pattern , Normal mode , To enable to receive

Uart->UCR.bit0.MODE = Uart_Config_Value.isIntelligenceMode;

Uart->UCR.bit0.STOPBITS = Uart_Config_Value.stop;

Uart->UCR.bit0.PAR = Uart_Config_Value.parity;

Uart->UCR.bit0.FIFO = Uart_Config_Value.isRamMode;

Uart->UCR.bit0.LOOP = Uart_Config_Value.isLoop;

Uart->UCR.bit0.RXEN = Uart_Config_Value.isEnableReceived;

//7, To configure FIFO threshold

Uart->ITL = 200;

}

else

{

return;

}

}

void UART_INT_Enable(Uint8 Numb, Uint32 type)

{

REG_UART_TYPE* Uart;

Uint32 rel = 0;

rel = FIND_UART(Numb,&Uart);

if(rel == 0)

{

Uart->IER.all = type;

}

else

{

return;

}

}

Uint8 UART_Get_IntStatus(Uint8 Numb)

{

REG_UART_TYPE* Uart;

Uint32 rel = 0;

Uint8 status = 0;

rel = FIND_UART(Numb,&Uart);

if(rel == 0)

{

status = Uart->IFR.bit.RECVC;

}

else

{

return -1;

}

return status;

}

边栏推荐

猜你喜欢

linux下修改mysql用户名root

hack the box:RouterSpace题解

How to configure DDR3 of dm8148

ABAP skill tree

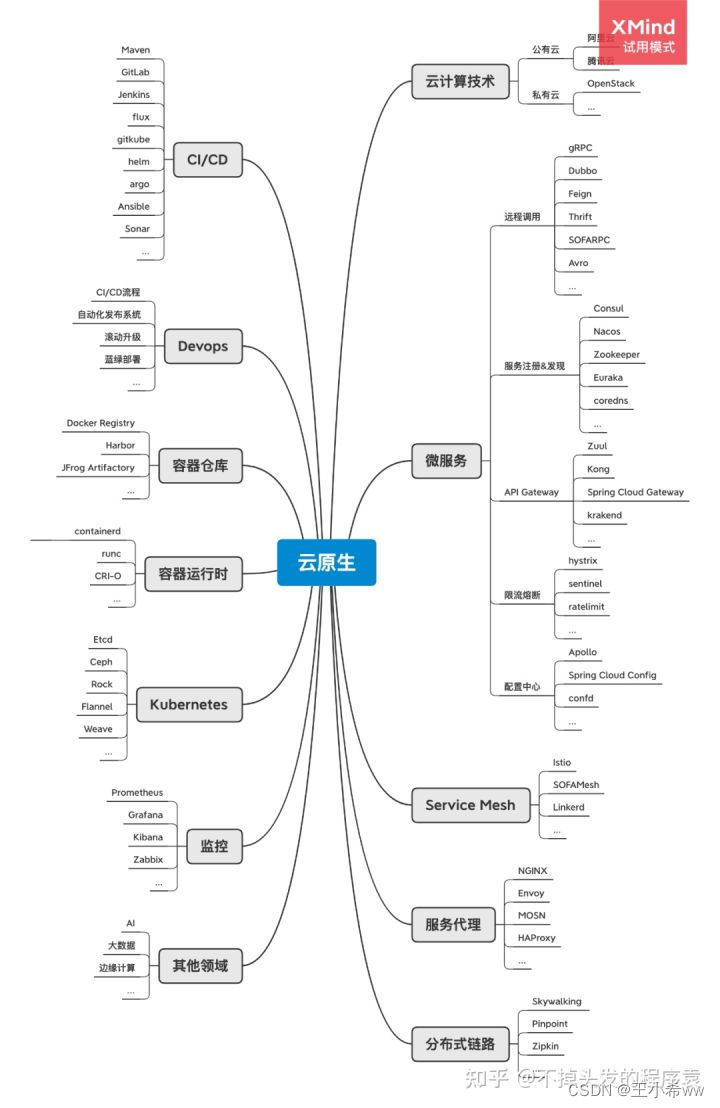

云原生(待更新)

Top 25 most popular articles on vivo Internet technology in 2021

Modifying MySQL user name root under Linux

安全培训是员工最大的福利!2022新员工入职安全培训全员篇

8 张图 | 剖析 Eureka 的首次同步注册表

Alibaba cloud server creates snapshots and rolls back disks

随机推荐

goland IDE和delve调试位于kubernetes集群中的go程序

HJ质数因子

Hj21 simple password

Alibaba cloud server creates snapshots and rolls back disks

大型项目中的Commit Message规范化控制实现

HJ character count

2021 VDC: technological architecture evolution of vivo Internet service for 100 million users | PPT download attached

kubernetes集群命令行工具kubectl

Section Xi. Axi of zynq_ Use of DMA

HJ明明的随机数

什么是EC鼓风机(ec blower fan)?

推荐系统系列精讲(第五讲): 排序模型的调优实践

kubelet垃圾(退出的容器和未使用的镜像)回收源码分析

Drawing animated bubble chart with R language

Investment transaction and settlement of the fund

What should I do if the version is incompatible with the jar package conflict?

Principle and practice of bytecode reference detection

Devtools implementation principle and performance analysis practice

Can okcc call centers work without computers?

Resizing node of rediscluster cluster cluster mode