当前位置:网站首页>【QPSK中频】基于FPGA的QPSK中频信号产生模块verilog设计

【QPSK中频】基于FPGA的QPSK中频信号产生模块verilog设计

2022-06-10 21:48:00 【fpga和matlab】

1.软件版本

matlab2013b+quartusii

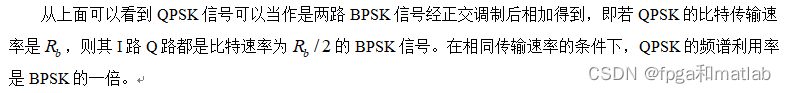

2.本算法理论知识

QPSK信号可以表示为:

![]()

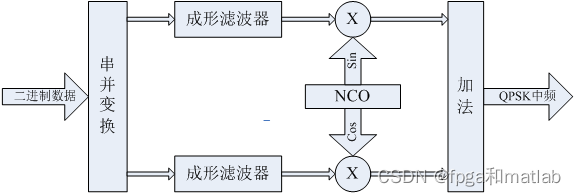

QPSK信号的组成方框图如图1所示。

下面,我们将基于这个结构设计一个QPSK调制信号发送模块。

3.部分源码

`timescale 1ns / 1ps

module tops(

i_clk,

i_rst,

o_signal,

o_I,

o_Q,

o_I_filter,

o_Q_filter,

o_I_cos,

o_Q_sin,

o_R

);

input i_clk;

input i_rst;

output o_signal;

output signed[1:0] o_I;

output signed[1:0] o_Q;

output signed[15:0]o_I_filter;

output signed[15:0]o_Q_filter;

output signed[15:0]o_I_cos;

output signed[15:0]o_Q_sin;

output signed[15:0]o_R;

wire clk4m;

wire clk8m;

DCM DCM_u(

.i_clk (i_clk),

.i_rst (i_rst),

.o_clk_8m1 (clk4m),

.o_clk_8m2 (clk8m)

);

signal signal_u(

.i_clk (clk4m),

.i_rst (i_rst),

.o_dout(o_signal)

);

s2p s2p_u(

.i_clk (clk4m),

.i_clk2 (i_clk),

.i_rst (i_rst),

.i_signal (o_signal),

.o_I (o_I),

.o_Q (o_Q)

);

filter filter_u1(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (o_I),

.o_dout(o_I_filter)

);

filter filter_u2(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (o_Q),

.o_dout(o_Q_filter)

);

wire signed[15:0]fsin;

wire signed[15:0]fcos;

NCO_ip NCO_ip_u(

.phi_inc_i (16'd16384),

.clk (i_clk),

.reset_n (~i_rst),

.clken (1'b1),

.fsin_o (fsin),

.fcos_o (fcos),

.out_valid ()

);

reg signed[31:0]r_I_cos;

reg signed[31:0]r_Q_sin;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

r_I_cos <= 32'd0;

r_Q_sin <= 32'd0;

end

else begin

r_I_cos <= fcos*o_I_filter;

r_Q_sin <= fsin*o_Q_filter;

end

end

assign o_I_cos = r_I_cos[29:14];

assign o_Q_sin = r_Q_sin[29:14];

assign o_R = o_I_cos + o_Q_sin;

endmodule 4.仿真效果

通过设计,整个系统的RTL结构图如下所示:

仿真结果如下所示:

A01-110

边栏推荐

- Several reasons and solutions of virtual machine Ping failure

- vulnhub之dc3

- Auto.js pro 开发环境配置

- vulnhub之dc4

- Opencv_ 100 questions_ Chapter IV (16-20)

- 分布式基础

- Static routing configuration of serial interface in router experiment (Supplement)

- Opencv_ 100 questions_ Chapter II (6-10)

- dc_labs--lab1的学习与总结

- [original] analysis of nine price HPV data capture of Yilu app

猜你喜欢

![[tcapulusdb knowledge base] tcapulusdb shard relocation introduction](/img/7b/8c4f1549054ee8c0184495d9e8e378.png)

[tcapulusdb knowledge base] tcapulusdb shard relocation introduction

Keras deep learning practice (8) -- using data enhancement to improve neural network performance

Blue Bridge Cup_ A fool sends a letter_ recursion

Web3生态去中心化金融平台——Sealem Finance

Vulnhub practice DC-1 target

Sherri Monroe被任命为增材制造商绿色贸易协会的新任执行董事

完美解码PureCodec 20220601

Déploiement et utilisation de base de la carte multi - réseau kubernets

ICML2022 | 从零开始重新审视端到端的语音到文本翻译

简单阻抗匹配电路及公式

随机推荐

Sealem finance builds Web3 decentralized financial platform infrastructure

Sdn/nfv application in cloud data center

Multus CNI deployment and basic use of kubernetes multi network card scheme

Web3 ecological decentralized financial platform sealem Finance

Open source project PM how to design official website

Question bank and simulation test of 2022 tea artist (intermediate) operation certificate examination

vulnhub之dc4

How to run Plink software -- three methods

锁机制

"Draw the bow as strong, use the arrow as long", Manfu technology opens a new track for the data service industry

Swin_ Interpretation of transformer source code

Blue Bridge Cup_ A fool sends a letter_ recursion

简单阻抗匹配电路及公式

Web3技术栈权威指南【2022】

Locking mechanism

Icml2022 | revoir la traduction vocale de bout en bout du texte à partir de zéro

Opencv_ 100 questions_ Chapter IV (16-20)

JS sensitive information leak detection tool

Basic use of mathtype7.x

[applet] vant sliding cell adds the function of clicking other positions to close automatically