当前位置:网站首页>APB2standard_handshake_bridge 设计

APB2standard_handshake_bridge 设计

2022-06-11 19:27:00 【Starry丶】

1. 功能描述

由于SoC的外围设备,例如USART、SPI、I2C等板级慢速通信接口,以及外围存储设备如RAM等,都是通过APB进行总线通信的。

而上述这些设备的常用接口并不是基于APB,所以就需要一个APB到标准握手的桥接器,实现接口转化,例如下图

是的,APB2HANDSHAKE桥是作为APB slave呈现的,由此可以得出桥接器的输入输出

2. 参数描述

| Group | Signal | Direction | Width(bits) | Description |

|---|---|---|---|---|

| APB slave | prstn | input | 1 | 复位信号 |

| pclk | input | 1 | 时钟 | |

| paddr | input | PADDR_WIDTH | 用于访问内部寄存器的地址 | |

| pwrite | input | 1 | 1表示写,0表示读 | |

| psel | input | 1 | 选通 | |

| penable | input | 1 | APB使能 | |

| pwdata | input | PDATA_WIDTH | 写数据 | |

| prdata | input | PDATA_WIDTH | 读出的数据 | |

| pready | output | 1 | 准备标志 | |

| pslverr | output | 1 | 传输错误标志,地址无效时传输也就无效 | |

| Standard Handshake | waddr | output | PADDR_WIDTH | 写地址 |

| wdata | output | PDATA_WIDTH | 写数据 | |

| wr_en | output | 1 | 写使能 | |

| wready | input | 1 | 写准备 | |

| raddr | output | PADDR_WIDTH | 读地址 | |

| rdata | input | PDATA_WIDTH | 读数据 | |

| rdata_val | input | 1 | 读数据有效 | |

| rd_en | output | 1 | 读使能 | |

| rready | input | 1 | 读准备 |

之后是参数描述

| Parameter | Units | Description |

|---|---|---|

| PADDR_WIDTH | bit | 访问SPI内部FIFO的地址位宽 |

| PDATA_WIDTH | bit | 写入or读出的数据位宽 |

| ACCESS_ADDR1、ACCESS_ADDR2、ACCESS_ADDR3、ACCESS_ADDR4 | bit | 可访问地址 |

3. 逻辑设计

按照状态机的思路,可将传输过程按照APB的状态机分为IDLE、SETUP和ACCESS。

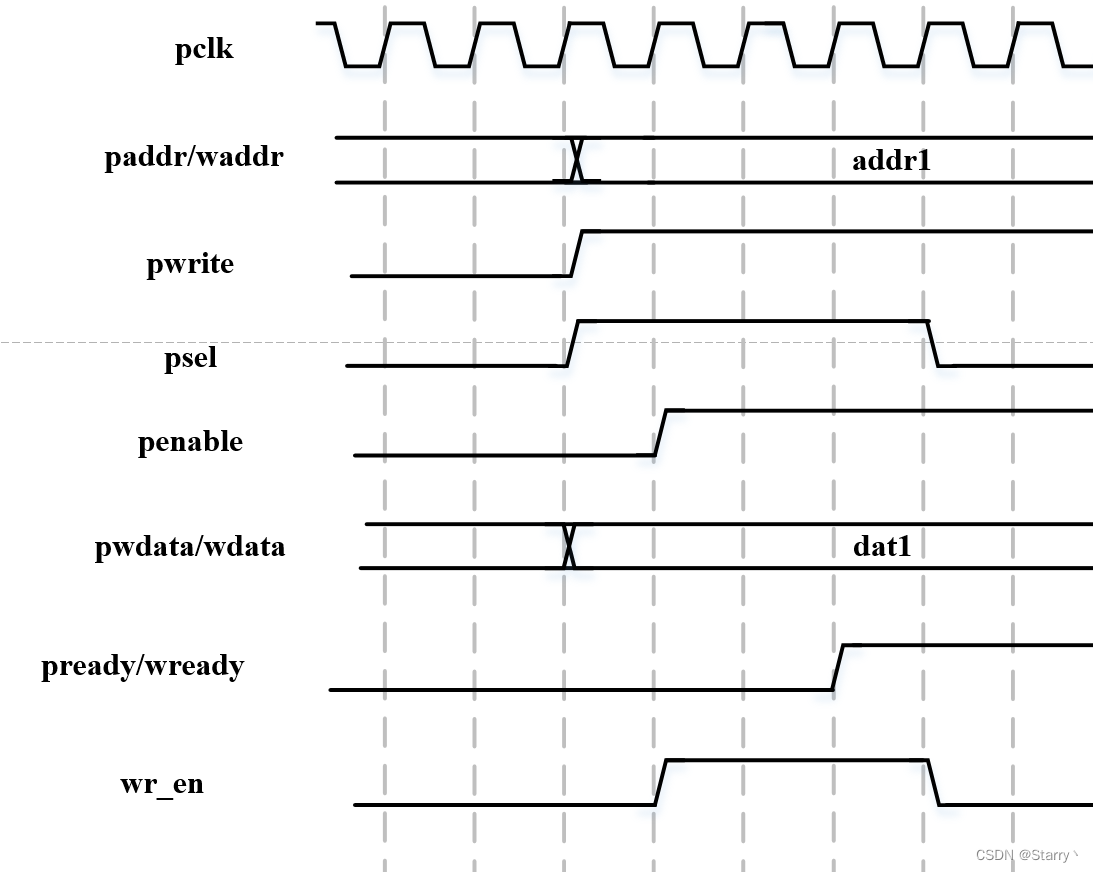

如果是写操作,就比较简单,只需在ACCESS阶段pwdata就是wdata、paddr就是waddr,而pready就是wready,检测到pready && psel && penable 就说明写入完成,如下波形图

读操作有两点需要注意,一个是读出有效数据需要两拍,还有就是读数据时pready表示的是读数据有效而不是读准备。

所以可以通过组合逻辑在APB的SETUP阶段就拉高rd_en 开始读,然后检测rready,一旦发现rready为高就说明rdata将在下一拍读出新数据,并且rdata_val与pready也是组合逻辑等于。

3.1. 代码

在实际写代码的时候,发现rd_en必须通过组合逻辑实现上述波形,所以不需要检测rready为高再拉低这种时序逻辑

module apb2standard_handshake_bridge#(

parameter PADDR_WIDTH = 32,

parameter PDATA_WIDTH = 32

parameter ACCESS_ADDR1 = 32'h0000_0000_0000_0010,

parameter ACCESS_ADDR2 = 32'h0000_0000_0000_0014,

parameter ACCESS_ADDR3 = 32'h0000_0000_0000_0018,

parameter ACCESS_ADDR4 = 32'h0000_0000_0000_001C

)(

input prstn,

input pclk,

input [PADDR_WIDTH-1:0] paddr,

input pwrite,

input psel,

input penable,

input [PDATA_WIDTH-1:0] pwdata,

output [PDATA_WIDTH-1:0] prdata,

output pready,

output pslverr,

output [PADDR_WIDTH-1:0] waddr,

output [PDATA_WIDTH-1:0] wdata,

output wr_en,

input wready,

output [PADDR_WIDTH-1:0] raddr,

input [PDATA_WIDTH-1:0] rdata,

input rdata_val,

output rd_en,

input rready

);

reg wr_en_r;

reg rd_en_r;

[email protected](posedge pclk or negedge prstn) begin

if(!prstn)

wr_en_r <= 1'b0;

else if(pwrite && psel) begin

if(!penable)

wr_en_r <= 1'b1;

else if(!wready)

wr_en_r <= 1'b1;

else

wr_en_r <= 1'b0;

end

else

wr_en_r <= 1'b0;

end

assign wr_en = wr_en_r;

assign waddr = paddr;

assign raddr = paddr;

assign wdata = pwdata;

assign pready = (pwrite)? wready:rdata_val;

assign prdata = rdata;

[email protected](*) begin

if(!pwrite && psel && !rdata_val)

rd_en_r = 1'b1;

else

rd_en_r = 1'b0;

end

assign rd_en = rd_en_r;

assign pslverr = pready && (paddr != ACCESS_ADDR1)

&& (paddr != ACCESS_ADDR2)

&& (paddr != ACCESS_ADDR3)

&& (paddr != ACCESS_ADDR4);

endmodule

边栏推荐

- Undefined reference to 'g2o:: vertexe3:: vertexe3()'

- [Multisim Simulation] using operational amplifier to generate sawtooth wave

- Yolov3 pytoch code and principle analysis (I): runthrough code

- Picture bed: picgo+ Tencent cloud +typera

- 5g communication test manual based on Ti am5728 + artix-7 FPGA development board (dsp+arm)

- 基于飞桨搭建的多模态学习工具包PaddleMM

- SLAM APP

- cf:F. Shifting String【字符串按指定顺序重排 + 分组成环(切割联通分量) + 各组最小相同移动周期 + 最小公倍数】

- 使用贝叶斯优化进行深度神经网络超参数优化

- leetcode:66. add one-tenth

猜你喜欢

cf:G. Count the Trains【sortedset + bisect + 模拟维持严格递减序列】

![Leetcode: sword finger offer 59 - ii Maximum value of queue [deque + sortedlist]](/img/6b/f2e04cd1f3aaa9fe057c292301894a.png)

Leetcode: sword finger offer 59 - ii Maximum value of queue [deque + sortedlist]

![[C language questions -- 10 simple questions for leetcode]](/img/60/c7aca1392eb85c3a7185abe4c82f16.png)

[C language questions -- 10 simple questions for leetcode]

Introduction to go language (VI) -- loop statement

An adaptive chat site - anonymous online chat room PHP source code

干货丨MapReduce的工作流程是怎样的?

![Cf:f. shifting string [string rearrangement in specified order + grouping into rings (cutting connected components) + minimum same moving cycle of each group + minimum common multiple]](/img/54/028f186883e54bcf0d741cf31b94fd.png)

Cf:f. shifting string [string rearrangement in specified order + grouping into rings (cutting connected components) + minimum same moving cycle of each group + minimum common multiple]

556. next larger element iii- (31. next permutation) - two iterations

ASEMI的MOS管25N120在不同应用场景的表现

懂机器学习如何入门量化交易?

随机推荐

Building web applications

An adaptive chat site - anonymous online chat room PHP source code

YOLOv3 Pytorch代码及原理分析(一):跑通代码

cocan yocto buildroot

SISO decoder for SPC (supplementary Chapter 1)

Introduction to typescript

Cf:b. array determinations

【图像分割】基于马尔可夫随机场实现图像分割附matlab代码

Web3 Games: exploring and reshaping the game experience

CMU 15-445 database course lesson 5 text version - buffer pool

Longest strictly increasing subsequence

【求助】请问如何让微信公众号文章在外部浏览器中打开后还能显示下方的精选留言?

PyMySQL利用游标操作数据库方法封装!!!

Learn about random library · 1

无监督图像分类《SCAN:Learning to Classify Images without》代码分析笔记(1):simclr

Web3游戏:游戏体验的探寻与重塑

基于飞桨搭建的多模态学习工具包PaddleMM

What is the workflow of dry goods MapReduce?

《经济学人》:WTO MC12重启 数字经济成为全球经济复苏和增长的核心引擎

程序员10年巨变,一切都变了又好像没变...