当前位置:网站首页>Register address name mapping

Register address name mapping

2022-07-07 09:05:00 【A big cat 1201】

Register address name mapping

describe

stay STM32 There are many functional units in , There are many registers in the bus and various peripherals , Each type of functional unit , Bus , Each peripheral and register has an address , Their address is from STM32 The hardware circuit of , If we use its address every time , This will be too complicated , So we map their addresses to a register address name , In this way, it will be much more convenient to use .

The mapping principle

Take peripherals for example :

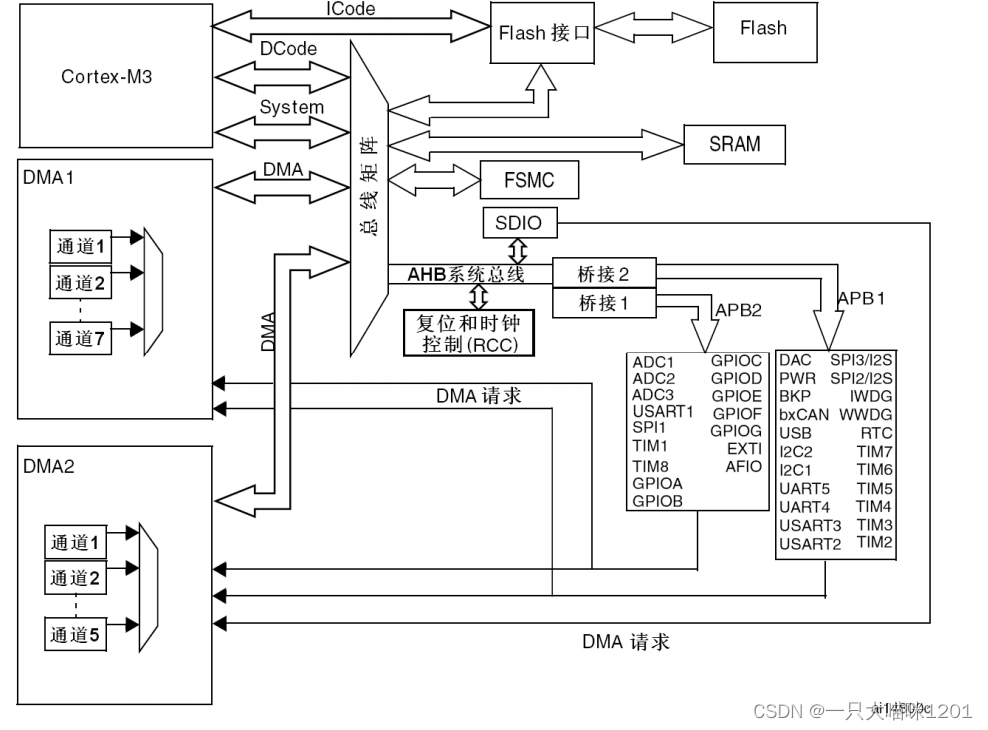

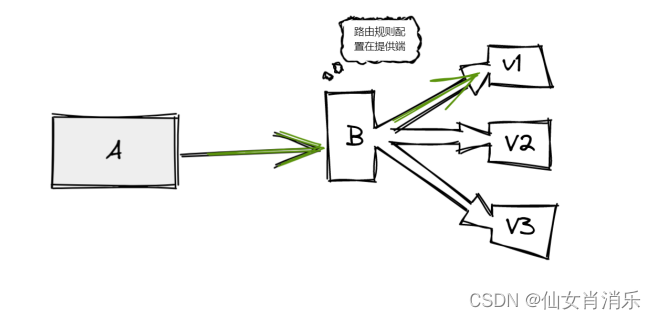

So first of all STM32 Bus structure :

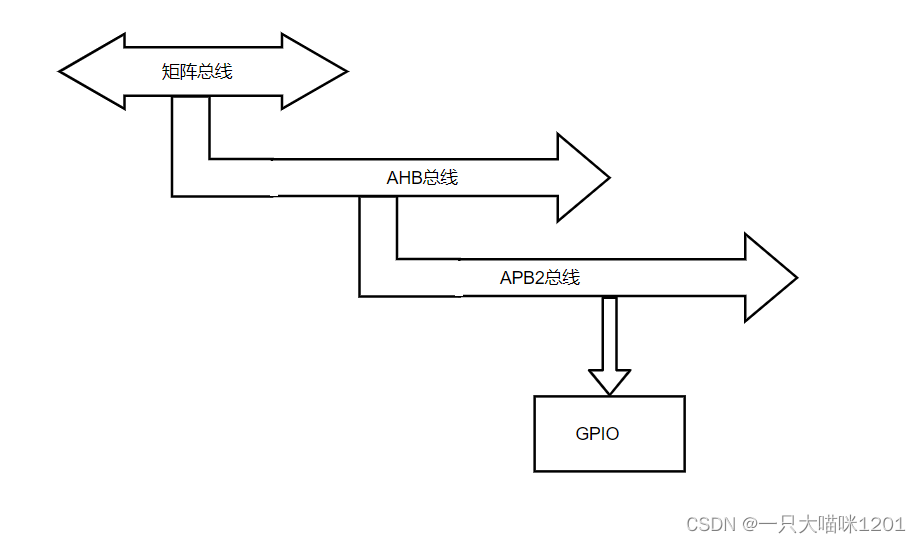

We use GPIO For example , Let's find its location .

- The first thing we find is the matrix bus . This is a STM32 The lifeline of , Various peripherals and various functional units and CPU Almost all connections need to be through the matrix bus .

- Further down we found AHB Bus . It is attached to the matrix bus , Of course ,AHB There are also many peripherals on the bus .

- Further down we found APB2 Bus . There are some high-speed peripherals attached to this bus .

- Finally we found GPIO.GPIO All attached to APB2 On the bus .

Graphically ,GPIO The position of is like this .

stay STM Standard library functions provided on the official website , All peripherals have been mapped , Next, Ben meow will introduce to you .

- Peripheral base address :

#define PERIPH_BASE ((uint32_t)0x40000000)

PERIPH_BASE Represents the peripheral base address , All kinds of peripherals are finally obtained by adding some offsets to the base address , Its essence is address 0x40000000.

- Bus peripheral base address

#define APB2PERIPH_BASE (PERIPH_BASE + 0x10000)

APB2PERIPH_BASE representative APB2 Bus peripheral base address , Its essence is a new address obtained by adding an offset to the peripheral base address , such as APB2 The address of is 0x4000000000+0x10000=0x4000010000.

- Register group base address

#define GPIOA_BASE (APB2PERIPH_BASE + 0x0800)

#define GPIOB_BASE (APB2PERIPH_BASE + 0x0C00)

#define GPIOC_BASE (APB2PERIPH_BASE + 0x1000)

#define GPIOD_BASE (APB2PERIPH_BASE + 0x1400)

#define GPIOE_BASE (APB2PERIPH_BASE + 0x1800)

#define GPIOF_BASE (APB2PERIPH_BASE + 0x1C00)

#define GPIOG_BASE (APB2PERIPH_BASE + 0x2000)

Here is just a list of 7 Group GPIO Mapping , The same is true for the mapping of other peripherals .GPIO_XBASE On behalf of the group GPIO The base address , Its essence is APB2 The address obtained by adding an offset to the base address of the bus peripheral .

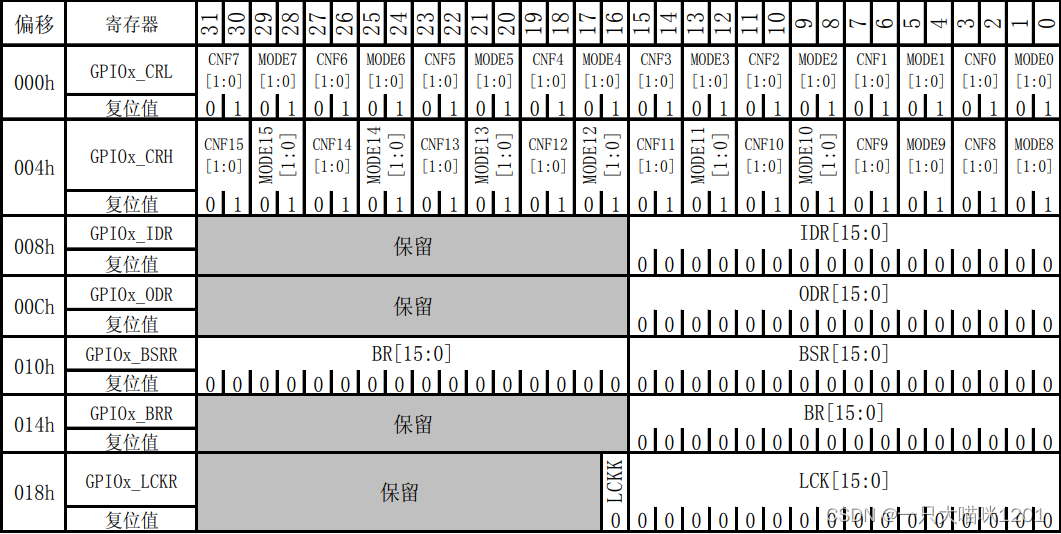

- GPIO Address of each register in

Find out through the manual GPIO Offset value of each register in , Add to GPIO The base address is the specific address of each register .

If you look it up like this , Each time you use it, you need to make corresponding calculations , For ease of use , The register group is processed as follows :

With GPIOA For example :

typedef struct

{

__IO uint32_t CRL;

__IO uint32_t CRH;

__IO uint32_t IDR;

__IO uint32_t ODR;

__IO uint32_t BSRR;

__IO uint32_t BRR;

__IO uint32_t LCKR;

} GPIO_TypeDef;

Put each group GPIO Medium 7 Registers are created into a structure .

#define GPIOA ((GPIO_TypeDef *) GPIOA_BASE)

And then GPIOA The base address of the mandatory type is converted to a structure pointer variable , In this way, it is used GPIOA You only need to directly access the members in the structure when each register of .

For example, using GPIOA_CRL register :

GPIOA->CRL=0x00000000;

Not every time GPIOA Add an offset value to the base address , This makes it much more convenient .

The same is true for other registers in the register group .

Other units

#define FLASH_BASE ((uint32_t)0x08000000)

#define SRAM_BASE ((uint32_t)0x20000000)

#define SRAM_BB_BASE ((uint32_t)0x22000000)

#define PERIPH_BB_BASE ((uint32_t)0x42000000)

#define FSMC_R_BASE ((uint32_t)0xA0000000)

This is the base address of other functional units , for example FLASH,SRAM wait .

#define APB1PERIPH_BASE PERIPH_BASE

#define AHBPERIPH_BASE (PERIPH_BASE + 0x20000)

This is the base address of other bus peripherals ,APB1PERIPH_BASE,AHBPERIPH_BASE Represent the APB1 Base address of peripheral bus ,AHB Base address of peripheral bus .

#define TIM2_BASE (APB1PERIPH_BASE + 0x0000)

#define TIM3_BASE (APB1PERIPH_BASE + 0x0400)

#define TIM4_BASE (APB1PERIPH_BASE + 0x0800)

#define TIM5_BASE (APB1PERIPH_BASE + 0x0C00)

#define TIM6_BASE (APB1PERIPH_BASE + 0x1000)

#define TIM7_BASE (APB1PERIPH_BASE + 0x1400)

#define TIM12_BASE (APB1PERIPH_BASE + 0x1800)

#define TIM13_BASE (APB1PERIPH_BASE + 0x1C00)

#define TIM14_BASE (APB1PERIPH_BASE + 0x2000)

#define RTC_BASE (APB1PERIPH_BASE + 0x2800)

#define WWDG_BASE (APB1PERIPH_BASE + 0x2C00)

#define IWDG_BASE (APB1PERIPH_BASE + 0x3000)

#define SPI2_BASE (APB1PERIPH_BASE + 0x3800)

#define SPI3_BASE (APB1PERIPH_BASE + 0x3C00)

#define USART2_BASE (APB1PERIPH_BASE + 0x4400)

#define USART3_BASE (APB1PERIPH_BASE + 0x4800)

#define UART4_BASE (APB1PERIPH_BASE + 0x4C00)

#define UART5_BASE (APB1PERIPH_BASE + 0x5000)

This is the base address of other register groups , Just a part of it , There's a lot that hasn't been listed , But they are all such mapping methods .

summary

The mapping of register address names is to make it more convenient to use various registers , The essence of each register name is actually an address , The operation register name is more convenient and intuitive than the operation address .

If the above is helpful to you , Please give Ben meow one button three consecutive support .

边栏推荐

- 2021 year end summary

- 使用Typora编辑markdown上传CSDN时图片大小调整麻烦问题

- Mountaineering team (DFS)

- channel. Detailed explanation of queuedeclare parameters

- NVIC中断优先级管理

- Redis fault handling "can't save in background: fork: cannot allocate memory“

- E-commerce campaign Guide

- 模拟卷Leetcode【普通】1705. 吃苹果的最大数目

- 数字三角形模型 AcWing 1027. 方格取数

- Oracle makes it clear at one time that a field with multiple separators will be split into multiple rows, and then multiple rows and columns. Multiple separators will be split into multiple rows, and

猜你喜欢

Ppt template and material download website (pure dry goods, recommended Collection)

2022-07-06 Unity核心9——3D动画

Greenplum 6.x build_ Environment configuration

The essence of high availability

C语言指针(特别篇)

Oracle makes it clear at one time that a field with multiple separators will be split into multiple rows, and then multiple rows and columns. Multiple separators will be split into multiple rows, and

PMP certificate preparation experience sharing

The longest ascending subsequence model acwing 1017 Strange thief Kidd's glider

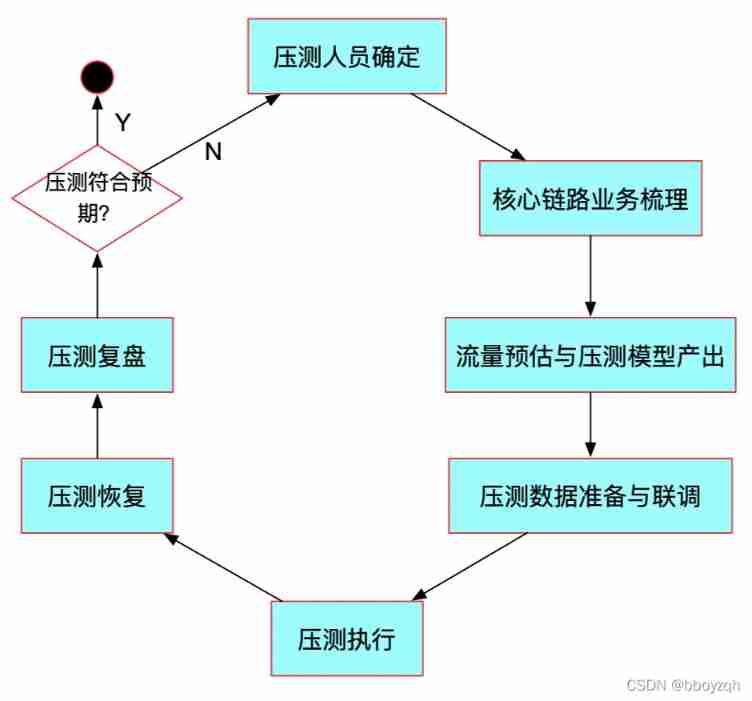

Full link voltage test of the e-commerce campaign Guide

【Istio Network CRD VirtualService、Envoyfilter】

随机推荐

Digital triangle model acwing 1027 Grid access

PMP Exam Preparation experience, seek common ground while reserving differences, and successfully pass the exam

How can I apply for a PMP certificate?

数据在内存中的存储

【ChaosBlade:节点磁盘填充、杀节点上指定进程、挂起节点上指定进程】

Cmake command line use

Interpretation of MySQL optimization principle

RuntimeError: Calculated padded input size per channel: (1 x 1). Kernel size: (5 x 5). Kernel size c

JVM 内存结构 详细学习笔记(一)

Original collection of hardware bear (updated on June 2022)

Greenplum 6.x common statements

Greenplum 6.x monitoring software setup

硬核分享:硬件工程师常用工具包

go mod module declares its path as: gtihub. com/xxx-xx but was required as:xx-xx

OpenGL三维图形绘制

Goldbach conjecture C language

外部中断实现按键实验

寄存器地址名映射

Skills that testers must know: Selenium's three waiting ways are interpreted clearly

2020 year end summary