当前位置:网站首页>JS generate random numbers

JS generate random numbers

2022-07-02 03:24:00 【onYang】

const getNum = (andNum, Num) => {

//andNum Sum of random numbers ,Num Number of random numbers

var randomNum = new Array()

let sum = 0

for (var i=0;i<Num-1;i++)

{

x = Math.floor(Math.random() * (andNum - sum))

randomNum[i] = x

sum += x

}

randomNum[Num-1] = andNum - sum

return randomNum

}

getNum(50,6)边栏推荐

- KL divergence is a valuable article

- MSI announced that its motherboard products will cancel all paper accessories

- [JS reverse series] analysis of a customs publicity platform

- Global and Chinese markets for infant care equipment, 2022-2028: Research Report on technology, participants, trends, market size and share

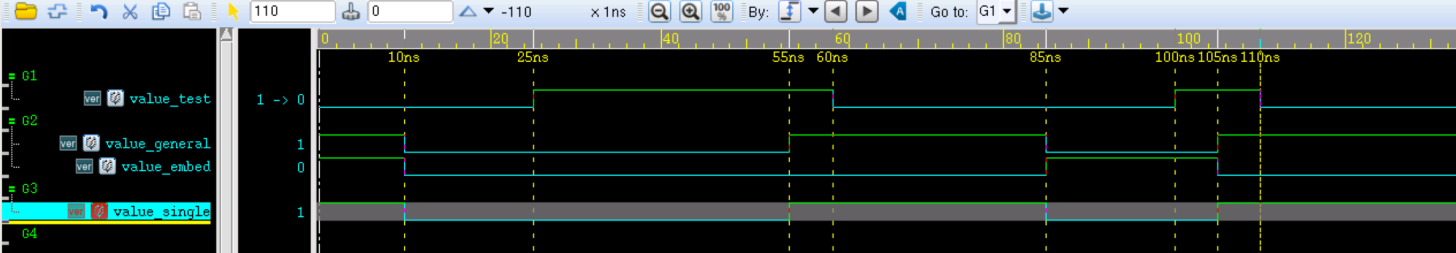

- Verilog 时序控制

- Verilog parallel block implementation

- JS introduction < 1 >

- verilog 并行块实现

- venn图取交集

- IPhone 6 plus is listed in Apple's "retro products" list

猜你喜欢

MySQL connection query and subquery

![[golang] leetcode intermediate bracket generation & Full Permutation](/img/93/ca38d97c721ccba2505052ef917788.jpg)

[golang] leetcode intermediate bracket generation & Full Permutation

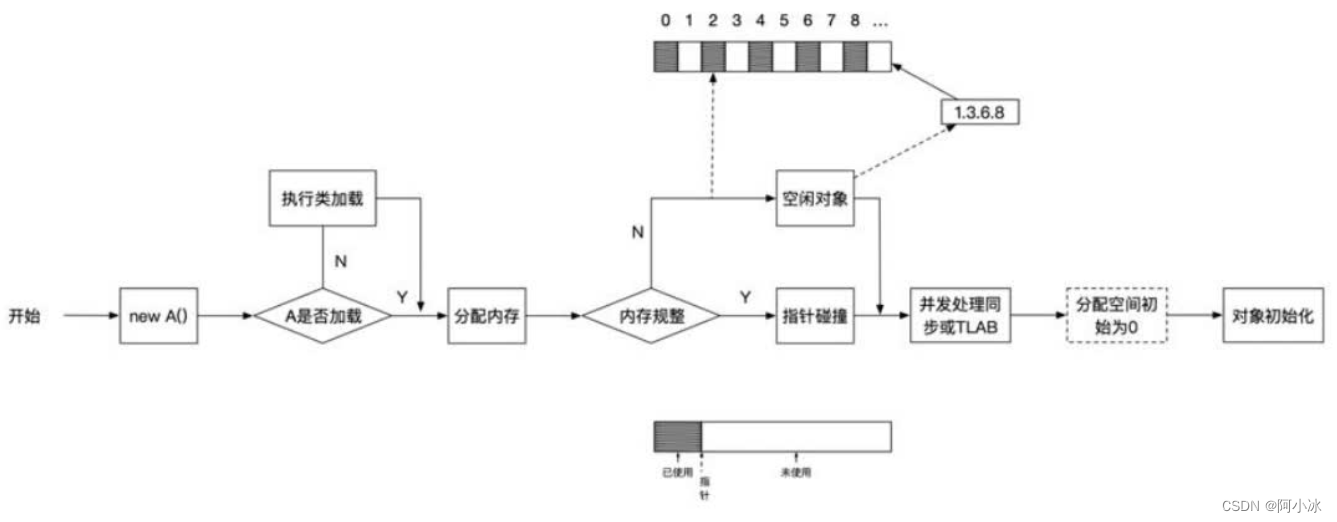

【JVM】创建对象的流程详解

Discussion on related configuration of thread pool

小米青年工程师,本来只是去打个酱油

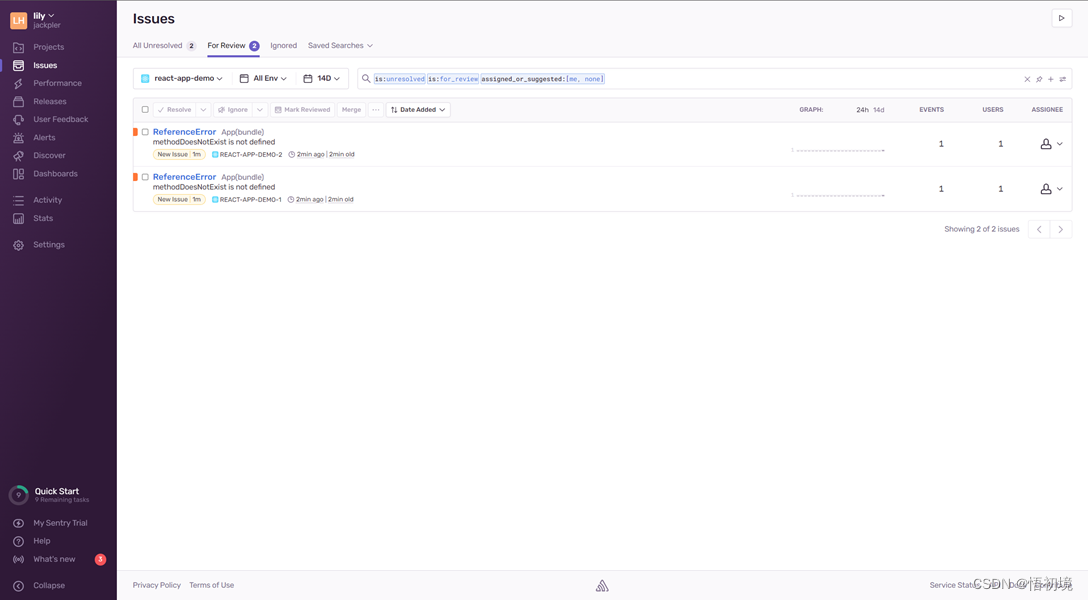

初出茅庐市值1亿美金的监控产品Sentry体验与架构

Start a business

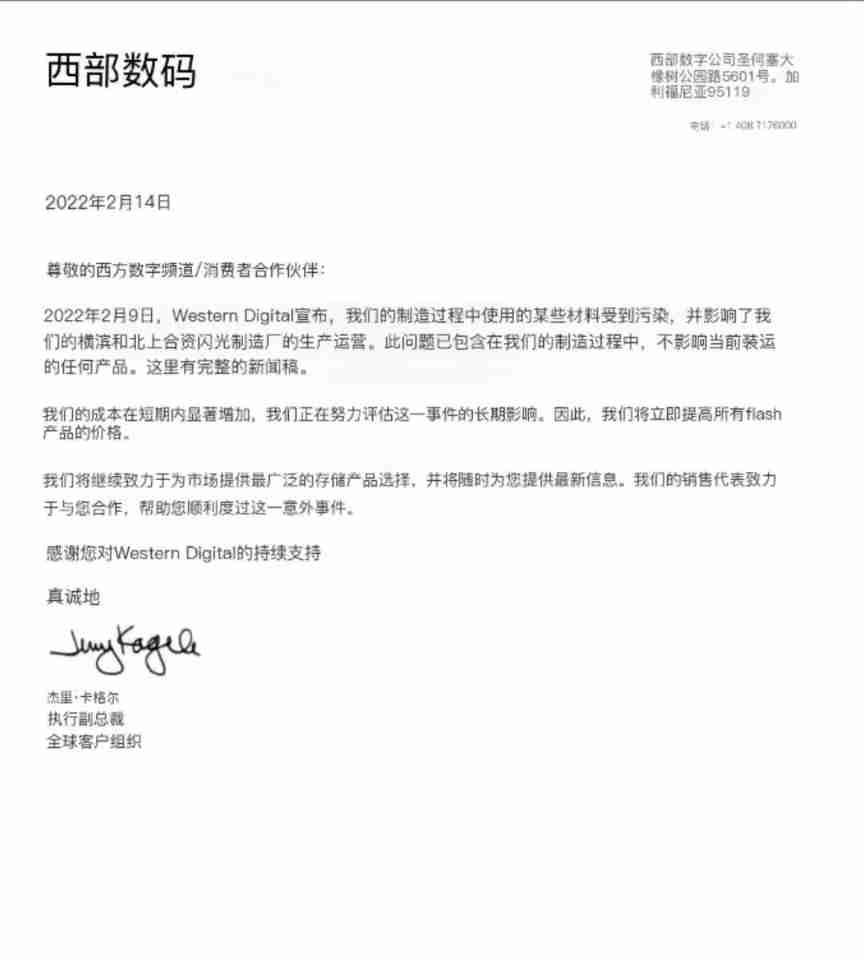

West digital decided to raise the price of flash memory products immediately after the factory was polluted by materials

![Find duplicates [Abstract binary / fast and slow pointer / binary enumeration]](/img/9b/3c001c3b86ca3f8622daa7f7687cdb.png)

Find duplicates [Abstract binary / fast and slow pointer / binary enumeration]

Verilog 时序控制

随机推荐

Review materials of project management PMP high frequency examination sites (8-1)

JDBC details

How to establish its own NFT market platform in 2022

流线线使用阻塞还是非阻塞

Grpc quick practice

[C Advanced] brother Peng takes you to play with strings and memory functions

C # joint Halcon's experience of breaking away from Halcon environment and various error reporting solutions

Verilog 避免 Latch

This article describes the step-by-step process of starting the NFT platform project

ThreadLocal详解

Learn PWN from CTF wiki - ret2shellcode

verilog REG 寄存器、向量、整数、实数、时间寄存器

Load different fonts in QML

KL divergence is a valuable article

[JS reverse series] analysis of a customs publicity platform

Docker installs canal and MySQL for simple testing and implementation of redis and MySQL cache consistency

Calculation of page table size of level 2, level 3 and level 4 in protection mode (4k=4*2^10)

Xiaomi, a young engineer, was just going to make soy sauce

[HCIA continuous update] working principle of OSPF Protocol

Global and Chinese market of autotransfusion bags 2022-2028: Research Report on technology, participants, trends, market size and share