当前位置:网站首页>Verilog reg register, vector, integer, real, time register

Verilog reg register, vector, integer, real, time register

2022-07-02 03:08:00 【Da Xi】

register (reg)

register (reg) Used to represent a storage unit , It will keep the original value of the data , Until it is rewritten . Examples of statements are as follows :

example

reg clk_temp;

reg flag1, flag2 ;

For example, in always In block , Registers may be integrated into edge triggers , In combinatorial logic, it may be integrated into wire Type variable . The register does not require a drive source , You don't need a clock signal . In simulation , The value of the register can be rewritten by assignment at any time . for example :

example

reg rstn ;

initial begin

rstn = 1'b0 ;

#100 ;

rstn = 1'b1 ;

end

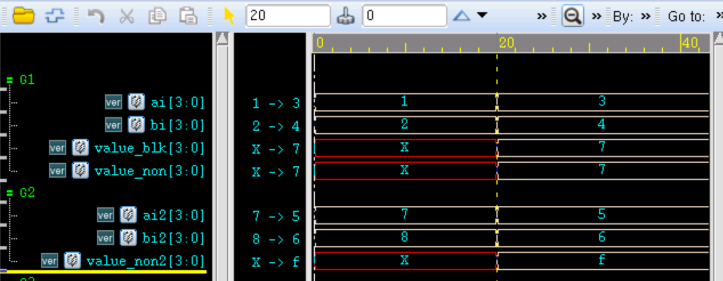

vector

When the bit width is greater than 1 when ,wire or reg Can be declared as a vector . for example :

example

reg [3:0] counter ; // Statement 4bit Bit wide register counter

wire [32-1:0] gpio_data; // Statement 32bit Bit width linetype variable gpio_data

wire [8:2] addr ; // Statement 7bit Bit width linetype variable addr, The bit width range is 8:2

reg [0:31] data ; // Statement 32bit Bit wide register variable data, The most significant bit is 0

For the above vector , We can specify one or several adjacent bits , Used as other logic . for example :

example

wire [9:0] data_low = data[0:9] ;

addr_temp[3:2] = addr[8:7] + 1'b1 ;

Verilog Support variable vector field selection , for example :

example

reg [31:0] data1 ;

reg [7:0] byte1 [3:0];

integer j ;

[email protected]* begin

for (j=0; j<=3;j=j+1) begin

byte1[j] = data1[(j+1)*8-1 : j*8];

// hold data1[7:0]…data1[31:24] Assign values to byte1[0][7:0]…byte[3][7:0]

end

end

Verillog It also supports specifying bit Vector field selection access with fixed bit width after bit .

- [bit+: width] : From start bit Bits begin to increment , The seat width is width.

- [bit-: width] : From start bit Bits begin to decrease , The seat width is width.

example

// below 2 Each assignment is equivalent

A = data1[31-: 8] ;

A = data1[31:24] ;

// below 2 Each assignment is equivalent

B = data1[0+ : 8] ;

B = data1[0:7] ;

When recombining signals into new vectors , You need braces . for example :

example

wire [31:0] temp1, temp2 ;

assign temp1 = {byte1[0][7:0], data1[31:8]}; // Data splicing

assign temp2 = {32{1'b0}}; // assignment 32 The number of bits 0

Integers , The set of real Numbers , Time register variables

Integers , The set of real Numbers , Data types such as time actually belong to register types .

Integers (integer)

Integer types use keywords integer To declare . Do not specify the bit width when declaring , The bit width is related to the compiler , It's usually 32 bit.reg Type variable is an unsigned number , and integer Type variable is a signed number . for example :

example

reg [31:0] data1 ;

reg [3:0] byte1 [7:0]; // An array variable , Follow up

integer j ; // Integer variables , Used to assist in the generation of digital circuits

[email protected]* begin

for (j=0; j<=3;j=j+1) begin

byte1[j] = data1[(j+1)*8-1 : j*8];

// hold data1[7:0]…data1[31:24] Assign values to byte1[0][7:0]…byte[3][7:0]

end

end

In this case ,integer The signal j As an auxiliary signal , take data1 The data of is assigned to the array in turn byte1. After synthesis, there is no in the actual circuit j This signal ,j It only helps to generate the corresponding hardware circuit .

The set of real Numbers (real)

Keywords for real numbers real To declare , Can be expressed in decimal or scientific notation . A real number declaration cannot have a range , The default value is 0. If you assign a real number to an integer , Only the integer part of the real number is assigned to the integer . for example :

example

real data1 ;

integer temp ;

initial begin

data1 = 2e3 ;

data1 = 3.75 ;

end

initial begin

temp = data1 ; //temp The size of the value is 3

end

Time (time)

Verilog Use a special time register time Type variable , Save the simulation time . Its width is generally 64 bit, By calling system functions $time Get the current simulation time . for example :

example

time current_time ;

initial begin

#100 ;

current_time = $time ; //current_time The size is 100

end

边栏推荐

- 表单自定义校验规则

- Framing in data transmission

- What is hybrid web containers for SAP ui5

- spark调优

- Principle of computer composition - interview questions for postgraduate entrance examination (review outline, key points and reference)

- Qualcomm platform WiFi -- P2P issue (2)

- Pychart creates new projects & loads faster & fonts larger & changes appearance

- What are the characteristics of common web proxy IP

- Analysis of FLV packaging format

- SAP ui5 beginner tutorial 19 - SAP ui5 data types and complex data binding

猜你喜欢

2022-2028 global wood vacuum coating machine industry research and trend analysis report

结婚后

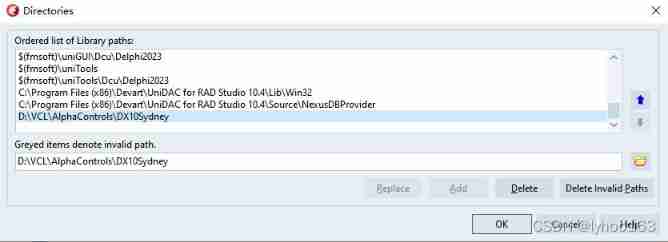

Delphi xe10.4 installing alphacontrols15.12

Mongodb base de données non relationnelle

Verilog avoid latch

连通块模板及变式(共4题)

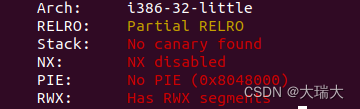

跟着CTF-wiki学pwn——ret2shellcode

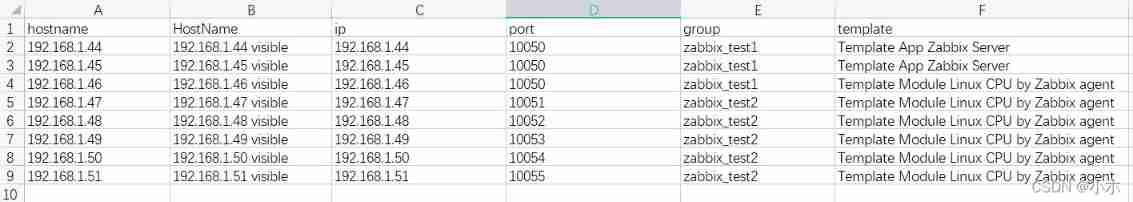

ZABBIX API creates hosts in batches according to the host information in Excel files

2022-2028 global human internal visualization system industry research and trend analysis report

Verilog 过程赋值 区别 详解

随机推荐

MMSegmentation系列之训练与推理自己的数据集(三)

What is the principle of bone conduction earphones and who is suitable for bone conduction earphones

C shallow copy and deep copy

Verilog 过程赋值 区别 详解

Qualcomm platform wifi-- WPA_ supplicant issue

[staff] restore mark (Introduction to the use of restore mark | example analysis of Metaphone mark and restore mark)

Which kind of sports headphones is easier to use? The most recommended sports headphones

venn圖取交集

Intersection vengraph

Baohong industry | 6 financial management models at different stages of life

Leetcode question brushing (10) - sequential question brushing 46 to 50

GSE104154_scRNA-seq_fibrotic MC_bleomycin/normalized AM3

tarjan2

设置状态栏颜色

el-table的render-header用法

GB/T-2423. XX environmental test documents, including the latest documents

[staff] pitch representation (treble clef | C3 60 ~ B3 71 pitch representation | C4 72 pitch representation | C5 84 pitch representation)

2022-2028 global aluminum beverage can coating industry research and trend analysis report

West digital decided to raise the price of flash memory products immediately after the factory was polluted by materials

QT implementation interface jump