当前位置:网站首页>[quickstart to Digital IC Validation] 15. Basic syntax for SystemVerilog Learning 2 (operator, type conversion, loop, Task / Function... Including practical exercises)

[quickstart to Digital IC Validation] 15. Basic syntax for SystemVerilog Learning 2 (operator, type conversion, loop, Task / Function... Including practical exercises)

2022-07-07 08:00:00 【Lugant TCC】

Guide de lecture:L'auteur a eu le privilège d'être à l'avant - garde du domaine de l'information électronique en Chine“University of Electronic Science and Technology”Pendant les études supérieures,En contact avec le FrontNombreICValidation des connaissances,J'ai entendu des choses commeHuawei haisi、Tsinghua Purple light、Mediated Science and TechnologyCours en personne pour les principales entreprises de l'industrie liées aux circuits intégrés,Pour les chiffresICVérifier qu'il y a une certaine accumulation de connaissances et d'expériences d'apprentissage.Pour vous aider à démarrer le Front EndICAmis validés,Après avoir réfléchi un, deux,En particulier cette colonne,Dans l'espoir de prendre le plus de temps possible,Prenez le moins de virages possible,Le plus apprisICValidation des connaissances techniques.

Catalogue des articles

- Un.、Aperçu du contenu

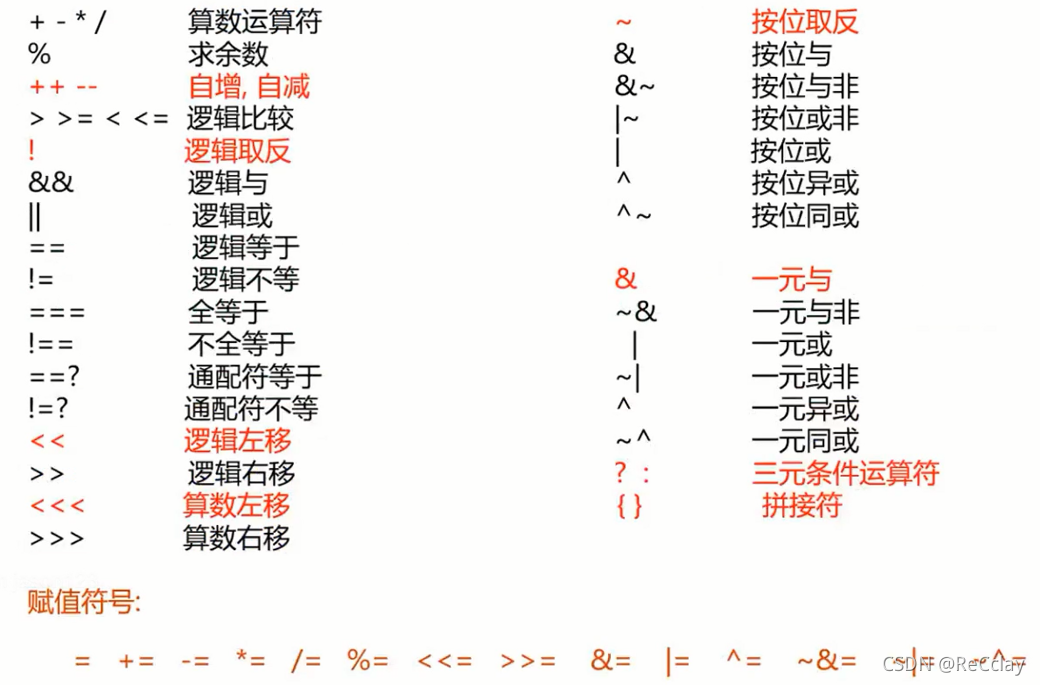

- 2.、Opérateur(Operation)

- Trois、SystemVerilog Déclaration de procédure(Procedural Statements)

- Quatre、Conversion de type variable(Type Casting)

- Cinq、SystemVerilog Instruction de contrôle de la boucle

- Six、SystemVerilog Mission(task)Et fonctions(function)

- Sept、Exercices pratiques

Un.、Aperçu du contenu

- SystemVerilog Opérateur

- SystemVerilog Déclaration de procédure

- SystemVerilog Conversion de type variable

- SystemVerilog Instruction de contrôle de la boucle

- SystemVerilog AméliorationcaseDéclarations

- SystemVerilog Mission(task)Et fonctions(function)

2.、Opérateur(Operation)

- Tout est égal à

===On va comparerx/z

Trois、SystemVerilog Déclaration de procédure(Procedural Statements)

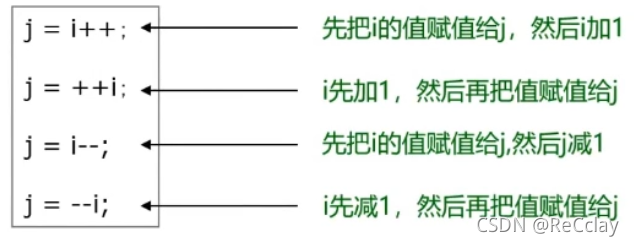

3.1、Opérateurs auto - incrémentaux et auto - décroissants

- SimilaireCLangues

- Ajouter d'abord/ Moins après utilisation et plus après utilisation /Moins

Note::SystemVerilog L'auto - augmentation et l'auto - diminution sont généralement utilisées dans TB- Oui., Ça ne marchera pas. RTLDans le Code!

3.2、Opérateur de comparaison logique

égal à

==,Pas égal à!=(Plus utilisé,En général, il y axIl y a un problème avec l'état )- La logique est vraiment 1, La fausse logique est 0;

- Si parmi les valeurs comparées ExistexEtz, Alors la valeur logique est 1’bx

- eg:

a=4'b000xEtb=4'b000xLes deux résultats de la comparaison sont1'bx, Il y a un trou ici siif(a == b),Attention!1'bxC'est faux !

- eg:

Tout le monde.

===,Pas tout à fait!==- Exactement. Quatre valeurs d'état :

0,1,x,z- eg:

a=4'b000xEtb=4'b000xLes deux résultats de la comparaison sont1'b1

- eg:

- Exactement. Quatre valeurs d'état :

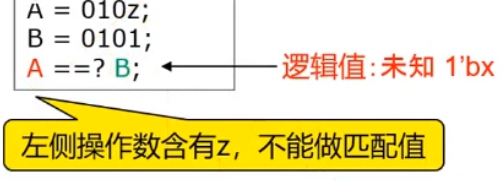

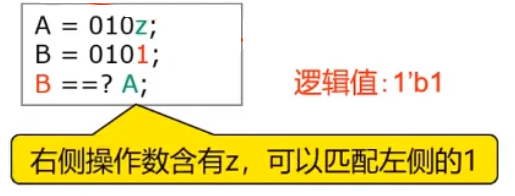

Comparaison logique des caractères génériques

- Correspondance, etc.

==?Et la correspondance n'est pas égale!=?- Comparaison bitwise,Prends ça.

xEtzLes valeurs correspondent - Juste mettre Opérande de droite Dans

xEtzComme symbole de blindage- eg:

4‘b1010 ==? 4'b101xCorrespondance, etc. retour à1'b1;4‘b1011 ==? 4'b101xCorrespondance, etc. retour à1'b1

- eg:

- Comparaison bitwise,Prends ça.

- Correspondance, etc.

- Exemple de comparaison logique des correspondances

- Imprimez le premier

$display

Note:: Notes et

displayIl y a un léger problème de grammaire .

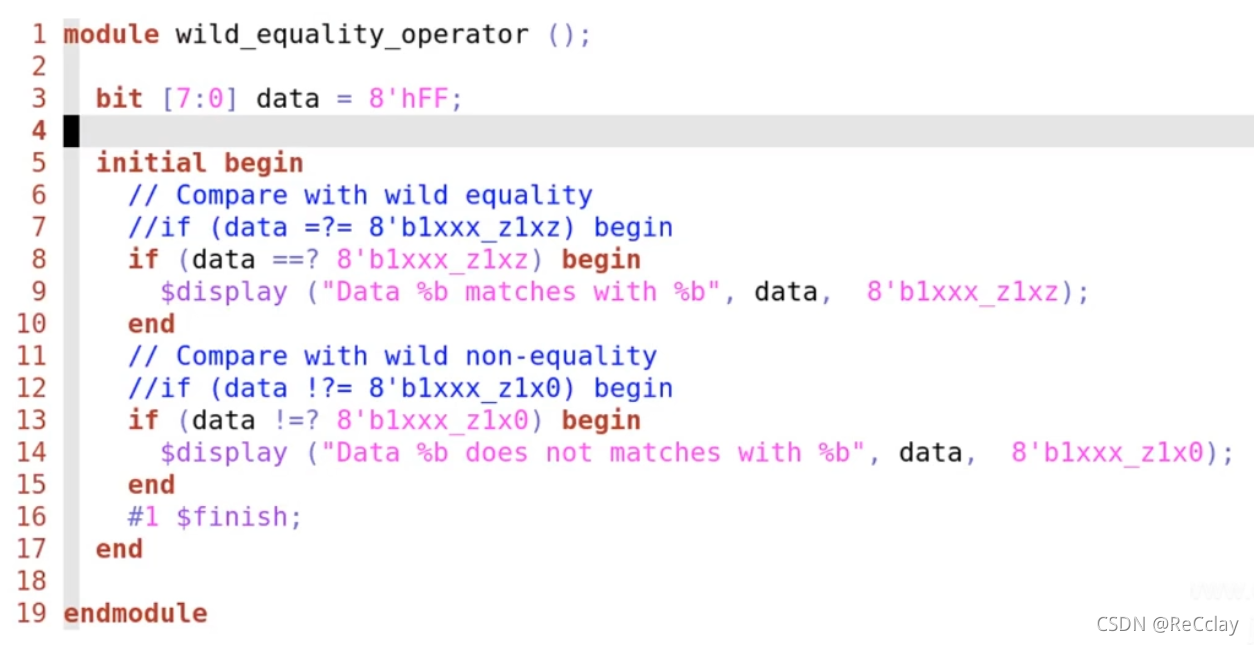

3.3、inside Mots clés

- insideC'est bon. Correspond à n'importe quelle valeur dans une plage de données

Quatre、VariablesConversion de type(Type Casting)

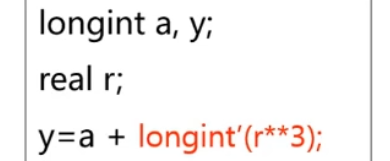

4.1、Convertisseur de type variabletype' (expression)

- SystemVerilog AjoutéConvertisseur de type variable:

type' (expression)- Le convertisseur de type variable peut typer une expression à tout moment

- Contrairement àVerilog La même chose ne peut se produire que dans une instruction d'affectation

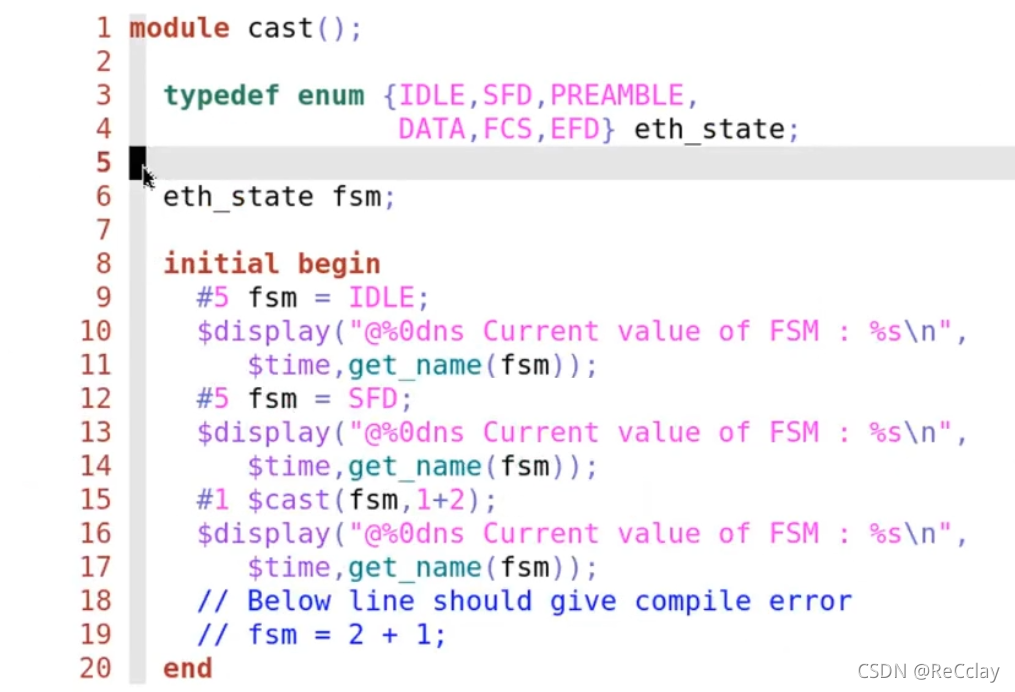

4.2、$castForcer la conversion de type

$cast(fsm, 1+2):Prends ça.3Assigner une valeur àfsm, Et convertir le type de force entier en type d'énumération ,C'est maintenant.fsmPourDATA

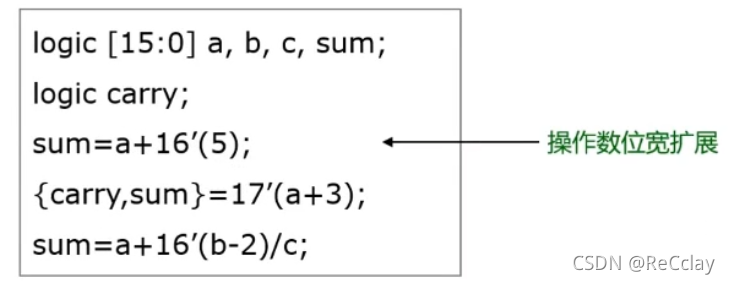

4.3、Conversion de la largeur du BIT variable(Size Casting)

- SystemVerilog Ajouté Largeur du BIT vectoriel Conversion

size' (expression)- Expression convertie en Petit Largeur du BIT ,Gauche. Les bits latéraux sont Supprimer

- Expression convertie en Grand Largeur du BIT ,Gauche. Les bits latéraux sont Élargissement

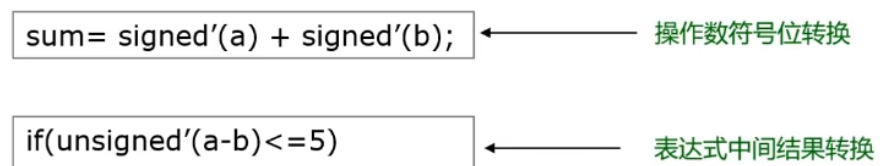

4.4、 Conversion de bits de symboles variables

- SystemVerilog Les bits de symbole peuvent être convertis

signed' (expression)Etunsigned' (expression)- Conversion de bits de symbole d'opérande

- Résultat de l'expression symbole bit conversion

Cinq、SystemVerilog Instruction de contrôle de la boucle

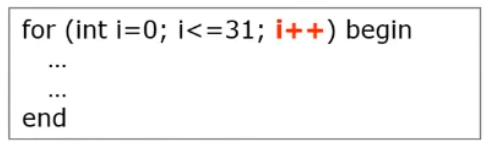

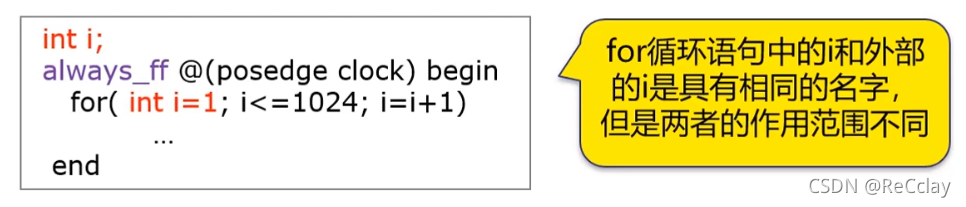

5.1、forDéclaration circulaire

Verilog La variable de boucle moyenne doit être for Déclaration en dehors de l'énoncé

- La boucle actuelle interagit avec d'autres déclarations

SystemVerilog Ça pourrait être dansfor Déclaration des variables de boucle à l'intérieur de la boucle

- Chaque variable est une variable locale unique , Ainsi, les variables du même nom utilisées à l'extérieur ne s'influencent pas mutuellement

- La variable de boucle locale est automatisée (automatic)

- for Les variables locales déclarées à l'intérieur de la boucle n'existent pas en dehors de l'instruction de boucle

- InVerilog La logique combinatoire et la logique séquentielle sont décrites dans

alwaysMots clés,Logique temporellealways @(posedge clk);Logique combinatoirealways @(*) - InSystemVerilogMoyenne, Pour décrire la logique des séries chronologiques

always_ff @(posedge clk)Oualways @(posedge clk);Logique combinatoirealways_comb @(*)Oualways @(*)

continue

- Uniquement pour les déclarations circulaires

- Fin du cycle,Continuez le prochain cycle

break

- Uniquement pour les déclarations circulaires

- Cycle de rupture ,Sortir de la boucle, N'exécutez plus cette boucle

return

- Peut être utilisé pour les déclarations circulaires

- Fin du cycle

- Peut également être utilisé pourtaskEtfunction

- FintaskEtfunction

- Peut être utilisé pour les déclarations circulaires

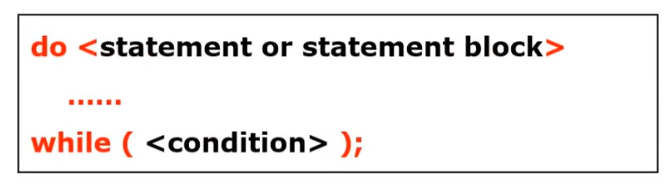

5.2、do...while Déclaration circulaire

- Verilog Danswhile Le cycle n'est pas nécessairement exécuté

- Si la valeur de la première expression de boucle est fausse , L'instruction de boucle ne s'exécute pas

- SystemVerilog Ajouté

do...whileDéclaration circulaire(SimilaireCLangues)- Exécuter l'instruction de boucle au moins une fois

- Déterminer les variables cycliques à la fin de l'instruction cyclique

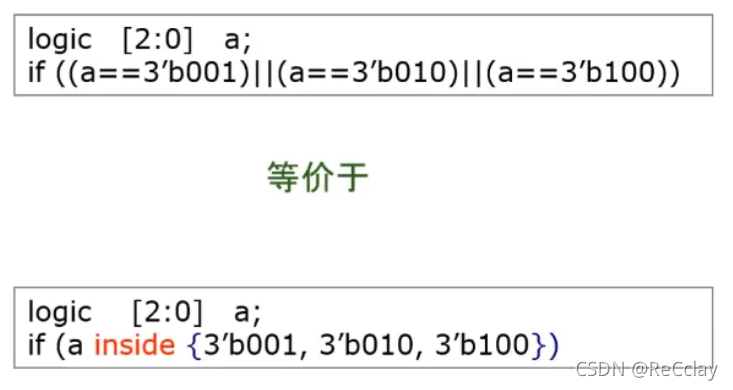

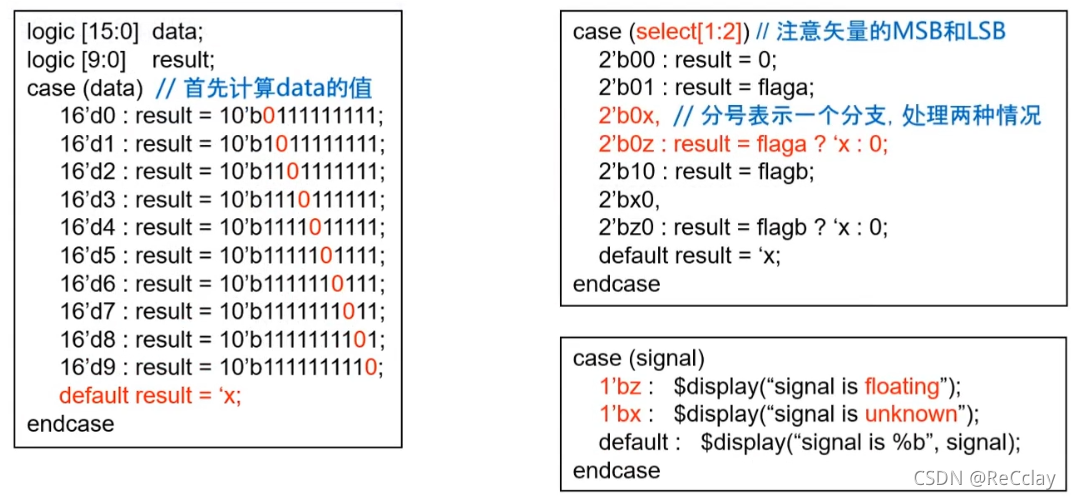

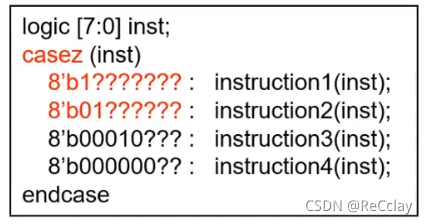

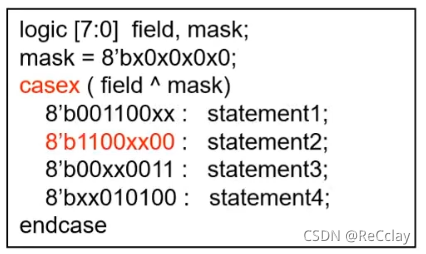

5.3、SystemVerilog AméliorationcaseDéclarations - case/casex/casez

- default Oui facultatif,Dans uncaseDans la Déclaration Plusieurs default

- Calculez d'abordcaseLa valeur de l'expression, Et ensuite correspondre à la branche réelle ci - dessous , Pour correspondre, exécutez l'instruction correspondante

- caseLa valeur de l'expression est Répartition par bit ,On peut s'en occuper.

xEtz

casez- Peu importe

z

- Peu importe

Note:: Un point d'interrogation indique un joker

casex- Peu importe

zEtx

- Peu importe

- Quand

field = 8'b01100110Heure,casexSélectionner une branchestatement2Mise en œuvre field ^ mask = x1x0x1x0

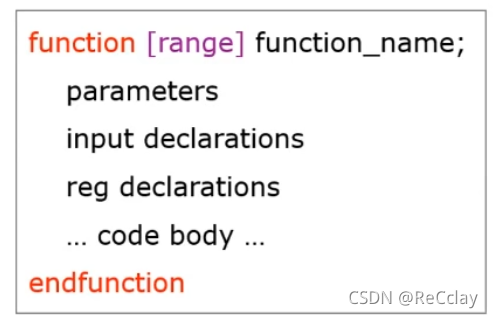

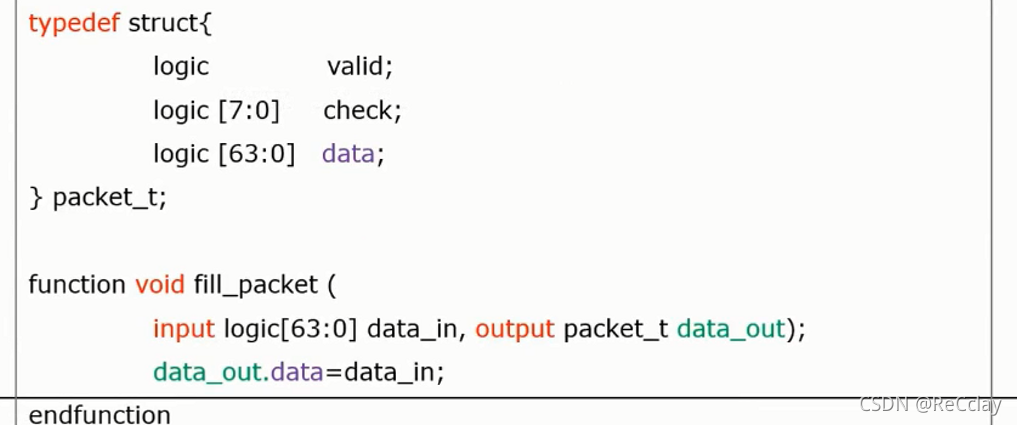

Six、SystemVerilog Mission(task)Et fonctions(function)

6.1、Verilog task Et functionGénéralités

function

- Quand la fonction s'exécute Pas de temps de simulation

- En fonction Impossible d'avoir des déclarations qui contrôlent le temps de simulation

- Il ne peut pas y avoir de délai de simulation :#100 =(`timescale 1ns/10ps)

- Il ne peut pas y avoir de déclaration de blocage :

@(posedge clock)Ouwait(ready) - Impossible d'appelertask

void functionAucune valeur de retour- Verilog De

functionDoit avoir une valeur de retour(Verilog Retour par nom de fonction !)

- Verilog De

function int sum(input x, y);

sum = x + y;

return sum;

endfunction

- 1

- 2

- 3

- 4

- task

- taskContient:input、outputEtinoutDéclarations

- task Temps de simulation consommé

- Retard:#20

- Cycle d'horloge:@(posedge clock)

- Événements:event

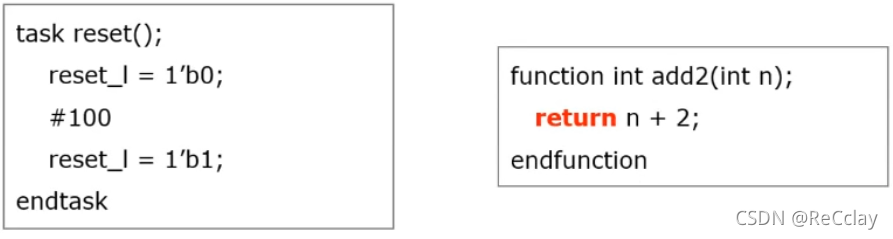

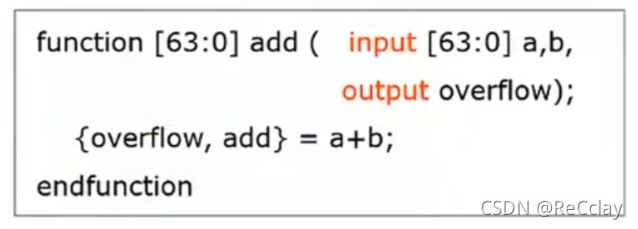

6.2、SystemVerilog task Et function

- tasks Et function

- - Non.À utiliserbegin…endDéclarations

- Ajouté

returnDéclarations- La valeur de retour n'est que1- Oui.return;Retour

bit/logicCe type simple de variable

- La valeur de retour n'est que1- Oui.return;Retour

void functionAucune valeur de retourfunctionOui.outputEtinoutComme paramètre formel- Valeur de retour supérieure à1Heures,Avecoutput Retour facile ;Retour

array/queue/structUtilisation complexeoutput

- Valeur de retour supérieure à1Heures,Avecoutput Retour facile ;Retour

C'est une analogie.,function Sans informations chronologiques , En général, décrire la logique combinatoire ;task Peut apporter des informations chronologiques , La logique combinatoire peut être décrite , La logique temporelle peut également être décrite !

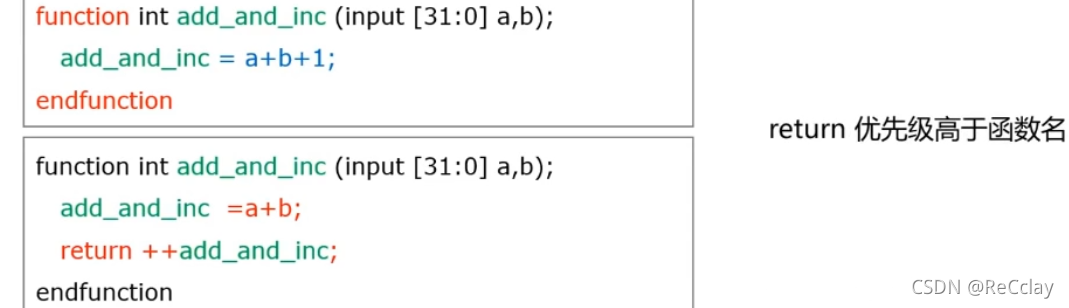

- return Déclarations

- SystemVerilog AjoutéreturnDéclarations

- return Lors de l'exécution de l'instructionRenvoie la valeur de l'expression, Sinon, la dernière valeur retournée Assigner une valeur au nom de la fonction

- return Instruction de sortie taskEtfunction

void function- void function Aucune valeur de retour

outputEtinoutLe paramètre formel estvoid function Fournit un moyen de transférer des variablesvoid functionPeut ressembler àtaskLa même chose est appelée, Mais doit être compatible avec les contraintes de contenu de la fonction

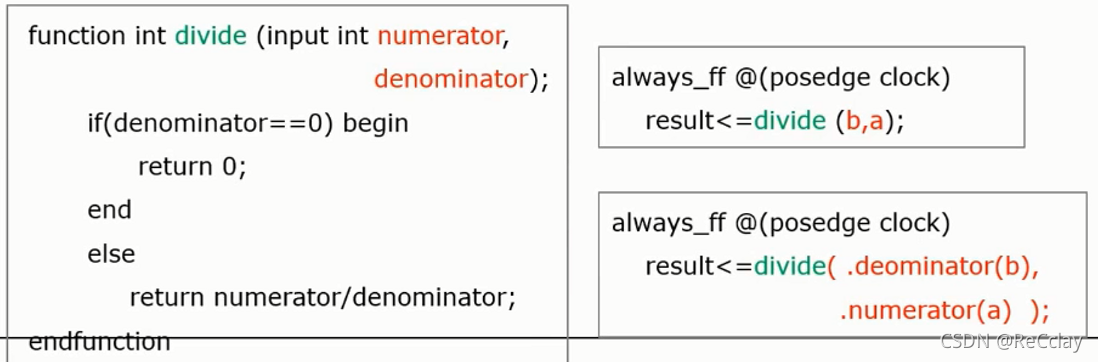

- Par nom taskEtfunctionParamètres

- SystemVerilog Passer un paramètre par le nom du paramètre formel

- Réduire les erreurs

- L'ordre des paramètres n'est pas limité

- La syntaxe des paramètres de passage est comparée à Verilog Les ports sont connectés de la même manière

- SystemVerilog Passer un paramètre par le nom du paramètre formel

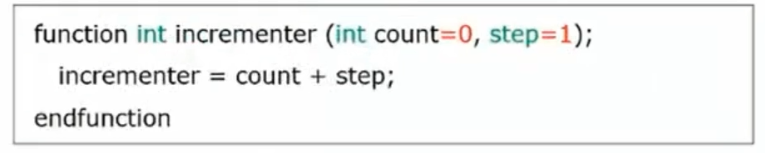

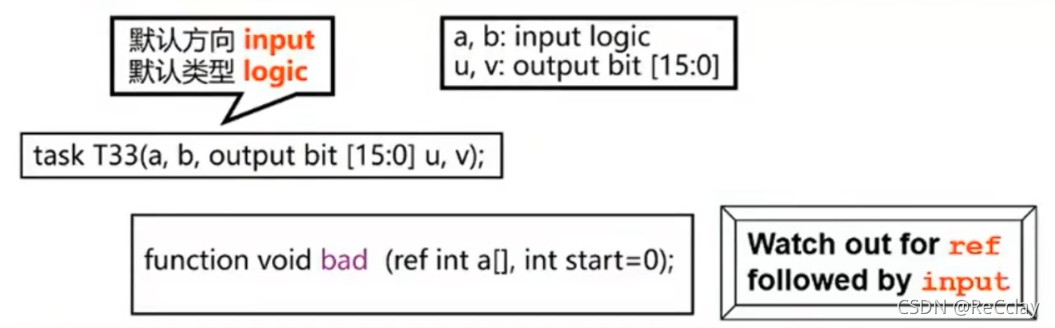

SystemVerilog Amélioration des paramètres de forme de la fonction

- AjoutéinputEtoutput

Direction et type par défaut des paramètres de forme

- Chaque paramètre formel a un type par défaut

- AppeleztaskEtfunctionHeure, Il n'est pas nécessaire de passer un paramètre à un paramètre avec une valeur de paramètre par défaut

- Si vous ne passez pas la valeur du paramètre ,Les valeurs par défaut sont utilisées

eg:

always_ff @(posedge clock)

result = incrementer(data_bus);// Les paramètres qui ne sont pas explicitement passés utilisent les valeurs par défaut ,C'est - à - dire:result = data_bus + 1;

- 1

- 2

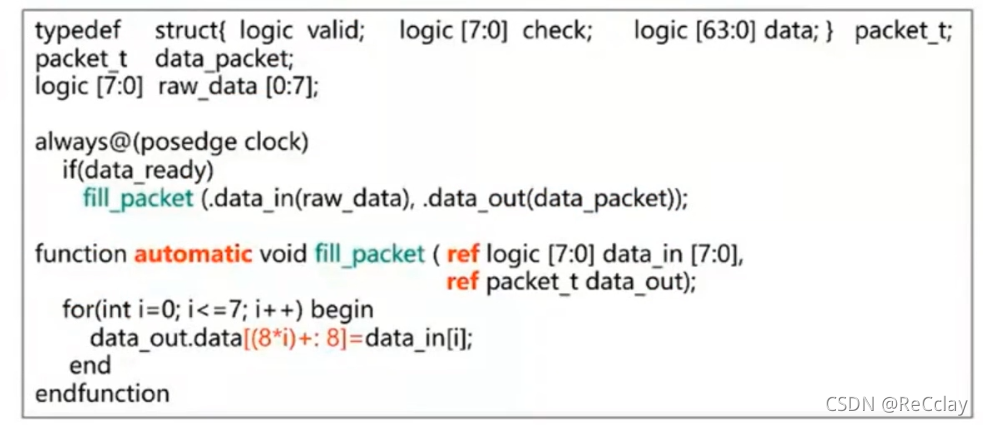

Utiliser des références(reference) Passer les paramètres d'une autre manière que la copie

- Tâches courantes (task)Et fonctions(function) La méthode de transmission des valeurs des paramètres est Copier

- Utiliser des références(reference) De façon explicite à la tâche (task)Et fonctions(function)Paramètres de passage

- Les mots clés sont::

ref(Remplacéinput, output Ou inout) - Seulement automatique (

automatic) Les tâches et les fonctions peuvent être utiliséesrefParamètres

- Les mots clés sont::

(8*i)+:8Dans:Sens:Prends ça.forExpansion de la boucle,Comme quandi=0Heure,(8*0)+:8Représentation0:0+8(0:8);QuandiDe=1Heure,(8*1)+:8Représentation8:16,Par là.forCycle,Je l'ai traversé.data[63:0]- Il existe trois façons de représenter un vecteur :

[MSB:LSB]、[MSB-:WIDTH]、[LSB+:WIDTH], Si l'ordre correspond[7:0]、[7-:8]([7:0])、[0+:8]([0:7])

Utiliser des références(reference) Passer les paramètres d'une autre manière que la copie

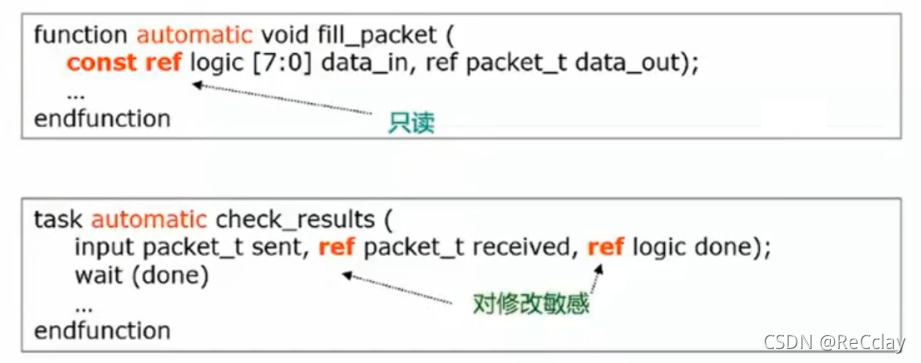

- Les paramètres passés par référence peuvent être en lecture seule (read-only)

- Allow task/function Référence à l'information dans le cadre de l'appel

- Bloquer task/function Modifier les informations référencées

- Modifiertask ref Les paramètres sont très sensibles

- ref Le paramètre peut lire la valeur actuelle

- ref Les paramètres transmettent immédiatement les changements d'information

Passage des paramètres

- Type de paramètre par défaut compatible avec le type de paramètre à gauche

- input - Par défaut, Saisissez une valeur pour copier au début

- output - Sortie pour copier une valeur à la fin

- inout - Entrez au début , Sortie à la fin , Une copie de la valeur

- ref - Transmission par référence , Les effets se manifestent immédiatement

- Quand le tableau est passé à taskEtfunctionHeure, Peut économiser du temps et du contenu

- const - Le paramètre ne peut pas être modifié

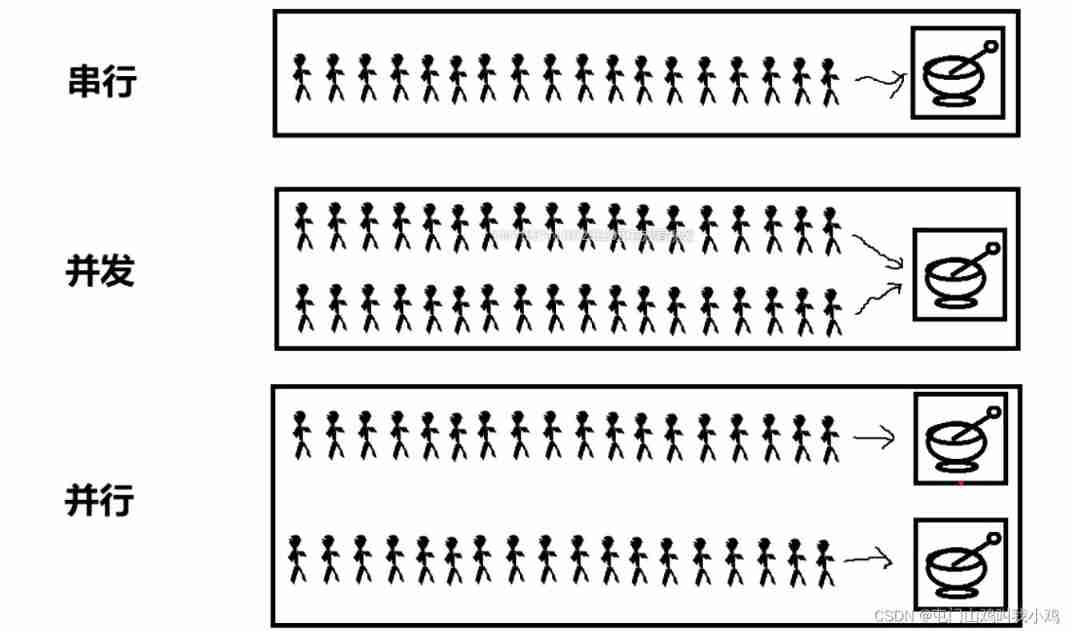

Questions d'entrevue courantes:taskEtfunctionLa différence?

- a. Consommation de temps de simulation ou non ,C'est - à - dire:task Il peut y avoir des déclarations qui consomment du temps de simulation ,function Il ne peut pas y avoir de déclarations qui prennent du temps ,task Il n'y a pas besoin de temps de simulation .

- b. taskPeut être appeléfunction,functionImpossible d'appelertask.

- c. InverilogMoyenne: taskPlusieurs valeurs peuvent être retournées(output),functionUne seule valeur peut être retournée

- d. taskEst - ce quereturnDe, void functionNon, pas du tout.returnDe

taskEtfunction Peut être intégré ?

- Peut être intégré , Selon l'énoncé de l'utilisateur à l'intérieur RTL Ou une description comportementale

- Par exemple,taskOufunctionOui.

$display("xxx");,Alors, ça.taskOufunction Ça ne doit pas être intégré .wait/#10L'attente ne peut pas non plus être intégrée !

Sept、Exercices pratiques

7.1 Exercice des opérateurs logiques et opérationnels

7.1.1、Comparer les opérateursdemo

sv_operation.sv

module SV_OPERATION();

bit sig_a;

bit sig_lgc_inv_a;

bit sig_bit_inv_a;

bit [2:0] sig_m_a;

bit [2:0] sig_m_lgc_inv_a;

bit [2:0] sig_m_bit_inv_a;

bit signed [7:0] sig_c;

bit signed [7:0] sig_lgc_lft_c;

bit signed [7:0] sig_lgc_rgt_c;

bit signed [7:0] sig_arth_lft_c;

bit signed [7:0] sig_arth_rgt_c;

int i;

logic [7:0] comp_a;

logic [7:0] comp_b;

logic [2:0] a;

logic comp1 [8];

logic comp2 [8];

initial begin

sig_a = 1'b0; sig_m_a = 3'b010;

sig_c = 8'sb1100_0111; sig_lgc_inv_a = !sig_a; sig_bit_inv_a = ~sig_a; sig_m_lgc_inv_a = !sig_m_a; sig_m_bit_inv_a = ~sig_m_a; comp_a = 8'b0100_1101;

comp_b = 8'b0100_1100; if(comp_a == comp_b) begin $display("******comp_a: %b == comp_b: %b", comp_a, comp_b); end else begin $display("******comp_a: %b != comp_b: %b", comp_a, comp_b); end if(comp_a === {comp_b[7:1], 1'bx}) begin

$display("******comp_a: %b === {comp_b[7:1], 1'bx}: %b", comp_a, {

comp_b[7:1], 1'bx}); end else begin $display("******comp_a: %b !== {comp_b[7:1], 1'bx}: %b", comp_a, {comp_b[7:1], 1'bx}); end if(comp_a ==? {comp_b[7:1], 1'bx}) begin $display("******comp_a: %b ==? {

comp_b[7:1], 1'bx}: %b", comp_a, {comp_b[7:1], 1'bx});

end

else begin

$display("******comp_a: %b !=? {comp_b[7:1], 1'bx}: %b", comp_a, {

comp_b[7:1], 1'bx});

end

end

endmodule

rslt.log

******comp_a: 01001101 != comp_b: 01001100

******comp_a: 01001101 !== {

comp_b[7:1], 1'bx}: 0100110x ******comp_a: 01001101 ==? {comp_b[7:1], 1'bx}: 0100110x

- 1

- 2

- 3

- Makefile Même chose.No14Monographie,Mais si.

comp_fileLes paramètres ont changé.:make comp_file=sv_operation.sv sig_aÇa veut dire un simple ,sig_m_aÇa veut dire Multi - bitssig_c = 8'sb1100_0111;DanssIndique signé- La logique monobit est inversée

!Et la position inverse~C'est pareil; Mais dobit est différent ! comp_xxxReprésente la variable utilisée pour la comparaison

7.1.2、Opérateurs logiques! Et les opérateurs arithmétiques ~Différencesdemo

sv_operation.sv

$display("******single bit logic invertor ! :sig_a is : %b, sig_lgc_inv_a is : %b", sig_a, sig_lgc_inv_a);

$display("******single bit bit invertor ~ :sig_a is : %b, sig_bit_inv_a is : %b", sig_a, sig_bit_inv_a);

$display("******multiple bit logic invertor ! :sig_m_a is : %b, sig_m_lgc_inv_a is : %b", sig_m_a, sig_m_lgc_inv_a);

$display("******multiple bit bit invertor ~ :sig_m_a is : %b, sig_m_bit_inv_a is : %b", sig_m_a, sig_m_bit_inv_a);

rslt.log

******single bit logic invertor ! :sig_a is : 0, sig_lgc_inv_a is : 1

******single bit bit invertor ~ :sig_a is : 0, sig_bit_inv_a is : 1

******multiple bit logic invertor ! :sig_m_a is : 010, sig_m_lgc_inv_a is : 000

******multiple bit bit invertor ~ :sig_m_a is : 010, sig_m_bit_inv_a is : 101

- Pour la logique monobit inverse

!Et la position inverse~Aucune différence; Et dobit est différent

7.1.3、Opération Shiftdemo

sv_operation.sv

sig_lgc_lft_c = sig_c << 5; sig_lgc_rgt_c = sig_c >> 5; sig_arth_lft_c = sig_c <<< 5; sig_arth_rgt_c = sig_c >>> 5; $display("******logical left shift << :sig_c is : %b, sig_lgc_lft_c is : %b", sig_c,sig_lgc_lft_c); $display("******logical right shift >> :sig_c is : %b, sig_lgc_rgt_c is : %b", sig_c,sig_lgc_rgt_c); $display("******arithmetic left shift <<< :sig_c is : %b, sig_arth_lft_c is : %b", sig_c,sig_arth_lft_c); $display("******arithmetic right shift >>> :sig_c is : %b, sig_arth_rgt_c is : %b", sig_c,sig_arth_rgt_c);

rslt.log******logical left shift << :sig_c is : 11000111, sig_lgc_lft_c is : 11100000 ******logical right shift >> :sig_c is : 11000111, sig_lgc_rgt_c is : 00000110 ******arithmetic left shift <<< :sig_c is : 11000111, sig_arth_lft_c is : 11100000 ******arithmetic right shift >>> :sig_c is : 11000111, sig_arth_rgt_c is : 11111110

- Logique gauche/À droite., Après le déplacement, utilisez

0Allez. - Le déplacement arithmétique à gauche est le même que le déplacement logique à gauche ; Si le BIT le plus élevé est

1,Alors, remplissez.1. De même, si le BIT le plus élevé est0,Alors, remplissez.0

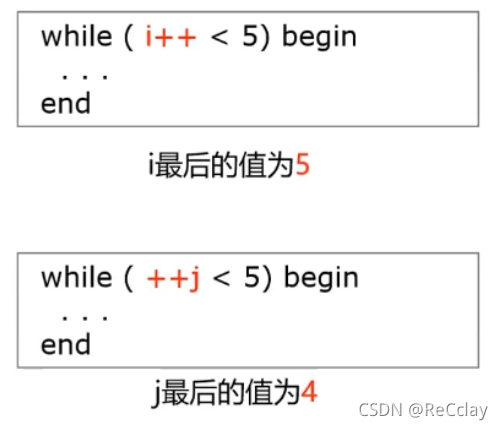

7.1.4、++iEti++La différencedemo

sv_operation.sv

i = 0;

while(i++ < 5) begin

$display("****** the i++ i %d", i);

end

i = 0;

while(++i < 5) begin

$display("****** the ++i i %d", i);

end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

rslt.log

****** the i++ i 1

****** the i++ i 2

****** the i++ i 3

****** the i++ i 4

****** the i++ i 5

****** the ++i i 1

****** the ++i i 2

****** the ++i i 3

****** the ++i i 4

7.1.5、insideMots clésdemo

sv_operation.sv

for(int i=0; i<8; i++) begin a = i[2:0]; if(a==3'b100 || a==3'b101 || a==3'b011) begin comp1[i] = 1'b1; end else begin comp1[i] = 1'b0; end if(a inside{3'b100, 3'b101, 3'b011}) begin comp2[i] = 1'b1; end else begin comp2[i] = 1'b0; end end if(comp1 == comp2) begin $display("******comp1 == comp2"); end else begin $display("******comp1 != comp2"); end

rslt.log******comp1 == comp2

- 1

7.2、Exercices circulaires

7.2.1、Différentinitial Les blocs partagent la même variable globale demo

sv_loop_case.sv

module sv_loop_case();

int j;

int i;

initial begin : loop0

for(i=0; i<5; i++) begin

#1;

$display("******loop0 i = %0d", i);

end

end

initial begin : loop1

for(i=0; i<5; i++) begin

#1;

$display("******loop1 i = %0d", i);

end

end

endmodule

******loop0 i = 0

******loop1 i = 1

******loop0 i = 2

******loop1 i = 3

******loop0 i = 4

******loop1 i = 5

- On peut voir deuxinitial Les blocs partagent la même variable globale i,for La circulation a un effet !

7.2.2、Différentinitial Les blocs utilisent des variables locales demo

sv_loop_case.sv

module sv_loop_case(); //int j; //int i; initial begin : loop0 for(int i=0; i<5; i++) begin // Attention, il y a une définition int, Appelé la variable locale ! #1; $display("******loop0 i = %0d", i); end end initial begin : loop1 for(int i=0; i<5; i++) begin #1; $display("******loop1 i = %0d", i); end end endmodule

rslt.log******loop0 i = 0 ******loop1 i = 0 ******loop0 i = 1 ******loop1 i = 1 ******loop0 i = 2 ******loop1 i = 2 ******loop0 i = 3 ******loop1 i = 3 ******loop0 i = 4 ******loop1 i = 4

- On peut voir deuxintialLe blocfor Le cycle n'affecte pas !

7.2.3、DifférentinitialUtilisation de blocsautomaticDéfinir les variablesdemo

sv_loop_case.sv

module sv_loop_case(); //int j; //int i; initial begin : loop0 automatic int i; for(i=0; i<5; i++) begin #1; $display("******loop0 i = %0d", i); end end initial begin : loop1 automatic int i; for(int i=0; i<5; i++) begin #1; $display("******loop1 i = %0d", i); end end endmodule

rslt.log******loop0 i = 0 ******loop1 i = 0 ******loop0 i = 1 ******loop1 i = 1 ******loop0 i = 2 ******loop1 i = 2 ******loop0 i = 3 ******loop1 i = 3 ******loop0 i = 4 ******loop1 i = 4

- Vous pouvez voir l'utilisationautomatic Définir une variable a le même effet que l'utilisation d'une variable locale ,Deux.initialLe blocfor Les cycles ne s'influencent pas les uns les autres

7.2.4、while Et do...while Processus d'exécutiondemo

sv_loop_case.sv

initial begin j = 0; do begin $display("******%d th loop in do while loop", j); j++; end while(j<0); j=0; while(j<0) begin $display("******%d th loop in while loop", j); j++; end end

rslt.log****** 0 th loop in do while loop

- 1

- Je vois.

do...whileIl sera exécuté une fois en premier,Encore un jugement

7.3、case/casez/casex Exercice de différenciation des branches

sv_loop_case.sv

logic [3:0] sel_z = 4'bz01z; logic [3:0] sel_x = 4'bx01x;

initial begin

case(sel_z)

4'b1??? : $display("****** sel_z(%0b) is 4'b1??? in case selection", sel_z); 4'b01?? : $display("****** sel_z(%0b) is 4'b01?? in case selection", sel_z); 4'b001? : $display("****** sel_z(%0b) is 4'b001? in case selection", sel_z);

4'b0001 : $display("****** sel_z(%0b) is 4'b0001 in case selection", sel_z); default : $display("****** sel_z(%0b) is in default branch in case selection", sel_z); endcase casez(sel_z) 4'b1??? : $display("****** sel_z(%0b) is 4'b1??? in casez selection", sel_z); 4'b01?? : $display("****** sel_z(%0b) is 4'b01?? in casez selection", sel_z);

4'b001? : $display("****** sel_z(%0b) is 4'b001? in casez selection", sel_z); 4'b0001 : $display("****** sel_z(%0b) is 4'b0001 in casez selection", sel_z); default : $display("****** sel_z(%0b) is in default branch in case selection", sel_z); endcase case(sel_x) 4'b1??? : $display("****** sel_x(%0b) is 4'b1??? in case selection", sel_x);

4'b01?? : $display("****** sel_x(%0b) is 4'b01?? in case selection", sel_x); 4'b001? : $display("****** sel_x(%0b) is 4'b001? in case selection", sel_x); 4'b0001 : $display("****** sel_x(%0b) is 4'b0001 in case selection", sel_x);

default : $display("****** sel_x(%0b) is in default branch in case selection", sel_x);

endcase

casex(sel_x)

4'b1??? : $display("****** sel_x(%0b) is 4'b1??? in casex selection", sel_x); 4'b01?? : $display("****** sel_x(%0b) is 4'b01?? in casex selection", sel_x); 4'b001? : $display("****** sel_x(%0b) is 4'b001? in casex selection", sel_x);

4'b0001 : $display("****** sel_x(%0b) is 4'b0001 in casex selection", sel_x); default : $display("****** sel_x(%0b) is in default branch in case selection", sel_x);

endcase

end

rslt.log

****** sel_z(z01z) is in default branch in case selection

****** sel_z(z01z) is 4'b1??? in casez selection ****** sel_x(x01x) is in default branch in case selection ****** sel_x(x01x) is 4'b1??? in casex selection

- 1

- 2

- 3

- 4

casezPeu importez,C'est - à - dire:zPeut être considéré comme0Ou1.casexPeu importezEtx,C'est - à - dire:xEtzPeut être considéré comme0Ou1.- Un point d'interrogation indique un joker ,case La correspondance générale à l'intérieur

?,Ça veut juste dire0Et1;casezÀ l'intérieur.?Tong Pai,Peut représenter0/1/z;casexÀ l'intérieur.?Tong Pai,Peut représenter0/1/x/z. z01zEt001?Peut également correspondre à , Mais ça correspond déjà au précédent1???,Donc, à l'arrière,001?Ça ne correspond plus- IncaseMoyenne, Si une branche est

z01z,Alorssel_z Ça correspond à cette branche ,Correspondance stricte!

7.4、task/function Exercice

7.4.1、function Structure encapsulée demo

sv_function_task.sv

module sv_function_task();

typedef struct {

int height;

int weight;

logic [7:0] legs;

logic [1:0] hands;

logic [1:0] eyes;

logic noses;

}animal;

animal duck;

animal dog;

animal d;

logic [76:0] data_in;

string name;

initial begin

duck.height = 32'd132; duck.weight = 32'd200;

duck.legs = 8'd2; duck.hands = 2'd2;

duck.eyes = 2'd2; duck.noses = 1'd1;

$display("******@%0tns duck unpacked value ******", $time);

$display("******@%0tns duck height : %0d ****", $time, duck.height);

$display("******@%0tns duck weight : %0d ****", $time, duck.weight);

$display("******@%0tns duck legs : %0d ****", $time, duck.legs);

$display("******@%0tns duck hands : %0d ****", $time, duck.hands);

$display("******@%0tns duck eyes : %0d ****", $time, duck.eyes);

$display("******@%0tns duck noses : %0d ****", $time, duck.noses);

dog.height = 32'd232; dog.weight = 32'd100;

dog.legs = 8'd4; dog.hands = 2'd0;

dog.eyes = 2'd2; dog.noses = 1'd1;

$display("******@%0tns dog unpacked value ******", $time);

$display("******@%0tns dog height : %0d ****", $time, dog.height);

$display("******@%0tns dog weight : %0d ****", $time, dog.weight);

$display("******@%0tns dog legs : %0d ****", $time, dog.legs);

$display("******@%0tns dog hands : %0d ****", $time, dog.hands);

$display("******@%0tns dog eyes : %0d ****", $time, dog.eyes);

$display("******@%0tns dog noses : %0d ****", $time, dog.noses);

end

function void animal_assign (input [76:0] data_in, output animal animal_obj);

animal_obj.height = data_in[76 -: 32];

animal_obj.weight = data_in[76-32 -: 32];

animal_obj.legs = data_in[76-32-32 -: 8];

animal_obj.hands = data_in[76-32-32-8 -: 2];

animal_obj.eyes = data_in[76-32-32-8-2 -: 2];

animal_obj.noses = data_in[0];

endfunction

function void animal_display (input string name, input animal animal_obj);

$display("******@%0tns %s unpacked value animal_assign&animal_display******", $time, name);

$display("******@%0tns %s height : %0d ****",$time, name, animal_obj.height);

$display("******@%0tns %s weight : %0d ****",$time, name, animal_obj.weight);

$display("******@%0tns %s legs : %0d ****",$time, name, animal_obj.legs);

$display("******@%0tns %s hands : %0d ****",$time, name, animal_obj.hands);

$display("******@%0tns %s eyes : %0d ****",$time, name, animal_obj.eyes);

$display("******@%0tns %s noses : %0d ****",$time, name, animal_obj.noses);

endfunction

initial begin

data_in = {

32'd132, 32'd200, 8'd2, 2'd2, 2'd2, 1'd1};

animal_assign(data_in, duck);

name="duck";

animal_display(name, duck);

data_in = {

32'd132, 32'd100, 8'd2, 2'd0, 2'd2, 1'd1};

animal_assign(data_in, dog);

name="dog";

animal_display(name, dog);

end

endmodule

rslt.log

******@0ns duck unpacked value ******

******@0ns duck height : 132 ****

******@0ns duck weight : 200 ****

******@0ns duck legs : 2 ****

******@0ns duck hands : 2 ****

******@0ns duck eyes : 2 ****

******@0ns duck noses : 1 ****

******@0ns dog unpacked value ******

******@0ns dog height : 232 ****

******@0ns dog weight : 100 ****

******@0ns dog legs : 4 ****

******@0ns dog hands : 0 ****

******@0ns dog eyes : 2 ****

******@0ns dog noses : 1 ****

******@0ns duck unpacked value animal_assign&animal_display******

******@0ns duck height : 132 ****

******@0ns duck weight : 200 ****

******@0ns duck legs : 2 ****

******@0ns duck hands : 2 ****

******@0ns duck eyes : 2 ****

******@0ns duck noses : 1 ****

******@0ns dog unpacked value animal_assign&animal_display******

******@0ns dog height : 132 ****

******@0ns dog weight : 100 ****

******@0ns dog legs : 2 ****

******@0ns dog hands : 0 ****

******@0ns dog eyes : 2 ****

******@0ns dog noses : 1 ****

7.4.2、refParamètresdemo

sv_function_task.sv

module sv_function_task();

typedef struct {

int height;

int weight;

logic [7:0] legs;

logic [1:0] hands;

logic [1:0] eyes;

logic noses;

}animal;

animal duck;

animal dog;

animal d;

logic [76:0] data_in;

string name;

/*initial begin

duck.height = 32'd132; duck.weight = 32'd200;

duck.legs = 8'd2; duck.hands = 2'd2;

duck.eyes = 2'd2; duck.noses = 1'd1;

$display("******@%0tns duck unpacked value ******", $time);

$display("******@%0tns duck height : %0d ****", $time, duck.height);

$display("******@%0tns duck weight : %0d ****", $time, duck.weight);

$display("******@%0tns duck legs : %0d ****", $time, duck.legs);

$display("******@%0tns duck hands : %0d ****", $time, duck.hands);

$display("******@%0tns duck eyes : %0d ****", $time, duck.eyes);

$display("******@%0tns duck noses : %0d ****", $time, duck.noses);

dog.height = 32'd232; dog.weight = 32'd100;

dog.legs = 8'd4; dog.hands = 2'd0;

dog.eyes = 2'd2; dog.noses = 1'd1;

$display("******@%0tns dog unpacked value ******", $time);

$display("******@%0tns dog height : %0d ****", $time, dog.height);

$display("******@%0tns dog weight : %0d ****", $time, dog.weight);

$display("******@%0tns dog legs : %0d ****", $time, dog.legs);

$display("******@%0tns dog hands : %0d ****", $time, dog.hands);

$display("******@%0tns dog eyes : %0d ****", $time, dog.eyes);

$display("******@%0tns dog noses : %0d ****", $time, dog.noses);

end

function void animal_assign (input [76:0] data_in, output animal animal_obj);

animal_obj.height = data_in[76 -: 32];

animal_obj.weight = data_in[76-32 -: 32];

animal_obj.legs = data_in[76-32-32 -: 8];

animal_obj.hands = data_in[76-32-32-8 -: 2];

animal_obj.eyes = data_in[76-32-32-8-2 -: 2];

animal_obj.noses = data_in[0];

endfunction

function void animal_display (input string name, input animal animal_obj);

$display("******@%0tns %s unpacked value animal_assign&animal_display******", $time, name);

$display("******@%0tns %s height : %0d ****",$time, name, animal_obj.height);

$display("******@%0tns %s weight : %0d ****",$time, name, animal_obj.weight);

$display("******@%0tns %s legs : %0d ****",$time, name, animal_obj.legs);

$display("******@%0tns %s hands : %0d ****",$time, name, animal_obj.hands);

$display("******@%0tns %s eyes : %0d ****",$time, name, animal_obj.eyes);

$display("******@%0tns %s noses : %0d ****",$time, name, animal_obj.noses);

endfunction

initial begin

data_in = {

32'd132, 32'd200, 8'd2, 2'd2, 2'd2, 1'd1};

animal_assign(data_in, duck);

name="duck";

animal_display(name, duck);

data_in = {

32'd132, 32'd100, 8'd2, 2'd0, 2'd2, 1'd1};

animal_assign(data_in, dog);

name="dog";

animal_display(name, dog);

end*/

task automatic animal_assign(ref [76:0] data_in, ref animal animal_obj);

animal_obj.height = data_in[76 -: 32];

animal_obj.weight = data_in[76-32 -: 32];

animal_obj.legs = data_in[76-32-32 -: 8];

animal_obj.hands = data_in[76-32-32-8 -: 2];

animal_obj.eyes = data_in[76-32-32-8-2 -: 2];

animal_obj.noses = data_in[0];

endtask

task automatic animal_display(ref string name, ref animal animal_obj);

$display("******@%0tns %s unpacked value automatic animal_assign&animal_display******", $time, name);

$display("******@%0tns %s height : %0d ****",$time, name, animal_obj.height);

$display("******@%0tns %s weight : %0d ****",$time, name, animal_obj.weight);

$display("******@%0tns %s legs : %0d ****",$time, name, animal_obj.legs);

$display("******@%0tns %s hands : %0d ****",$time, name, animal_obj.hands);

$display("******@%0tns %s eyes : %0d ****",$time, name, animal_obj.eyes);

$display("******@%0tns %s noses : %0d ****",$time, name, animal_obj.noses);

endtask

task automatic animal_assign_modified(ref [76:0] data_in, ref animal animal_obj);

animal_obj.height = data_in[76 -: 32];

animal_obj.weight = data_in[76-32 -: 32];

animal_obj.legs = data_in[76-32-32 -: 8];

animal_obj.hands = data_in[76-32-32-8 -: 2];

animal_obj.eyes = data_in[76-32-32-8-2 -: 2];

animal_obj.noses = data_in[0];

data_in = '0; endtask initial begin data_in = {32'd132, 32'd200, 8'd2, 2'd2, 2'd2, 1'd1}; animal_assign(data_in, duck); name = "duck"; animal_display(name, duck) data_in = {32'd132, 32'd100, 8'd2, 2'd0, 2'd2, 1'd1};

animal_assign(data_in, dog);

name = "dog";

animal_display(name, dog);

animal_assign_modified(data_in, dog);

animal_display(name, dog);

$display("******After data_in modified by dog structure");

animal_assign(data_in, duck);

name = "duck";

animal_display(name, duck);

end

endmodule

rslt.log

******@0ns duck unpacked value automatic animal_assign&animal_display******

******@0ns duck height : 132 ****

******@0ns duck weight : 200 ****

******@0ns duck legs : 2 ****

******@0ns duck hands : 2 ****

******@0ns duck eyes : 2 ****

******@0ns duck noses : 1 ****

******@0ns dog unpacked value automatic animal_assign&animal_display******

******@0ns dog height : 132 ****

******@0ns dog weight : 100 ****

******@0ns dog legs : 2 ****

******@0ns dog hands : 0 ****

******@0ns dog eyes : 2 ****

******@0ns dog noses : 1 ****

******@0ns dog unpacked value automatic animal_assign&animal_display******

******@0ns dog height : 132 ****

******@0ns dog weight : 100 ****

******@0ns dog legs : 2 ****

******@0ns dog hands : 0 ****

******@0ns dog eyes : 2 ****

******@0ns dog noses : 1 ****

******After data_in modified by dog structure

******@0ns duck unpacked value automatic animal_assign&animal_display******

******@0ns duck height : 0 ****

******@0ns duck weight : 0 ****

******@0ns duck legs : 0 ****

******@0ns duck hands : 0 ****

******@0ns duck eyes : 0 ****

******@0ns duck noses : 0 ****

- Vous pouvez voir les changements

refVariables référencées, Alors appelez cette variable à nouveau , Cette variable est la valeur modifiée . refFacile à faire des erreurs, L'utilisation réelle n'est pas recommandée .

RÉFÉRENCES

边栏推荐

- 3D reconstruction - stereo correction

- Quickly use Jacobo code coverage statistics

- Linux server development, SQL statements, indexes, views, stored procedures, triggers

- Hands on deep learning (IV) -- convolutional neural network CNN

- pytest+allure+jenkins安装问题:pytest: error: unrecognized arguments: --alluredir

- Pytest+allure+jenkins installation problem: pytest: error: unrecognized arguments: --alluredir

- 【p2p】本地抓包

- [performance pressure test] how to do a good job of performance pressure test?

- Explore Cassandra's decentralized distributed architecture

- 探索干货篇!Apifox 建设思路

猜你喜欢

探索干货篇!Apifox 建设思路

Linux server development, MySQL transaction principle analysis

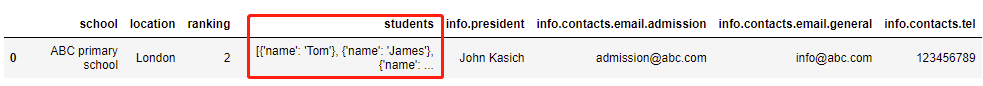

json 数据展平pd.json_normalize

![[Matlab] Simulink 自定义函数中的矩阵乘法工作不正常时可以使用模块库中的矩阵乘法模块代替](/img/e3/cceede6babae3c8a24336c81d98aa7.jpg)

[Matlab] Simulink 自定义函数中的矩阵乘法工作不正常时可以使用模块库中的矩阵乘法模块代替

Iterable、Collection、List 的常见方法签名以及含义

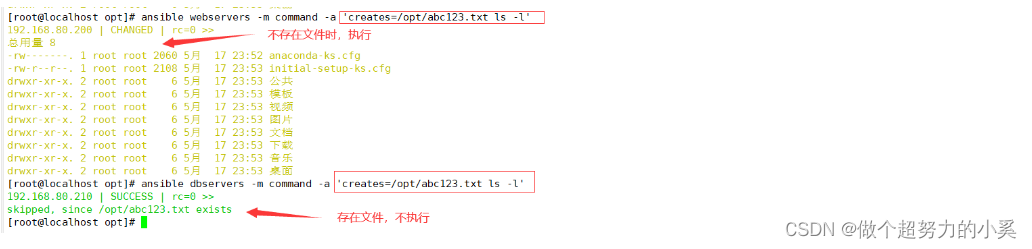

Ansible

QT learning 28 toolbar in the main window

Linux server development, redis protocol and asynchronous mode

![[SUCTF 2019]Game](/img/9c/362117a4bf3a1435ececa288112dfc.png)

[SUCTF 2019]Game

These five fishing artifacts are too hot! Programmer: I know, delete it quickly!

随机推荐

Chip information website Yite Chuangxin

Téléchargement des données de conception des puces

Wechat applet data binding multiple data

[Matlab] Simulink 自定义函数中的矩阵乘法工作不正常时可以使用模块库中的矩阵乘法模块代替

Operation suggestions for today's spot Silver

Padavan manually installs PHP

numpy中dot函数使用与解析

Info | webrtc M97 update

Linux server development, SQL statements, indexes, views, stored procedures, triggers

Gslx680 touch screen driver source code analysis (gslx680. C)

Linux server development, MySQL stored procedures, functions and triggers

Mysql高低版本切换需要修改的配置5-8(此处以aicode为例)

misc ez_usb

buuctf misc USB

[CV] Wu Enda machine learning course notes | Chapter 8

2022茶艺师(初级)考试题模拟考试题库及在线模拟考试

misc ez_ usb

Rust versus go (which is my preferred language?)

These five fishing artifacts are too hot! Programmer: I know, delete it quickly!

Linux server development, MySQL transaction principle analysis