当前位置:网站首页>[VHDL parallel statement execution]

[VHDL parallel statement execution]

2022-07-07 07:53:00 【Both delicious and fun_】

VHDL A way to judge the rising edge of a signal

General detection clock rising edge

Method 1 :rising_edge Is a very strict rising edge , Must be from 0 To 1 ,

Method 2 :(clk’event and clk=‘1’) It can be downloaded from X To 1

Both ways are well understood

/

problem

Because of the recent contact FPGA, Study VHDL Language , Encountered a problem that beginners may encounter

clk10khz_d1 <= clk10khz;

clk10khz_d2 <= clk10khz_d1;

if key_cs='1' and clk10khz_d1='1' and clk10khz_d2='0' then --( Judge the rising edge )

.......

end if;

See here ,clk10khz The value of clk10khz_d1 , clk10khz_d1 The value of clk10khz_d2,

thus clk10khz ,clk10khz_b1 ,clk10khz_b2 It shouldn't be the same ? Is it wrong ?

Later, I saw a lot of code to detect the rising edge , It's all like this , There's no explanation .

In fact, that is Nonblocking assignment and Block assignment The difference between , Senior VHDL Players will feel that this problem is too basic .

What is non blocking assignment ?

The non blocking assignment operator uses the less than or equal sign ( namely <=) Express .

For calculating the non blocking assignment character at the beginning of the assignment operation time RHS expression , Update at the end of the assignment operation time LHS. When calculating non blocking assignment RHS Expressions and updates LHS period , Other statements , Including other non blocking assignment statements can be calculated at the same time RHS Expressions and updates LHS. Nonblocking assignment allows other statements to operate at the same time .

The non blocking assignment is determined by the clock beat , When the clock rises , Execute the assignment statement , And then begin-end All assignment statements between are assigned to the left of the assignment statement at the same time , Be careful : yes begin—end All statements between , Do it together , And a clock executes only once .

The results of two different assignment methods are different , Nonblocking assignment b<=a;c<=b; Two statements are executed at the same time , And block assignment b=a;c=b; Two statements are executed first b=a After execution c=b.

Why can we detect the rising edge ?

Know what is non blocking assignment , Then it is easy to understand the method of detecting the rising edge

clk10khz_d1 <= clk10khz;

clk10khz_d2 <= clk10khz_d1;

Execute two sentences together , hypothesis clk10khz Status as …01… ( On the rising edge )

At low levels clk10khz_d1 , clk10khz_d2 Are endowed with 0 ,

Along the rising edge , When executing two sentences at the same time clk10khz_d2 still Before being clk10khz_d1 The stored value is assigned to 0;

here clk10khz Rise to 1 , clk10khz_d1 To be an assignment 1.

Thus through clk10khz_d1='1' and clk10khz_d2='0 The rising edge of the detection signal .

That is to say, the order of two assignment statements is not important , The reverse result is the same .

边栏推荐

- Pytest+allure+jenkins environment -- completion of pit filling

- buuctf misc USB

- 今日现货白银操作建议

- Solve could not find or load the QT platform plugin "xcb" in "

- What is the interval in gatk4??

- dash plotly

- 2022焊工(初级)判断题及在线模拟考试

- 【斯坦福计网CS144项目】Lab3: TCPSender

- Is the test cycle compressed? Teach you 9 ways to deal with it

- misc ez_ usb

猜你喜欢

【webrtc】m98 screen和window采集

【斯坦福计网CS144项目】Lab4: TCPConnection

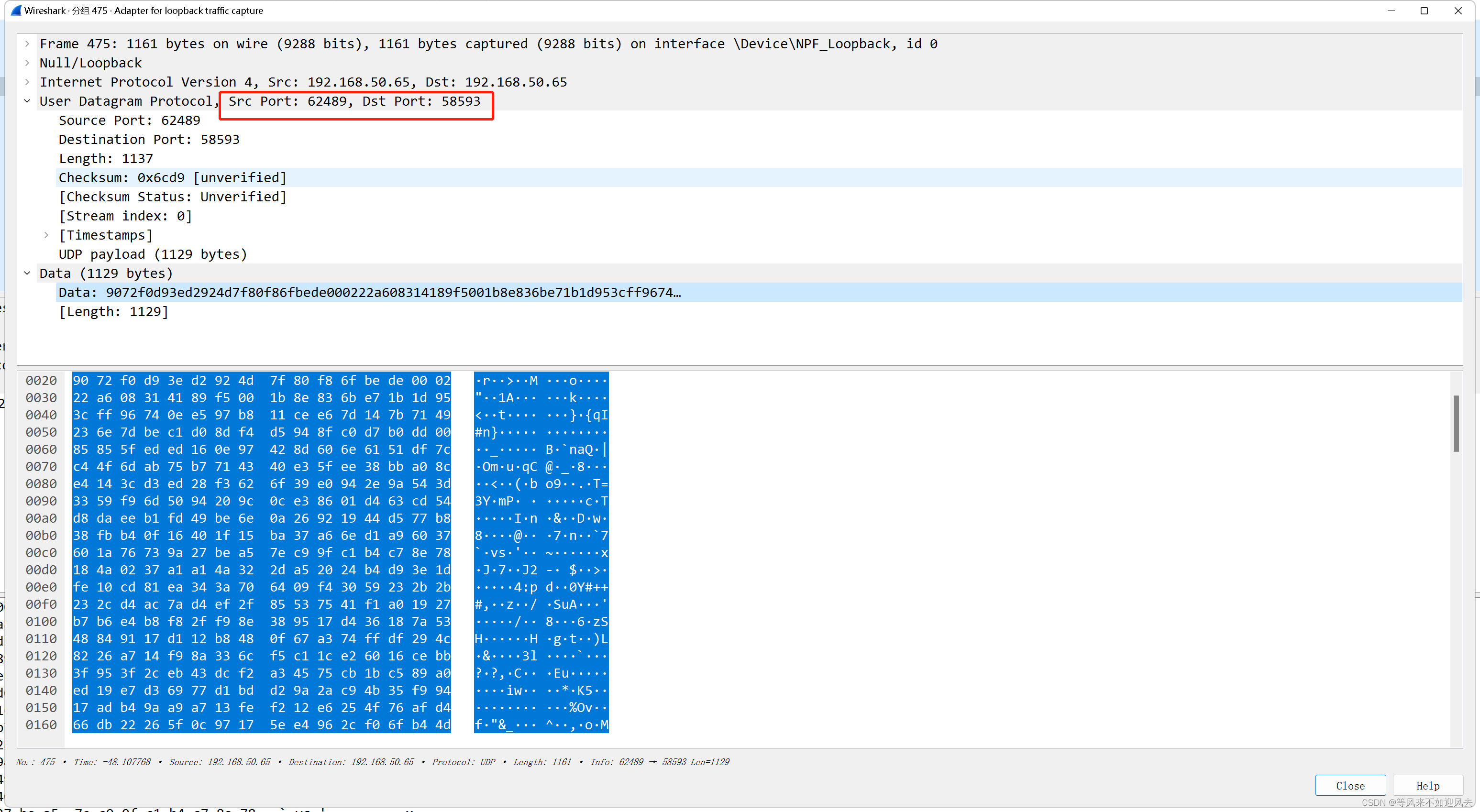

【p2p】本地抓包

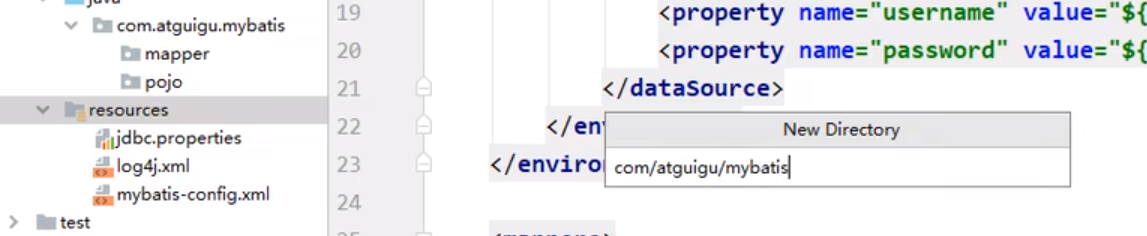

resource 创建包方式

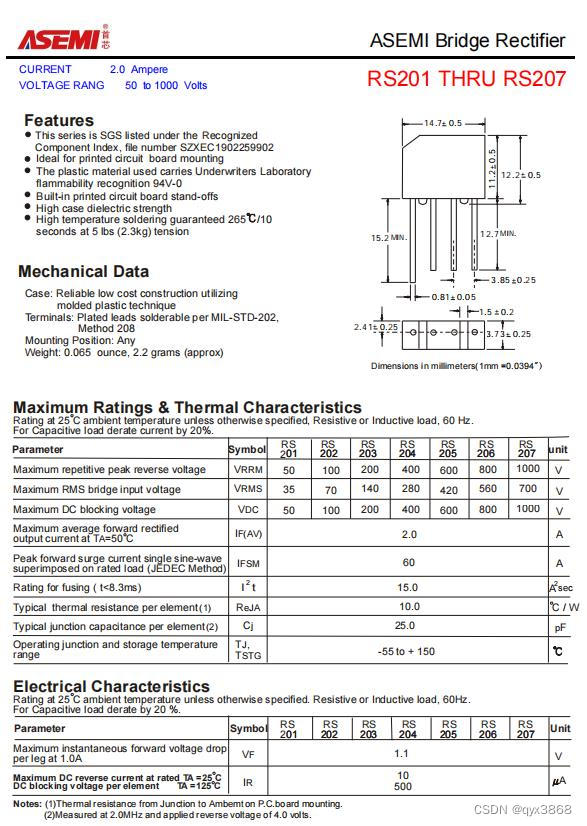

Asemi rectifier bridge rs210 parameters, rs210 specifications, rs210 package

Technology cloud report: from robot to Cobot, human-computer integration is creating an era

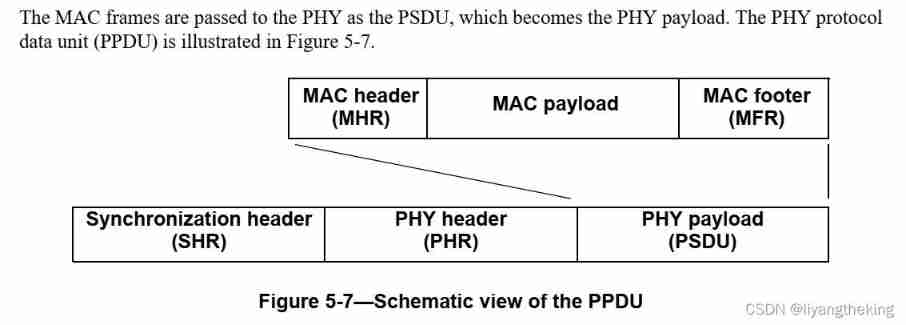

UWB learning 1

Why should we understand the trend of spot gold?

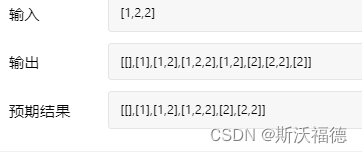

LeetCode 90:子集 II

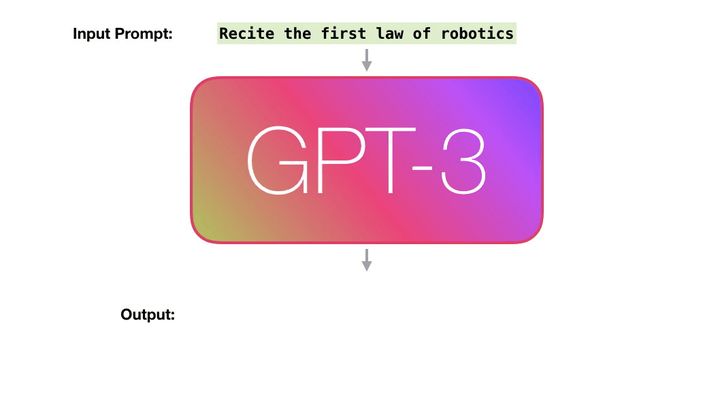

图解GPT3的工作原理

随机推荐

Numbers that appear only once

Installing postgresql11 database under centos7

You Li takes you to talk about C language 6 (common keywords)

[P2P] local packet capturing

Iterable、Collection、List 的常见方法签名以及含义

【VHDL 并行语句执行】

【经验分享】如何为visio扩展云服务图标

Solve could not find or load the QT platform plugin "xcb" in "

微信小程序中使用wx.showToast()进行界面交互

有 Docker 谁还在自己本地安装 Mysql ?

dash plotly

测试周期被压缩?教你9个方法去应对

Regular e-commerce problems part1

Live online system source code, using valueanimator to achieve view zoom in and out animation effect

Jenkins remote build project timeout problem

[UVM basics] summary of important knowledge points of "UVM practice" (continuous update...)

[ANSYS] learning experience of APDL finite element analysis

Common validation comments

Kbu1510-asemi power supply special 15A rectifier bridge kbu1510

Qt学习27 应用程序中的主窗口