当前位置:网站首页>[quick start of Digital IC Verification] 14. Basic syntax of SystemVerilog learning 1 (array, queue, structure, enumeration, string... Including practical exercises)

[quick start of Digital IC Verification] 14. Basic syntax of SystemVerilog learning 1 (array, queue, structure, enumeration, string... Including practical exercises)

2022-07-07 08:13:00 【luoganttcc】

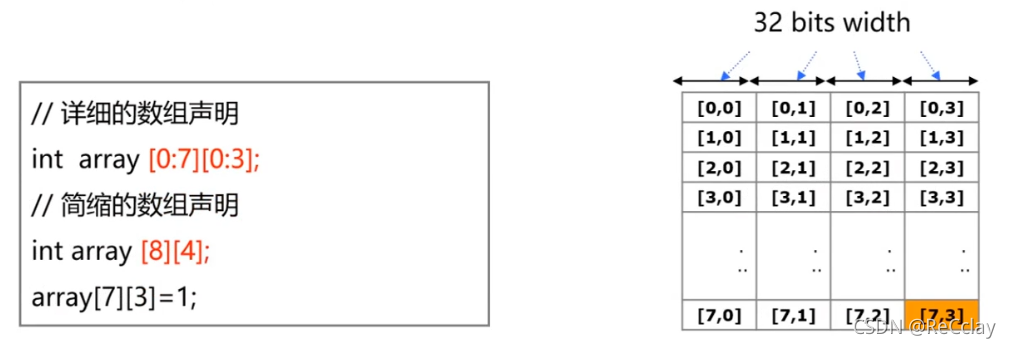

Reading guide : The author has the honor to be a pioneer in the field of electronic information in China “ University of electronic technology ” During postgraduate study , Touch the cutting edge Numbers IC Verification knowledge , I heard something like Huawei Hisilicon 、 Tsinghua purple light 、 MediaTek technology And other top IC related enterprises in the industry , Pairs of numbers IC Verify some knowledge accumulation and learning experience . Want to get started for help IC Verified friends , After one or two thoughts , This column is specially opened , In order to spend the shortest time , Take the least detours , Most learned IC Verify technical knowledge .

List of articles

- One 、 Description of content

- Two 、 Basic variables

- 3、 ... and 、 Fixed array

- 3.1、 One dimensional array

- 3.2、 Multidimensional arrays

- 3.3、 Basic operation of fixed array

- 3.4、 Unfilled array (unpacked array)

- 3.5、 Fill the array ( Compressed array ,Packed Array)

- 3.6、 Mixed array (Mixed Arrays)

- 3.7、 Compare a filled array with an unfilled array

- 3.8、 Fill array and constant array initialization are compared with memory storage

- 3.9、 Small test

- Four 、 The dynamic array

- 5、 ... and 、 queue ( With the more )

- 6、 ... and 、 Associative array ( Linked data )

- 7、 ... and 、 Array methods ( Built in functions )

- 8、 ... and 、 Array usage is recommended

- Nine 、 Structure

- Ten 、 enumeration

- 11、 ... and 、 character string

- Twelve 、 Practice

- 12.1、bit/logic practice

- 12.2、 Fixed array exercise

- 12.2.1、unpacked array ininial demo( Unfilled array initialization demo)

- 12.2.2、unpacked array assignment demo( Unfilled array assignment demo)

- 12.2.3、unpacked array partial assign demo( Partial assignment of unfilled array demo)

- 12.2.4、array over read demo( Array read out of bounds demo)

- 12.2.5、packed array assign demo( Fill array assignment demo)

- 12.3、 Dynamic array exercise

- 12.4、 Practice in line

- 12.5、 Array method practice

- 12.6、 Structure 、 Enumerate exercises

- 12.7、 String practice

One 、 Description of content

- data type : Four value variable 、 Binary variables

- If the four valued variable is 1bit, Then the four values are :0/1/x/z(x It's an unsteady state ;z It's a high resistance state , If 0 yes 0V,1 yes 0.8V, that z That is 0.5V/0.6V Left and right )

- Fixed array : initialization ( Direct assignment 、for、foreach)

- Fixed array :unpacked array & packed array

- Fixed array : Assignment and comparison

- The dynamic array

- queue

- Associative array

- Array methods ( function )

- Structure

- Enumeration type

- character string

Two 、 Basic variables

2.1、SystemVerilog Rule of grammar

and Verilog equally

- Case sensitive

- Spaces are not ignored , Except in string

- Annotation symbols

- Line notes :

// - Statement block comments :

/*...*/

- Line notes :

Number system format

<size>' <base> <number>'b(binary Binary system ):01xXzZ'd(decimal Decimal system ):0123456789'h(hexadecimal Hexadecimal ):0123456789abcdefABCDEFxXzZ

Use separator

“_”, Improve the readability :16'b1100_1011_1010_001032'hbeef_cafe

2.2、SystemVerilog New data types

- Binary logic : Better performance , Less memory

- queue , Dynamic arrays and associative arrays : Reduce memory usage , Support search and sorting

- Combine arrays and fill structures : The same data has different views (View)

- Classes and structs : Support the abstraction of data structure

- character string :SV Built in operation function

- Enumeration type : Easy to code and understand ( Commonly used in TestBench in )

2.3、SystemVerilog data type

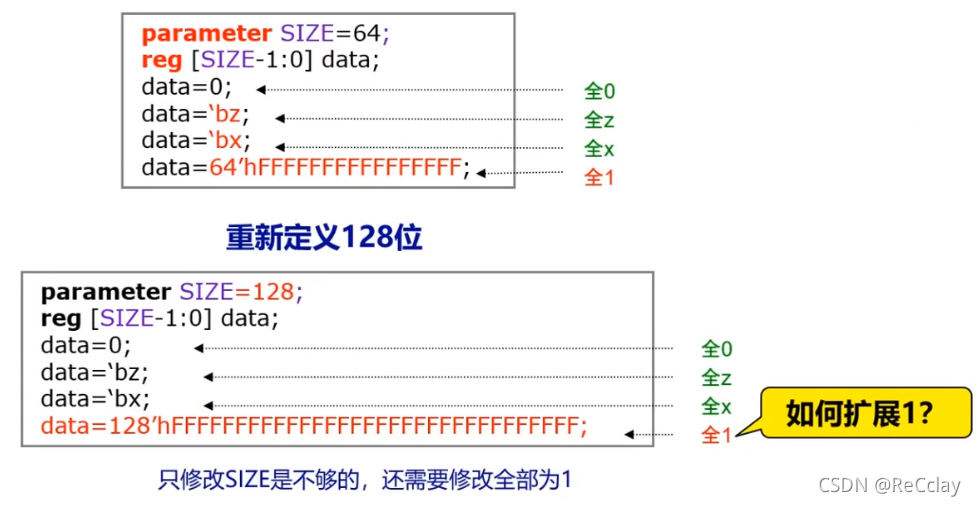

Verilog Assignment in language

- vector (vector, Position width greater than 1 The variable of ) Easy to assign to all

0/z/x, But the assignment is all1When , You need to write all the bits !

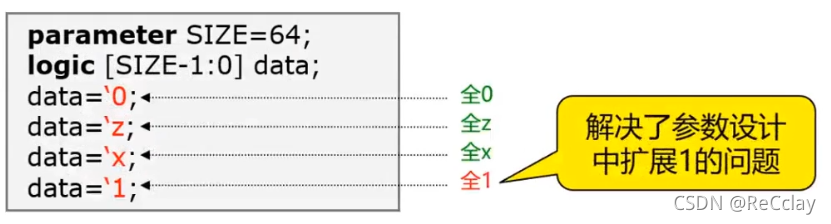

SystemVerilog Assignment

- There is no need to specify a hexadecimal number ( Binary system 、 octal 、 Decimal and hexadecimal numbers ) You can fill in 0/x/z

- All filled 1

Four value variable

Verilog

- reg: Universal variable , Use in

initialandalwaysIn the sentence , Modeling hardware modules- Combinational circuits and sequential circuits

- wire: It mainly plays a connecting role , Similar to metal wire ; stay

assignAssignment in

- reg: Universal variable , Use in

SystemVerilog

- logic(logic To replace the reg)

- Statements that can be consecutively assigned , Gate circuit or module drive

- Don't drive more , Such as bidirectional bus ( Need to use wire Modeling )

- logic(logic To replace the reg)

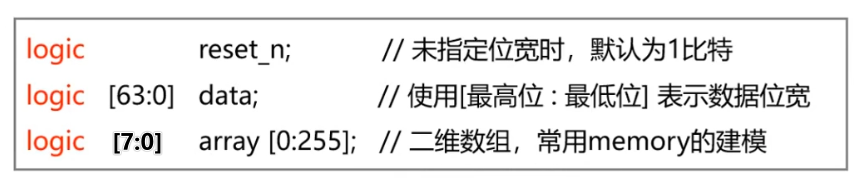

logic There are four states

- 0/1/x/z

- logic The variable defined is An unsigned number !

- give an example :

logic [31:0] data;

- give an example :

Common use :

logic reset_n; // Unspecified bit width , The default is 1bit

logic [63:0] data; // Use [ highest : Its lowest ] Indicates the data bit width

logic [7:0] array [0:255]; // Two dimensional array , Commonly used memory Modeling of

- 1

- 2

- 3

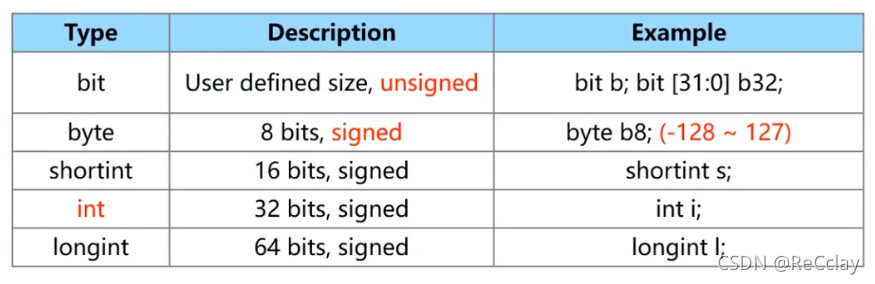

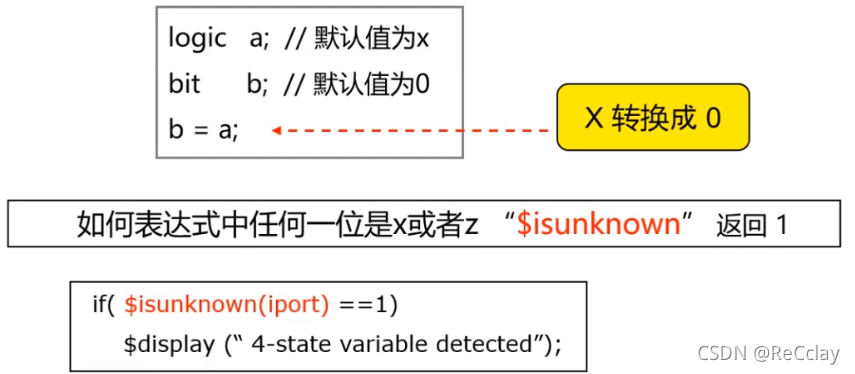

Binary variables :bit,byte,shortint,int,longint

- There are only two states 0 and 1(x and z Will be converted into a 0)

- Improve simulation performance , Reduce memory usage

- Not used for RTL Design ( because x or z The two states will be converted into 0)

bitOf The bit width is user-defined Of , And is An unsigned number ;byte/shortint/int/longintOf The bit width is fixed Of , And is Signed number !logicThe bit width of is also user-defined , And it's unsigned !

Make a little review about the data range of signed and unsigned numbers ,eg:2 A wide , namely

00 / 01 / 10 / 11Four forms , Represented in sequence in unsigned form :0 / 1 / 2 / 3; In symbolic form ( The highest bit is the sign bit ) In turn stands for :0 / 1 / -1 / -2- The complement of a positive number is itself , The complement of a negative number is negative plus 1

Q:

logic [7:0] xandbyte xAre they exactly alike? ?- A: Dissimilarity ,

logicIs a four valued variable ,byteIs a binary variable

- A: Dissimilarity ,

Logic simulation features

- The default initial value of the four value state variable is

x; The default initial value of the binary state variable is0 - Variables in binary state cannot represent uninitialized state (

x) - Variables in the four value state can be assigned to variables in the two value state .

xandzWill be converted into a 0 $isunknown(expression)You can check whether there is x or z

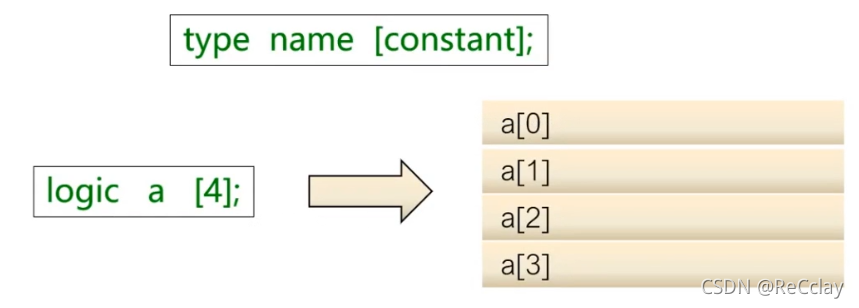

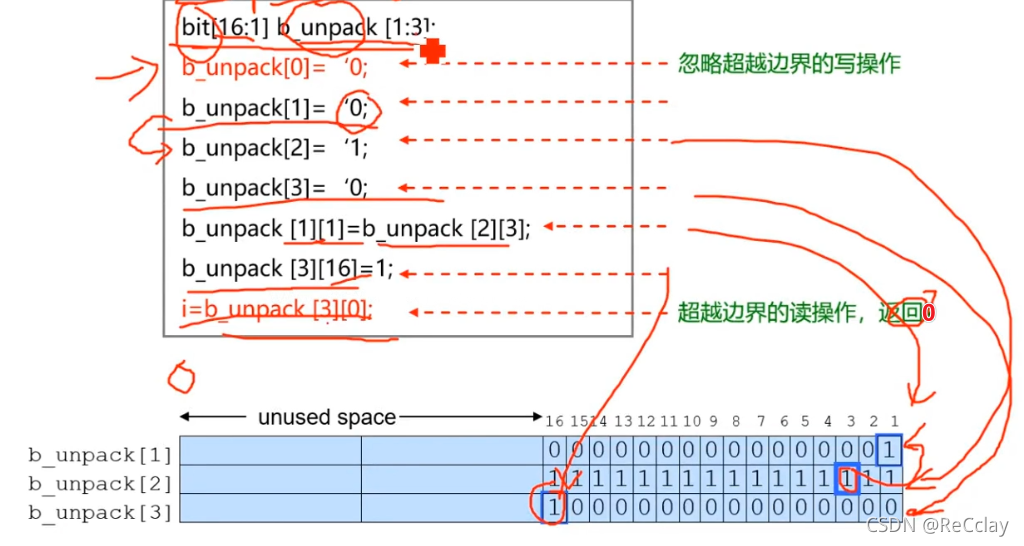

3、 ... and 、 Fixed array

- Support multidimensional array ( Algorithm vector operations are used more )

- Beyond the boundary Write operation ignored

- Beyond the boundary Read operations The return value is

x( Four valued state variables ),0( Binary state variables ) byte/shortint/intStore in 32 position In the storage space of ( obviouslybyteandshortintA little waste of storage space )longintStore in 64 position In the storage space of

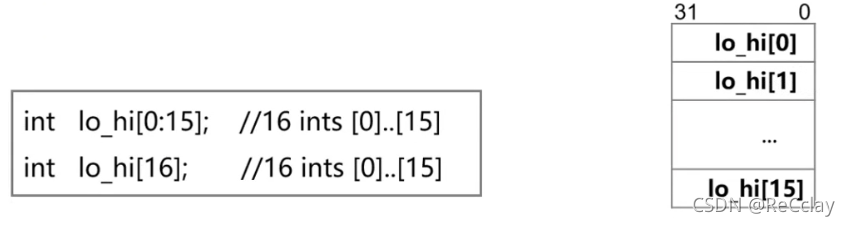

3.1、 One dimensional array

intEquivalent tobit signed [31:0]Statement of[0:15]、[16]There are two ways to specify the depth of a one-dimensional array , So the two ways of writing are equivalent .int lo_hi[0:15]Andint lo_hi[16]The elements of the writing are arranged in the same order ( from 0 Start to the maximum 15), howeverint lo_hi[15:0]The order of elements in the writing method is different from the previous ( from 15 Start to the minimum 0)!- Array

f[5]Equate tof[0:4], andforeach(f[i])Equate tofor(int i=0; i<=4; i++). - For arrays

rev[6:2]Come on ,foreach(rev[i])Equate tofor(int i=6; i>=2; i--).

int lo_hi[16]amount to16 That's ok x32 ColumnThe size of the matrix- take lo_hi pass the civil examinations 1 The number of 8bit:

lo_hi[1][8]

3.2、 Multidimensional arrays

3.3、 Basic operation of fixed array

3.3.1、 Fixed array initialization :'{} '{n{}}

- Full or partial initialization

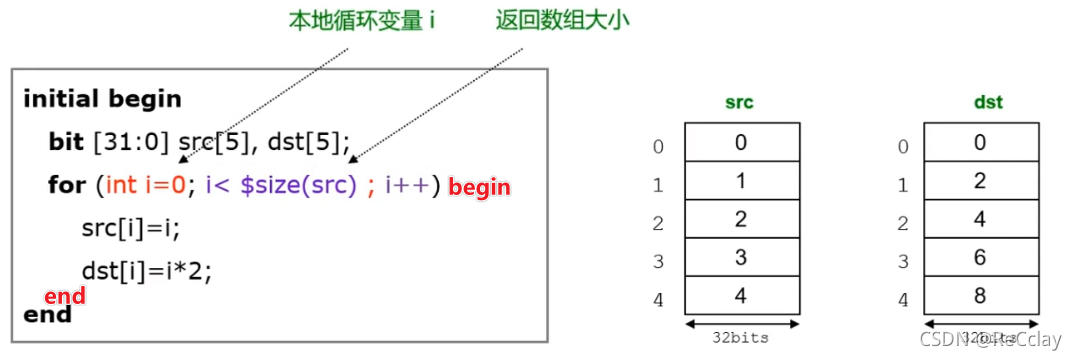

3.3.2、for: utilize for Loop statements to initialize

- The most common array initialization method

- Variable

iIs a local loop variable - System function

$sizeReturns the size of the array ( Fixed arrays can only be used$size)

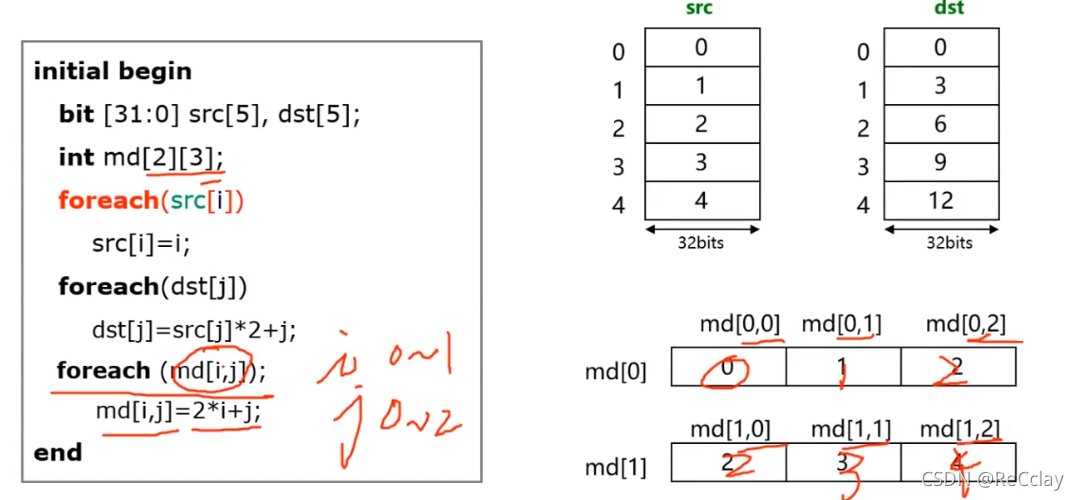

3.3.3、foreach: utilize foreach Loop statements to initialize

- Specify the array name , In square brackets are index numbers ,foreach It will traverse all array elements according to the index number

- Index numbers can be automatically declared as local loop variables

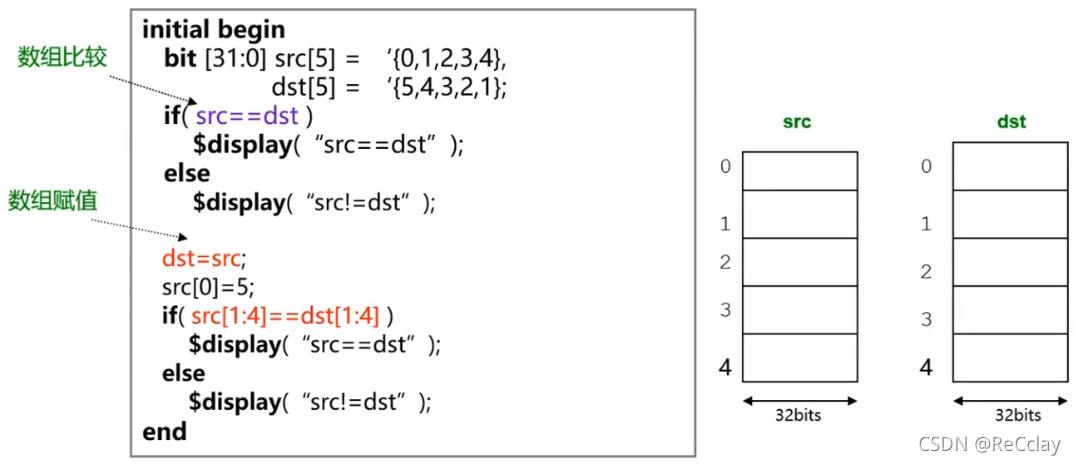

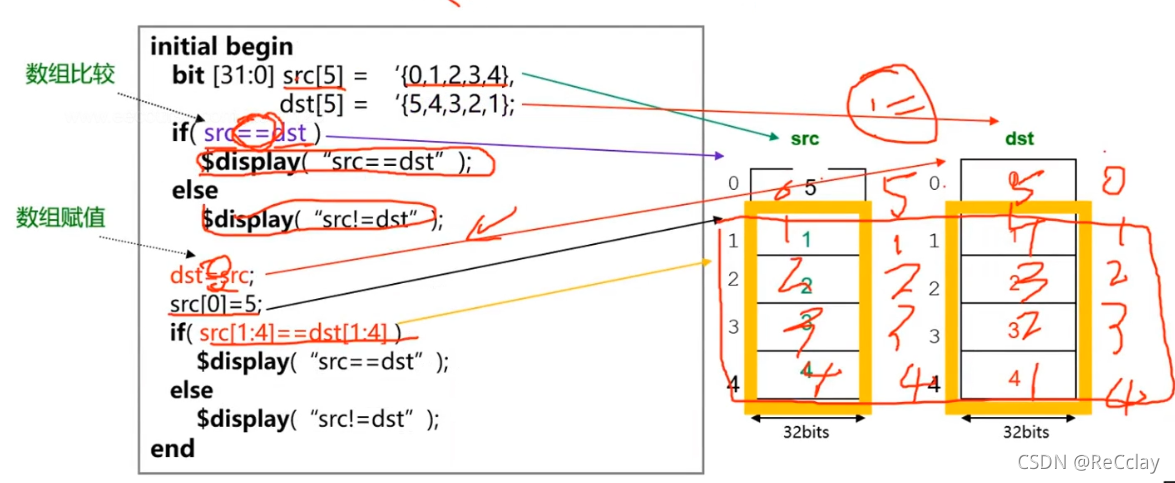

3.3.4、 Assignment and comparison of fixed arrays

- You can assign and compare arrays without loops ( only apply Operator equal sign

==And inequality!=)

3.3.5、 Array elements 、 Partial selection of array elements

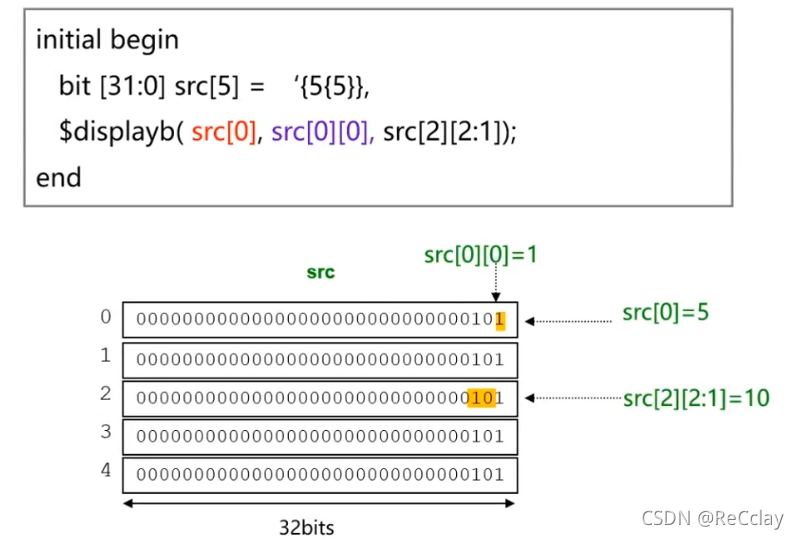

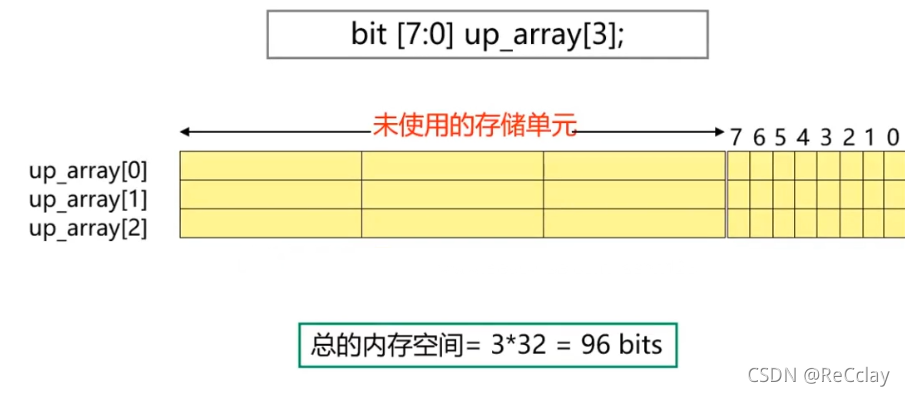

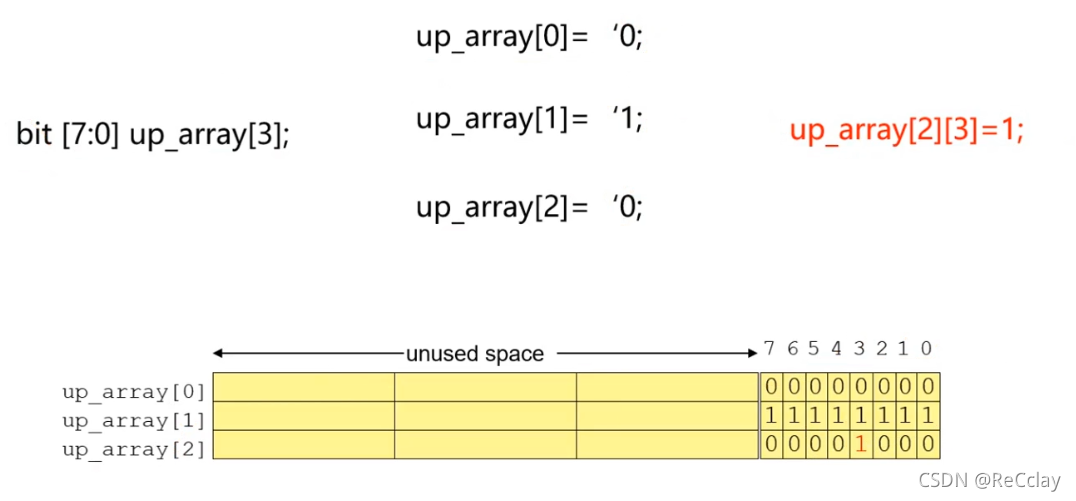

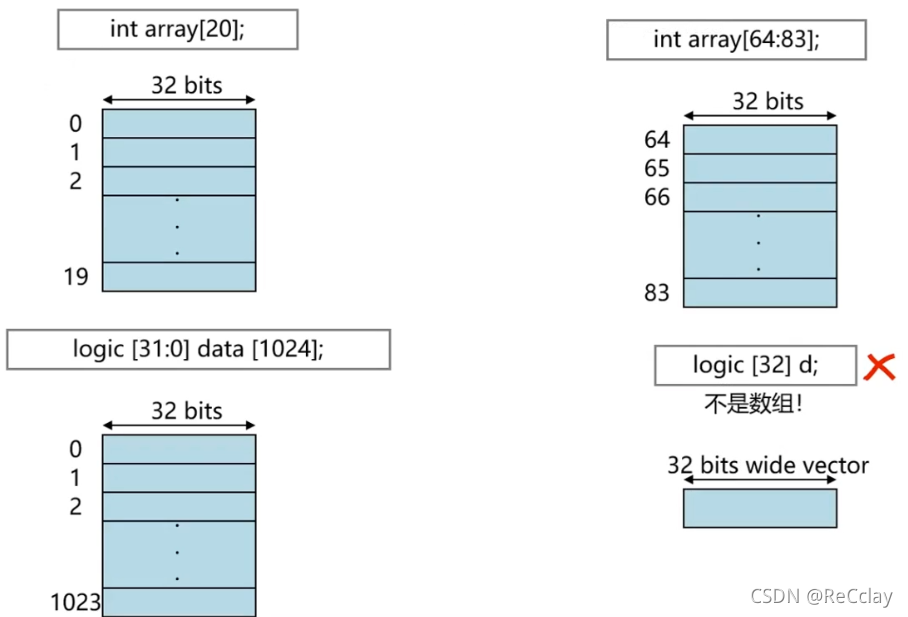

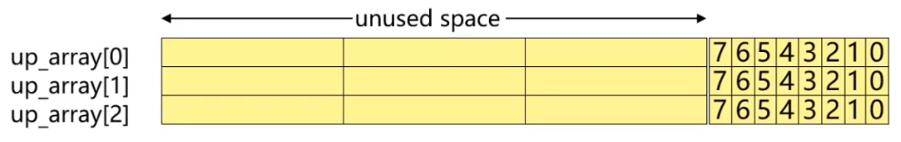

3.4、 Unfilled array (unpacked array)

- Store in 32 Bit storage unit

bit [7:0] up_array[3]Approximately equivalent tobyte up_array[3]( But pay attention to bit It's unsigned ,byte It's symbolic )

Simple unfilled array declaration

- Note that the array directly defines the depth, such as

1024, So it's from0-1023; If you directly specify[64:83], So that is64-83

3.5、 Fill the array ( Compressed array ,Packed Array)

The difference from uncompressed arrays , Still Storage On !

- Treat an array as a value

- Continuous storage of data

- The writing format of dimension is

[msb:lsb]

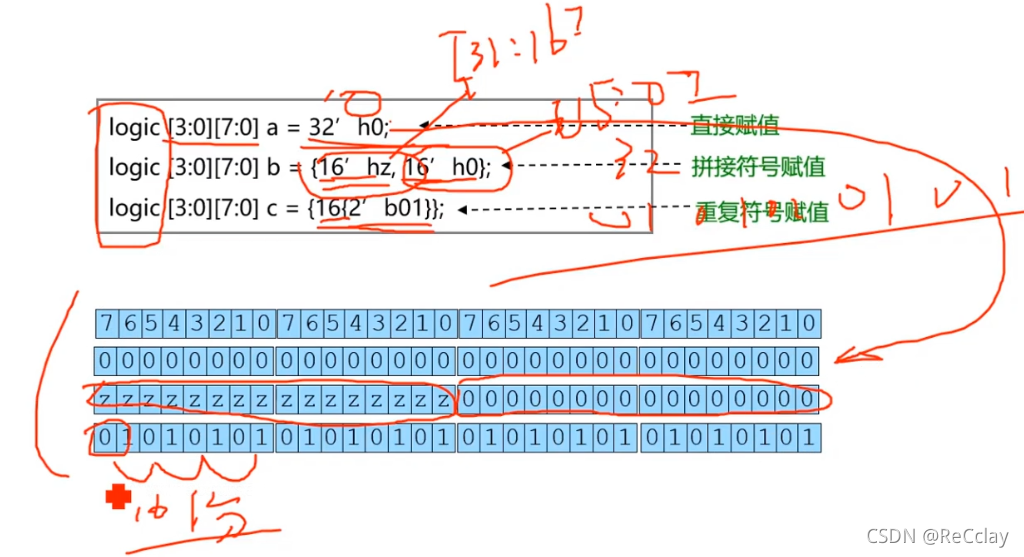

Initialization of filling array

- The declaration is initialized with a simple assignment statement

- Fill array initialization assignment There's no need to put single quotes !

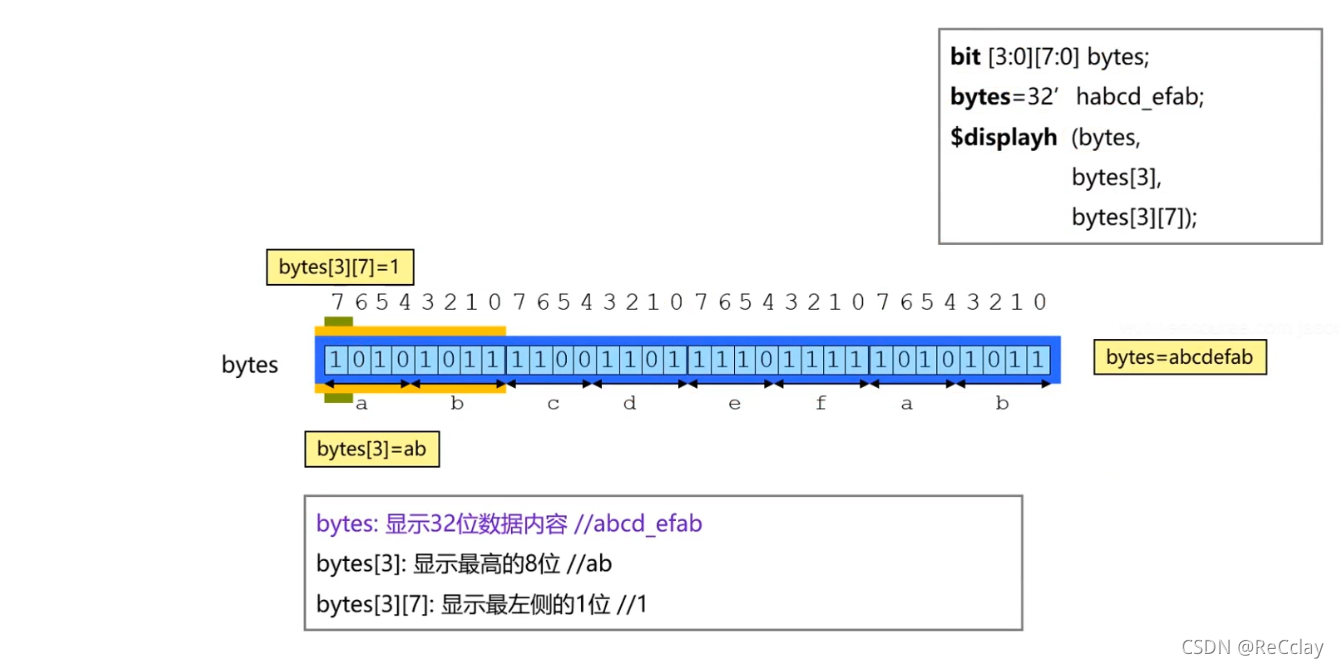

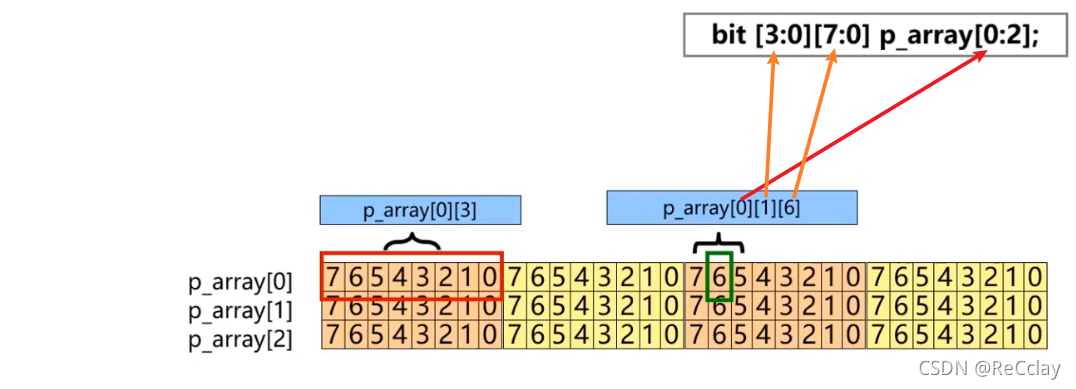

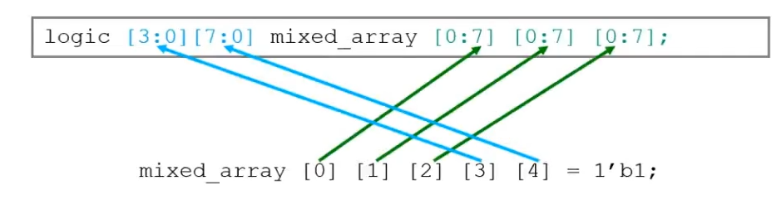

3.6、 Mixed array (Mixed Arrays)

3.6.1、 Introduction to mixed arrays

- p_array Is an unfilled array , Array elements are filled arrays :

bit [3:0][7:0] p_array[0:2]

- Review of unfilled arrays :

bit [7:0] up_array[3];

3.6.2、 Mixed array dimensions

- Mixed array , The dimension of the unfilled array is the first ; Start from the far left to the far right

- The dimension of the filled array is the second , Start from the left to the far right

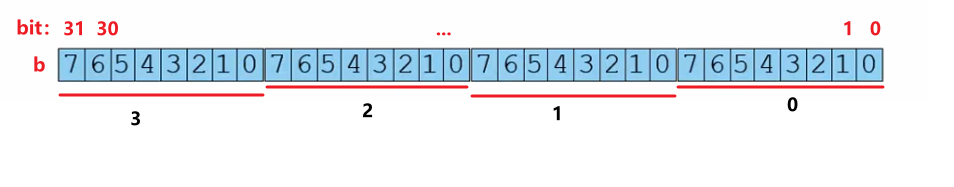

3.7、 Compare a filled array with an unfilled array

- Fill the array You can convert with scalar manually

bit [3:0][7:0] a;Andbit [31:0] b;They can be transformed into each other ! namely :a = b;orb = a;

- according to

byteReference memory data- A byte ,

8bit

- A byte ,

- If you need to wait for the array to change in the simulation , You can use to fill an array

- It's OK to use non filling , Filled vs. unfilled Smaller storage space , Faster simulation !

- Only Fixed arrays can be filled

- Fixed arrays are divided into filled and unfilled !

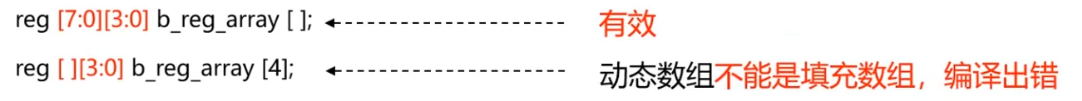

- The dynamic array 、 Associative arrays and queues cannot be filled

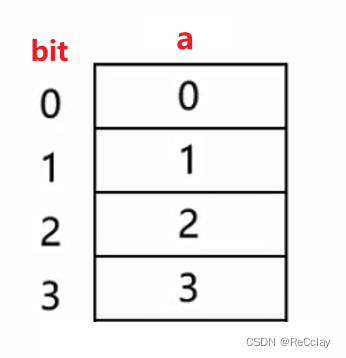

3.8、 Fill array and constant array initialization are compared with memory storage

Constant array :int a[4] = '{0, 1, 2, 3};

- Constant array initialization must Put single quotation marks in front

- Memory storage :

a[0] = 0; a[1] = 1; a[2] = 2; a[3] = 3;

Fill the array :bit [3:0] [7:0] b = {8'h3, 8'h2, 8'h1, 8'h0};

- Fill array initialization Unwanted Put single quotation marks in front

- Memory storage :

b[3] = 3; b[2]=2; b[1] = 1; b[0] = 0;

3.9、 Small test

Q: Variable logic and reg Is there a fundamental difference ?

- A: No,

Q: Variable logic and bit What's the difference ?

- A:logic There are four states :0/1/x/z;bit There are only two states :0/1

Q: Variables in two states can be used RTL Design ? Why? ?

- A: Can not be , Because binary logic will x/z The two circuit states are converted to 0

Q:

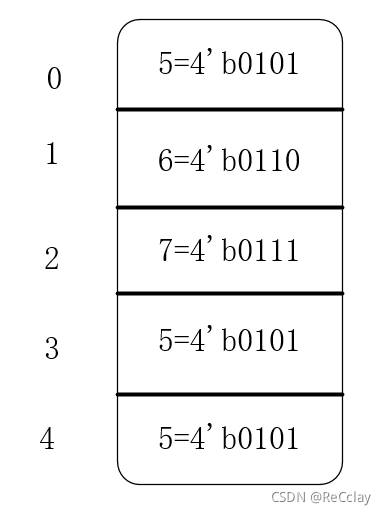

bit[31:0] src[5] = '{5,6,7,5,5}, besrc[1]= 3‘b110’src[3][0]= 1’b1src[2][3:1]= 3’b011

Q: Which of the following is not 2 Value data type ?(B)

- A bit

- B logic

- C int

- D byte

Q: Which of the following is not Verilog grammar ?(D)

- A data = '0;

- B data = 'z;

- C data = 'x;

- D data = '1;

int md[2][3];

foreach(md[i,j])

md[i,j] = 2*i+j;

- 1

- 2

- 3

- Q: Code above , that

md[2,3](A)- A 0

- B 5

- C 7

- D X

analysis :i The value range is :0-1,j The value range is :0-2.int Is a binary variable ,md[2,3] There is no doubt that it has crossed the line , So we should go back to 0, answer A. But if the definition is logic Four value variable , So what's back is x

- Q:logic[7:0] and byte The value ranges of are ?(A)

- A

0~255, -128~127 - B

-128~127, -128~127 - C

0~255, 0~255 - D

-128~127, 0~255

- A

logic It's unsigned ,byte It's symbolic

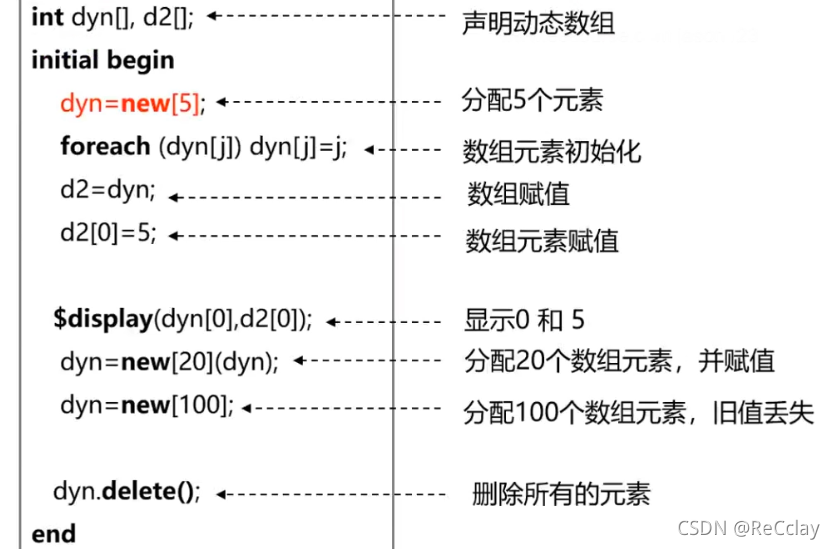

Four 、 The dynamic array

If you don't know the number of elements of the array before simulation , Then use dynamic arrays !

- Use square brackets when declaring dynamic arrays :

[], Form the following :

data_type name_of_dynamic_array[];

name_of_dynamic_array = new[number_of_elements];

- 1

- 2

- Set the number of elements of the array when running the simulation , Not at compile time

- In the simulation process , You can allocate memory space and reset the number of array elements

new[]Used to allocate memory space , Passing the number of array elements- The assignment of array can be realized through the name of array

- When the data type of the fixed array is the same , You can assign values to dynamic arrays

$sizeThe system function returns the number of elements of fixed array and dynamic array !( Fixed arrays can only be used$size, Dynamic arrays can be used$sizeandsize())

dyn = new[20](dyn)- The original element value is still saveddyn = new[100];- The original element value is lost

When the following conditions are met , Dynamic arrays and fixed numbers can be assigned to each other :

- Same data type

- The same number of elements

int a[10]; // Fixed array

int b[]; // The dynamic array

b = new[10]; // After this ,b and a You can assign values to each other, that is :a=b or b=a Fine !

- 1

- 2

- 3

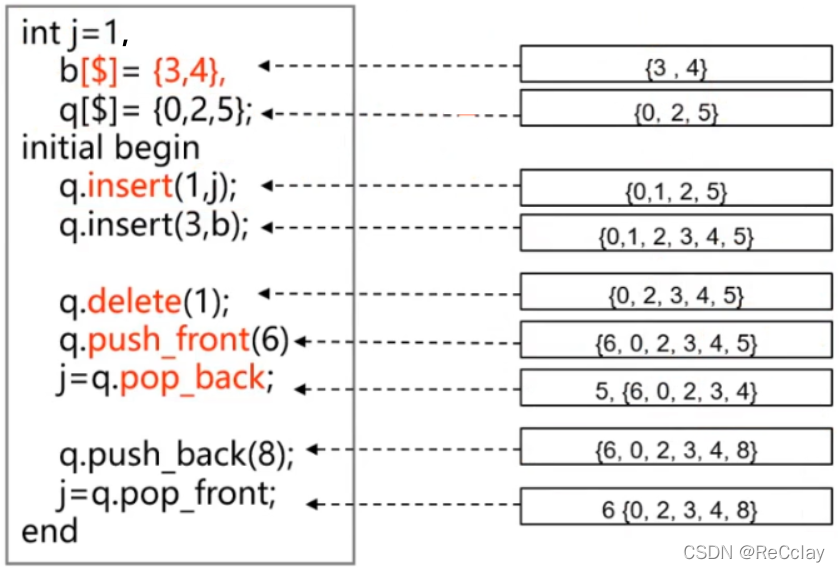

5、 ... and 、 queue ( With the more )

Queues combine the characteristics of arrays and linked lists . Queues are similar to linked lists , Sure Add or remove elements anywhere in a queue , The performance loss of such operations is much smaller than that of dynamic arrays , Because dynamic arrays need to allocate new arrays and copy the values of all elements . Queues are similar to arrays , You can access any element through the index , Instead of traversing all the elements before the target element like a linked list !

- Queue declaration uses

$In square brackets :data_type queue_name[$]; - have Sort and Search for The function of

- Allocate additional space and additional elements in sequence

- Support

pushandpopoperation - Support

addandremoveElement operation - Fixed array and The dynamic array The value of is assigned to queue

- Unwanted

new[]function - The queue element number is :

0To$- If you put

$To the left of a range expression , that$Will represent the minimum , for example[$:2]On behalf of[0:2]. Empathy , If placed on the right side of the expression , Represents the maximum .

- If you put

- The initialization of queue constants is the same as that of filling arrays ( Merge array ) equally No single quotation marks !

bandqandjCommon variable typesint, So they are separated by commas ! queue{3, 4}left 3 It's the team leader , On the right side 4 It's the end of the team !insert(x, y): In the x The value inserted before the position element is y The elements ofpush_front(x): stay Team head Insert value is x The elements of ;push_back(x): stay A party Insert value is x The elements of ;

pop_back: The tail element is out of the teampop_front: Team leader element out of the team

pushandpopOnly the head or tail of the team can be operated , Equivalent to one FIFO Behavior !delete(x): Delete the first x Location elements

The elements in the queue are Continuous storage Of , So it is very convenient to access data at the front or back of the queue . No matter how big the queue is , Such operation ( Access data before and after ) It takes the same time . Adding or deleting elements in the middle of the queue requires moving the existing data to make room . The time consumed by the corresponding operation will increase linearly with the size of the queue .

6、 ... and 、 Associative array ( Linked data )

SV Provides an associative array type , The element used to hold the sparse matrix , This means that when you address a very large address space ,SV Allocate space only for the elements that are actually written . Associative arrays can be stored in the form of trees or hash tables , But there is some extra cost . But when saving arrays with scattered index values , Such as 32 Bit address or 64 Data packets indexed by bit data , This extra cost is obviously acceptable !

- Associative array declarations use data types placed in square brackets ,

data_type associative_array_name[data_type] - Use sparse Of memory space

- Dynamic allocation , Discontinuous elements ( It's a bit like a linked list )

- A one-dimensional , You can use integers and strings as indexes .

notes : Joint array declarations can also be used

*In square brackets , But not recommended , Here is only for understanding !

Associative array operation

- Associative arrays can be used

foreachTo initialize - Read unallocated elements ,4 Value logical variable returns x,2 Value logical variable returns 0

- Support functions :

first,next,prev,delete,exists

More use of associative arrays , May refer to :

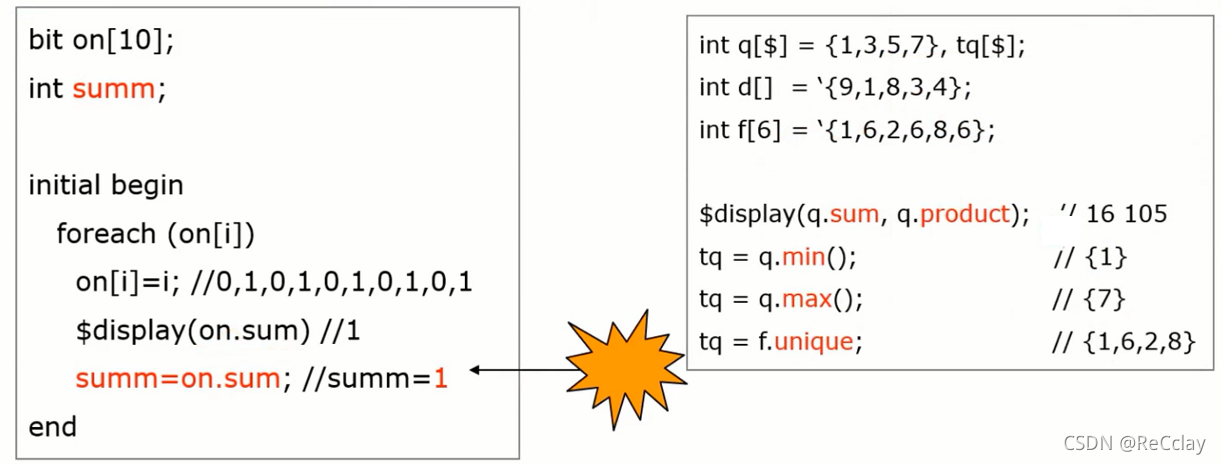

7、 ... and 、 Array methods ( Built in functions )

- Array decrement method ( For unfilled arrays : Fixed array 、 The dynamic array 、 Queues and associative arrays )

- Sum up

sum, quadratureproduct、 Andand、 oror、 Exclusive orxor a.sumSum of single bit array returns the value of single bit- This can explain why we should put

data_inDefined as33bit了 !

- This can explain why we should put

- For maximum

max, minimum valuemin, The only changeunique( duplicate removal )【 Be careful , Their return value is a queue 】

on.sumin sum The following brackets can be added or not

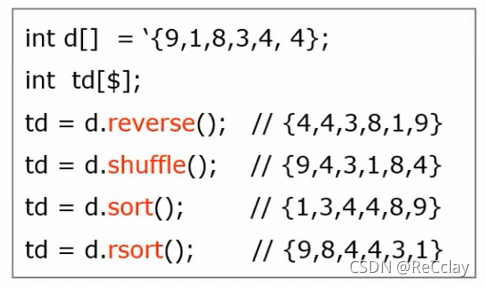

Array sort operation

- Flip :reverse

- Disorder :shuffle

- Ascending order :sort

- Descending order :rsort

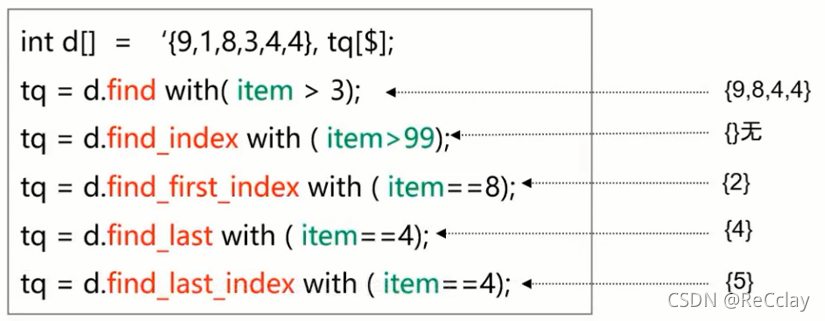

Array positioning operation

- Look for the element :find

- You can find someone A class Elements , Define the scope of this type of element , Namely characteristics

- Find the first element :find_first

- Find the index of the first element :find_first_with_index

- with and item It's all keywords ,item All elements !

- Pay attention to take index Is the return index !

- Pay attention to the initialization of dynamic array , It uses the initialization method of fixed array , This is OK !new It is used when the number of elements changes !

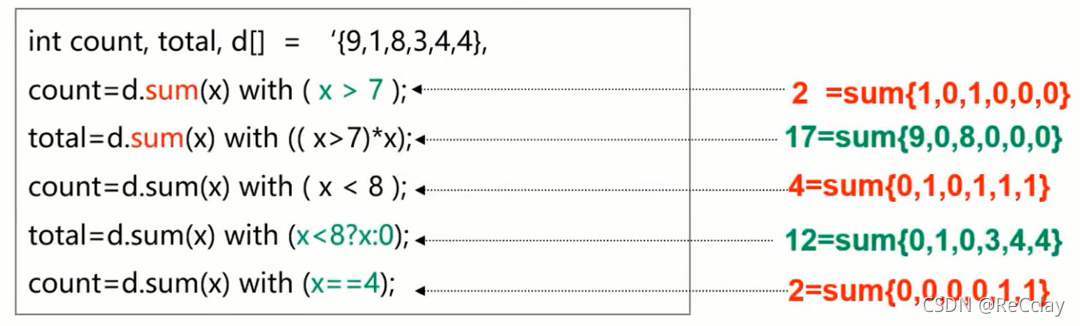

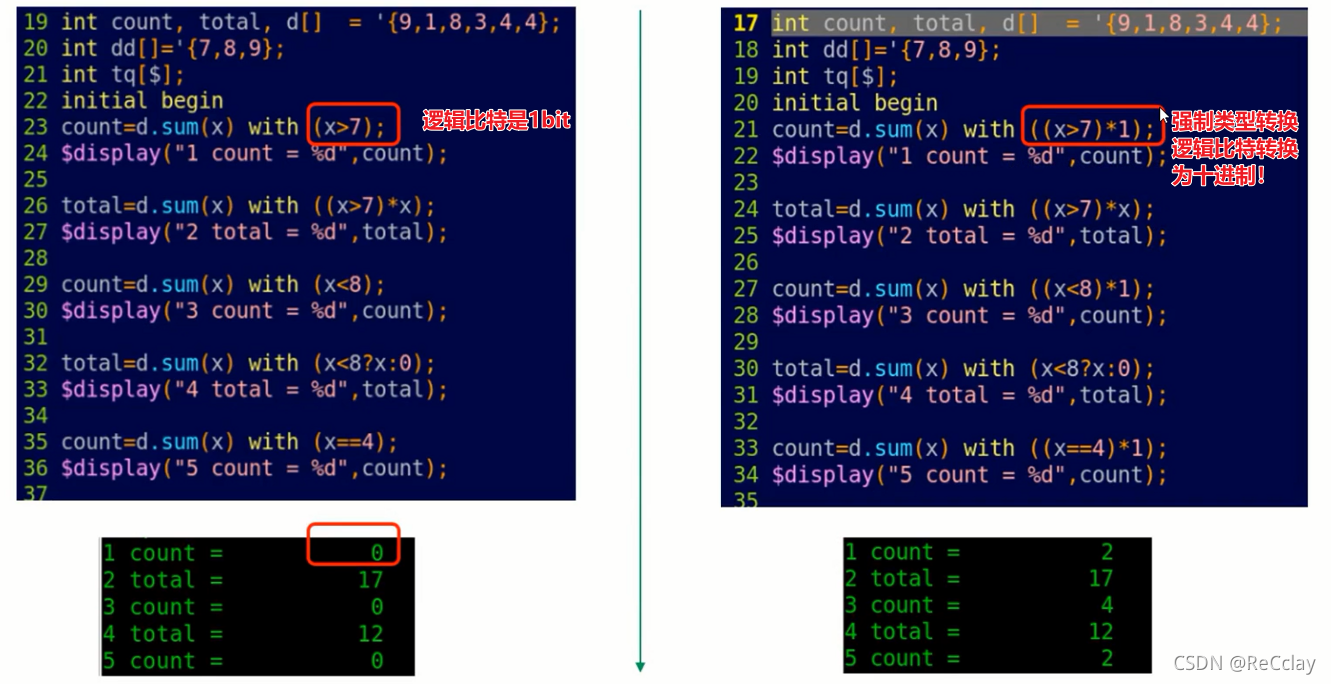

d.sum(x) with(x > 7)inx>7What is returned is a logical result , That is, the result is only 0 and 1 Two kinds of .

The above code practice

- You can see the first one

countIt should be printed out 2, Why is this 0 Well ?- Or what we said above :

with(x > 7)The logical result returned is single bit Of , and Sum of single bit array returns the value of single bit , So here is a mistake ! terms of settlement , Cast multiply it by 1, This 1 yes 32bit Of - summary : Only Simple logical operation Of , All need to be converted !

- Or what we said above :

8、 ... and 、 Array usage is recommended

Fixed array

- Compile time , The number of array elements is fixed

- Continuous storage of data ( Compared with associative arrays )

- Multidimensional arrays

The dynamic array

- Compile time , I don't know the number of array elements

- Continuous storage of data ( Compared with associative arrays )

queue

- FIFO/Stack

- Special dynamic array , Compared with dynamic array, it can realize the rapid deletion of elements , Unwanted

new()To update !

Associative array

- Sparse data and memory ( Storage is discontinuous )

- The index number can be an integer or a string

Nine 、 Structure

- The key word of the structure is :struct

- A structure is a set of variables or constants , It can be operated as a whole , You can also operate some of them

- Put together logically related signals , For example, bus protocol :

struct{

int a, b;

logic [7:0] opcode;

logic [23:0] address;

bit error;

}instruction_Word

- Use the name of the structure to manipulate the entire variable

<structure_name>.<variable_name>

instruction_Word.address =24'hF00000;

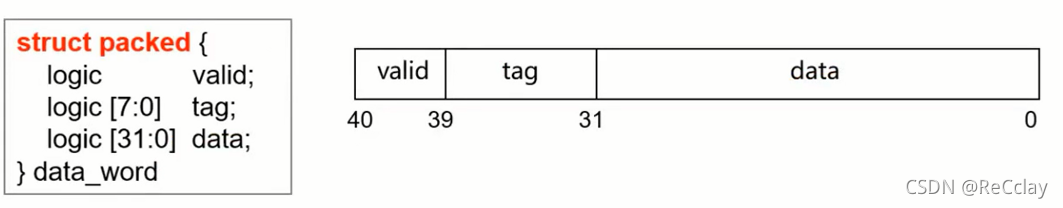

Fill structure

- Structure Default In this case Unfilled Of

- Different EDA The arrangement of tools is different

- Use keywords

packedThe structure can be Declare as filled The structure of the body- The filling structure stores all data elements in In a continuous unit

- Structure of the First element Is the right amount Leftmost field ( Different EDA The tools may be different !)

- The variables in the filled structure can be used through variable name or partial vector selection

data_word tag = 8'hf0; data_word [39:32] = 8'hf0;

- Fill structure operation

- Filling the structure assignment

data_word = '{1'b1, 8'hff, 32'd1024};

- 1

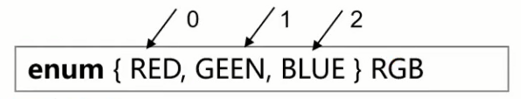

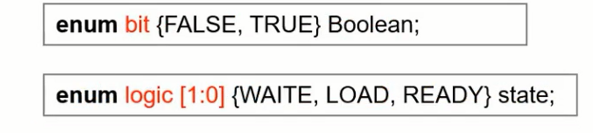

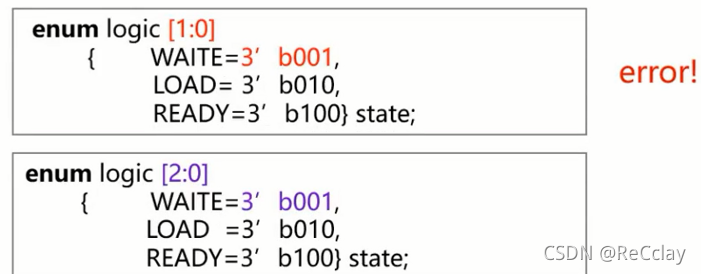

Ten 、 enumeration

- Abstract variables represent a numerical sequence

- Users can define each value

- Increased readability

- Support

first、last、next、prevoperation

enum {

RED,GREEN, BLUE} RGB

- 1

The default labels are :0 / 1 / 2

The default value of enumeration type is int

- The first value is

0, The second value is1, In turn, increasing

- The first value is

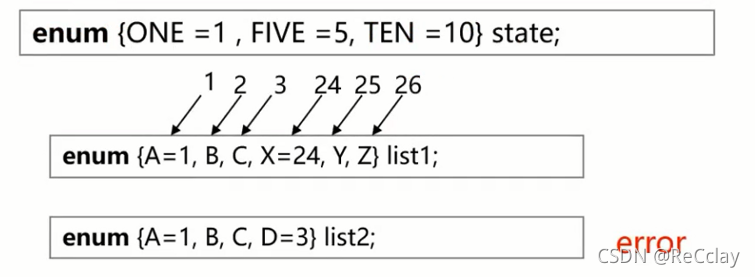

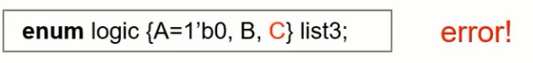

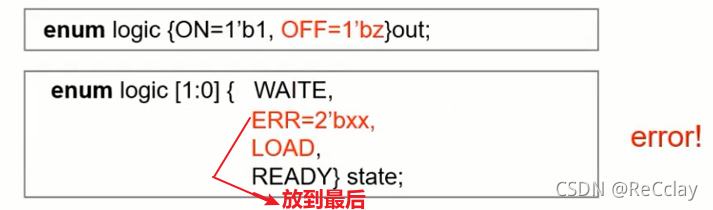

- SystemVerilog Support to explicitly specify each value

- All values must only

- For elements that do not specify a value , Its value is added according to the value of the previous element 1

- Enumerate the basic types of variables

- SystemVerilog Allow explicit specification of base types

- Enumerate variable values

- The value of the assigned variable must match the base type

- Numeric size of enumeration type

- Value range Cannot exceed the valid range of multiple base types ( The system will automatically determine the value range according to the defined variables !)

- Assign values to four valued logical variables X/Z It's legal.

- Must give x/z The next variable shows the assignment

11、 ... and 、 character string

string variable_name [=initial_value];The contents in brackets are optional , That is, the initial value is optional !- Without assignment ,string The value of the type variable is initialized to null characters

"" - System function

$psprintf()Generate string - String variable types have built-in operators and functions

==,!=,compare() and icompare();itoa(), atoi(), atohex(), toupper(), tolower()etc.len(), getc(), putc(), substr()

Twelve 、 Practice

12.1、bit/logic practice

12.1.1、 Initial value exercise of binary and quaternary variables

sv_bit_logic.sv

module sv_bit_logic();

logic [7:0] sig_logic;

bit [7:0] sig_bit;

byte sig_byte;

shortint sig_sint;

int sig_int;

longint sig_lint;

initial begin

$display("********************************initial value test********************************");

$display("**********************************************************************************");

$display("*************************4 state varialbe initial value***************************");

$display("***************Initial value of logic type signal sig_logic = %0b*****************", sig_logic);

$display("**********************************************************************************");

$display("**********************************************************************************");

$display("*************************2 state varialbe initial value***************************");

$display("***************Initial value of logic type signal sig_bit = %0b*****************", sig_bit);

$display("***************Initial value of logic type signal sig_byte = %0b*****************", sig_byte);

$display("***************Initial value of logic type signal sig_sint = %0b*****************", sig_sint);

$display("***************Initial value of logic type signal sig_int = %0b*****************", sig_int);

$display("***************Initial value of logic type signal sig_lint = %0b*****************", sig_lint);

$display("**********************************************************************************");

end

endmodule

Makefile

comp_file = ;

all: comp run log open

comp:

vcs -full64 -sverilog -debug_all -timescale=1ns/1ps $(comp_file) -l comp.log

run:

./simv -l $(comp_file).log

log:

sed '/^[^*].*/d' $(comp_file).log > rslt.log

open:

gvim rslt.log

clean:

sed '/^[^*].*/d' $(comp_file).log > rst.log: Regular expression , The function is the beginning, not the asterisk*Just delete it , After deletion, the remaining lines with asterisks are placed in the filerslt.ogin

Run the command as follows :

make comp_file=sv_bit_logic.sv

- 1

rslt.log

********************************initial value test********************************

**********************************************************************************

*************************4 state varialbe initial value***************************

***************Initial value of logic type signal sig_logic = xxxxxxxx*****************

**********************************************************************************

**********************************************************************************

*************************2 state varialbe initial value***************************

***************Initial value of logic type signal sig_bit = 0*****************

***************Initial value of logic type signal sig_byte = 0*****************

***************Initial value of logic type signal sig_sint = 0*****************

***************Initial value of logic type signal sig_int = 0*****************

***************Initial value of logic type signal sig_lint = 0*****************

**********************************************************************************

sig_logicIt's an eight digit four valued variable , So what's printed out is 8 individualx- Others are binary variables , The default initial value is

0

12.1.2、$isunknown practice

stay sv_bit_logic.sv Add the relevant code in :

...

$display("********************************$isunknown() test ********************************");

if($isunknown(sig_logic) == 1) begin

$display("***************Initial value of sig_logic is X*****************");

end

else begin

$display("***************Initial value of sig_logic is not X*****************");

end

if($isunknown(sig_bit) == 1) begin

$display("***************Initial value of sig_bit is X*****************");

end

else begin

$display("***************Initial value of sig_bit is not X*****************");

end

...

... ********************************$isunknown() test ******************************** ***************Initial value of sig_logic is X***************** ***************Initial value of sig_bit is not X*****************12.1.3、 Unsigned and signed number exercises

stay

sv_bit_logic.svAdd the relevant code in :... $display("********************************signed & unsigned test ********************************"); sig_logic = 8'b1000_1010; sig_bit = 8'b1000_1010; sig_byte = 8'b1000_1010; $display("***************sig_logic(8'b1000_1010) = %0d*****************", sig_logic); $display("***************sig_bit (8'b1000_1010) = %0d*****************", sig_bit ); $display("***************sig_byte (8'b1000_1010) = %0d*****************", sig_byte ); ...

rslt.log... ********************************signed & unsigned test ******************************** ***************sig_logic(8'b1000_1010) = 138***************** ***************sig_bit (8'b1000_1010) = 138***************** ***************sig_byte (8'b1000_1010) = -118*****************

bit/logicOf The bit width is user-defined Of , And is An unsigned number ;byte/shortint/int/longintOf The bit width is fixed Of , And is Signed number !

12.1.4、 whole 0/1/x/z Assignment exercise

stay sv_bit_logic.sv Add the relevant code in :

... $display("********************************all zeros, one test********************************"); sig_logic = '0; $display("***************sig_logic = '0 is %0b*****************", sig_logic); sig_logic = '1; $display("***************sig_logic = '1 is %0b*****************", sig_logic); sig_logic = 'x; $display("***************sig_logic = 'x is %0b*****************", sig_logic); sig_logic = 'z; $display("***************sig_logic = 'z is %0b*****************", sig_logic); ...

rslt.log... ********************************all zeros, one test******************************** ***************sig_logic = '0 is 0***************** ***************sig_logic = '1 is 11111111***************** ***************sig_logic = 'x is xxxxxxxx***************** ***************sig_logic = 'z is zzzzzzzz*****************

- 0 A few don't matter , Anyway, it's all 0, So the print here is correct !

12.2、 Fixed array exercise

12.2.1、unpacked array ininial demo( Unfilled array initialization demo)

sv_fix_array.sv

module sv_fix_array();

int src[5];

int dst[5];

logic [31:0] src_logic[5] = '{

5{

2}};

bit [3:0][7:0] packed_src;

initial begin

$display("**************************************************");

$display("*************unpacked array ininial demo**********");

$display("****size of src[5] is : %0d*********************", $size(src));

$display("****size of dst[5] is : %0d*********************", $size(dst));

foreach(src[i]) begin

src[i] = i;

$display("****src[%0d] = %0d*********************", i, src[i]);

end

foreach(dst[i]) begin

dst[i] = 5-i;

$display("****dst[%0d] = %0d*********************", i, dst[i]);

end

if( src == dst ) begin

$display("*********src == dst********");

end

else begin

$display("*********src != dst********");

foreach(src[i]) begin

$display("***src[%0d] = %1d, dst[%0d] = %1d***", i, src[i], i, dst[i]);

end

end

$display("**************************************************");

end

endmodule

MakefileSame as5.1, Copy it directly . Run the command as follows :make comp_file=sv_fix_array.sv

rslt.log

************************************************** *************unpacked array ininial demo********** ****size of src[5] is : 5********************* ****size of dst[5] is : 5********************* ****src[0] = 0********************* ****src[1] = 1********************* ****src[2] = 2********************* ****src[3] = 3********************* ****src[4] = 4********************* ****dst[0] = 5********************* ****dst[1] = 4********************* ****dst[2] = 3********************* ****dst[3] = 2********************* ****dst[4] = 1********************* *********src != dst******** ***src[0] = 0, dst[0] = 5*** ***src[1] = 1, dst[1] = 4*** ***src[2] = 2, dst[2] = 3*** ***src[3] = 3, dst[3] = 2*** ***src[4] = 4, dst[4] = 1*** **************************************************12.2.2、unpacked array assignment demo( Unfilled array assignment demo)

stay

sv_fix_array.svAdd the relevant code in :... $display("*************unpacked array assignment demo**********"); dst = src; $display("*************after dst = src**********"); foreach(src[i]) begin $display("***src[%0d] = %1d, dst[%0d] = %1d***", i, src[i], i, dst[i]); end src[0] = 5; $display("*************after src[0] = 5**********"); foreach(src[i]) begin $display("***src[%0d] = %1d, dst[%0d] = %1d***", i, src[i], i, dst[i]); end if( src[1:4] == dst[1:4] ) begin $display("*********src == dst********"); end else begin $display("*********src != dst********"); foreach(src[i]) begin $display("***src[%0d] = %1d, dst[%0d] = %1d***", i, src[i], i, dst[i]); end ...

rslt.log*************unpacked array assignment demo********** *************after dst = src********** ***src[0] = 0, dst[0] = 0*** ***src[1] = 1, dst[1] = 1*** ***src[2] = 2, dst[2] = 2*** ***src[3] = 3, dst[3] = 3*** ***src[4] = 4, dst[4] = 4*** *************after src[0] = 5********** ***src[0] = 5, dst[0] = 0*** ***src[1] = 1, dst[1] = 1*** ***src[2] = 2, dst[2] = 2*** ***src[3] = 3, dst[3] = 3*** ***src[4] = 4, dst[4] = 4*** *********src == dst********12.2.3、unpacked array partial assign demo( Partial assignment of unfilled array demo)

stay

sv_fix_array.svAdd the relevant code in :$display("**************************************************"); $display("*************unpacked array partial assign demo**********"); src = '{ 5{ 5}}; foreach(src[i]) begin $display("***src[%0d] = %1d ***", i, src[i]); end $display("***src[0] = %0b ***", src[0]); $display("***src[0][0] = %0b ***", src[0][0]); $display("***src[2][2:1] = %0b ***",src[2][2:1]);

rslt.log************************************************** *************unpacked array partial assign demo********** ***src[0] = 5 *** ***src[1] = 5 *** ***src[2] = 5 *** ***src[3] = 5 *** ***src[4] = 5 *** ***src[0] = 101 *** ***src[0][0] = 1 *** ***src[2][2:1] = 10 ***12.2.4、array over read demo( Array read out of bounds demo)

stay

sv_fix_array.svAdd the relevant code in :... logic [31:0] src_logic[5] = '{ 5{ 2}}; ... $display("*************array over read demo**********"); $display("***over read int type src[10] = %0b ***", src[10]); $display("***over read logic src_logic[10] = %0b ***", src_logic[10]); ...

rslt.log*************array over read demo********** ***over read int type src[10] = 0 *** ***over read logic src_logic[10] = xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx ***

- 1

- 2

- 3

- The binary variable out of bounds is

0state - Note that the out of bounds of the four valued variable is

xstate , And it is the corresponding digitx. Here, src_logic yes 32 position , So it is 32 individualx

12.2.5、packed array assign demo( Fill array assignment demo)

stay sv_fix_array.sv Add the relevant code in :

$display("*************packed array assign demo**********");

packed_src = {

8'h3, 8'h2, 8'h1, 8'h0};

foreach(packed_src[i]) begin

$display("***packed_src[%0d] = %1d ***", i, packed_src[i]);

end

rslt.log

*************packed array assign demo**********

***packed_src[3] = 3 ***

***packed_src[2] = 2 ***

***packed_src[1] = 1 ***

***packed_src[0] = 0 ***

- Fill the array with assignment braces without adding

' - Note that the index of the filled array is from right to left , On the right is

0.

12.3、 Dynamic array exercise

12.3.1、dynamic array initial demo( Dynamic array initialization demo)

sv_dyn_array.sv

module sv_dyn_array();

int dyn1[];

int dyn2[];

initial begin

$display("***dynamic array initial demo***");

$display("***Before dyn1=new[5], size of dyn1 is : %0d ***", $size(dyn1));

dyn1 = new[5];

$display("***After dyn1=new[5], size of dyn1 is : %0d ***", $size(dyn1));

foreach(dyn1[i]) begin

dyn1[i] = i;

$display("****** dyn1[%0d]=%0d", i, dyn1[i]);

end

end

endmodule

rslt.log

***dynamic array initial demo***

***Before dyn1=new[5], size of dyn1 is : 0 ***

***After dyn1=new[5], size of dyn1 is : 5 ***

****** dyn1[0]=0

****** dyn1[1]=1

****** dyn1[2]=2

****** dyn1[3]=3

****** dyn1[4]=4

- Makefile Same as before , But is

comp_fileParameters changed :make comp_file=sv_dyn_array.sv

12.3.2、dynamic array assignment demo( Dynamic array assignment demo)

sv_dyn_array.sv

$display("***dynamic array initial demo***");

dyn2 = dyn1;

dyn2[0] = 5;

$display("***After dyn2=dyn1 & dyn2[0]=5***");

foreach(dyn2[i]) begin

$display("****** dyn1[%0d]=%0d, dyn2[%0d]=%0d", i, dyn1[i], i, dyn1[i]);

end

dyn1=new[20](dyn1);

$display("******After dyn1=new[20](dyn1)******");

foreach(dyn1[i]) begin

$display("****** dyn1[%0d]=%0d", i, dyn1[i]);

end

dyn1=new[10];

$display("******After dyn1=new[10]******");

foreach(dyn1[i]) begin

$display("****** dyn1[%0d]=%0d", i, dyn1[i]);

end

rslt.log

***dynamic array initial demo***

***After dyn2=dyn1 & dyn2[0]=5***

****** dyn1[0]=0, dyn2[0]=0

****** dyn1[1]=1, dyn2[1]=1

****** dyn1[2]=2, dyn2[2]=2

****** dyn1[3]=3, dyn2[3]=3

****** dyn1[4]=4, dyn2[4]=4

******After dyn1=new[20](dyn1)******

****** dyn1[0]=0

****** dyn1[1]=1

****** dyn1[2]=2

****** dyn1[3]=3

****** dyn1[4]=4

****** dyn1[5]=0

****** dyn1[6]=0

****** dyn1[7]=0

****** dyn1[8]=0

****** dyn1[9]=0

****** dyn1[10]=0

****** dyn1[11]=0

****** dyn1[12]=0

****** dyn1[13]=0

****** dyn1[14]=0

****** dyn1[15]=0

****** dyn1[16]=0

****** dyn1[17]=0

****** dyn1[18]=0

****** dyn1[19]=0

******After dyn1=new[10]******

****** dyn1[0]=0

****** dyn1[1]=0

****** dyn1[2]=0

****** dyn1[3]=0

****** dyn1[4]=0

****** dyn1[5]=0

****** dyn1[6]=0

****** dyn1[7]=0

****** dyn1[8]=0

****** dyn1[9]=0

dyn1=new[20](dyn1)Assigned ; anddyn1=new[10]Will overwrite the assigned !

12.3.3、dynamic array delete demo( Dynamic array deletion demo)

sv_dyn_array.sv

$display("***dynamic array delete demo***");

dyn1.delete();

$display("*******After dyn1.delete******");

d i s p l a y < / s p a n > < s p a n c l a s s = " t o k e n p u n c t u a t i o n " > ( < / s p a n > < s p a n c l a s s = " t o k e n s t r i n g " > " ∗ ∗ ∗ ∗ A f t e r d e l e t i o n , d y n 1 s i z e i s : display</span><span class="token punctuation">(</span><span class="token string">"****After deletion, dyn1 size is : %0d"</span>, <span class="token variable"> display</span><spanclass="tokenpunctuation">(</span><spanclass="tokenstring">"∗∗∗∗Afterdeletion,dyn1sizeis:size(dyn1));

foreach(dyn1[i]) begin

$display(“****** dyn1[%0d]=%0d”, i, dyn1[i]);

end

rslt.log

***dynamic array delete demo*** *******After dyn1.delete****** ****After deletion, dyn1 size is : 012.4、 Practice in line

12.4.1、 Queue built-in function demo( Yes bug)

sv_queue.sv

module sv_queue(); int q[$] = { 1, 3, 5, 7}; int tq[$]; int d[$] = '{9, 1, 8, 3, 4, 4}; int f[$] = '{ 1, 6, 2, 6, 8, 6}; initial begin foreach(q[i]) begin $display("******q[%0d] = %0d******", i, q[i]); end $display("******summation of q{1, 3, 5, 7} = %0d, ******", q.sum); $display("******product of q{1, 3, 5, 7} = %0d, ******", q.product); $display("******minimum of q{1, 3, 5, 7} = %0d, ******", q.min); $display("******maximum of q{1, 3, 5, 7} = %0d, ******", q.max); tq = f.unique; foreach(tq[i]) begin $display("******unique of queue f{1,6,2,6,8,6}[%0d] = %0d******", i, tq[i]); end end endmodule

rslt.sv******q[0] = 1****** ******q[1] = 3****** ******q[2] = 5****** ******q[3] = 7****** ******summation of q{ 1, 3, 5, 7} = 16, ****** ******product of q{ 1, 3, 5, 7} = 105, ****** ******minimum of q{ 1, 3, 5, 7} = -1207817664, ****** ******maximum of q{ 1, 3, 5, 7} = -1207816928, ****** ******unique of queue f{ 1,6,2,6,8,6}[0] = 1****** ******unique of queue f{ 1,6,2,6,8,6}[1] = 6****** ******unique of queue f{ 1,6,2,6,8,6}[2] = 2****** ******unique of queue f{ 1,6,2,6,8,6}[3] = 8******doubt : Why? max and min The printed value is wrong ?

- Makefile Same as before , But is

comp_fileParameters changed :make comp_file=sv_queue.sv - Grammar requires , For queues , need

'initialization , But now the tools are more powerful , It doesn't matter if you don't add it !

12.4.2、 Queue insert delete demo

sv_queue.sv

$display("******Queue operation demo******"); q.insert(1, 2); $display("***q{1,3,5,7} after q.insert(1,2) becomes : {%0d,%0d,%0d,%0d,%0d}******", q[0],q[1],q[2],q[3],q[4]); q.insert(3, 4); $display("***q{1,2,3,5,7} after q.insert(3,4) becomes : {%0d,%0d,%0d,%0d,%0d,%0d}******",q[0],q[1],q[2],q[3],q[4],q[5]); q.insert(5, 6); $display("***q{1,2,3,4,5,7} after q.insert(5,6) becomes : {%0d,%0d,%0d,%0d,%0d,%0d,%0d}******",q[0],q[1],q[2],q[3],q[4],q[5],q[6]); q.delete(5); $display("***q{1,2,3,4.5,6,7} after q.delete(5) becomes : {%0d,%0d,%0d,%0d,%0d,%0d}******",q[0],q[1],q[2],q[3],q[4],q[5]); q.delete(3); $display("***q{1,2,3,4,5,7} after q.delete(3) becomes : {%0d,%0d,%0d,%0d,%0d}******",q[0],q[1],q[2],q[3],q[4]); q.delete(1); $display("***q{1,2,3,5,7} after q.delete(1) becomes : {%0d,%0d,%0d,%0d}******",q[0],q[1],q[2],q[3]);******Queue operation demo****** ***q{ 1,3,5,7} after q.insert(1,2) becomes : { 1,2,3,5,7}****** ***q{ 1,2,3,5,7} after q.insert(3,4) becomes : { 1,2,3,4,5,7}****** ***q{ 1,2,3,4,5,7} after q.insert(5,6) becomes : { 1,2,3,4,5,6,7}****** ***q{ 1,2,3,4.5,6,7} after q.delete(5) becomes : { 1,2,3,4,5,7}****** ***q{ 1,2,3,4,5,7} after q.delete(3) becomes : { 1,2,3,5,7}****** ***q{ 1,2,3,5,7} after q.delete(1) becomes : { 1,3,5,7}******12.4.3、 Join the team and leave the team demo

sv_queue.sv$display("*******************************"); for(int i=0; i<4; i=i+1) begin $display("***q{1,3,5,7} the %0d times q.pop_front value %0d***", i, q.pop_front); end $display("******* After 4 times pop_front for q{1,3,5,7}******"); $display("***q[0]=%0d,q[1]=%0d,q[2]=%0d,q[3]=%0d***",q[0],q[1],q[2],q[3]); for(int i=0; i<4; i=i+1) begin q.push_back(2*i+1); $display("*** the %0d times q.push_back value %0d***", i, 2*i+1); end $display("******* After 4 times push_back(2*i+1) for q{} ******"); $display("***q[0]=%0d,q[1]=%0d,q[2]=%0d,q[3]=%0d***",q[0],q[1],q[2],q[3]);

rslt.sv******************************* ***q{ 1,3,5,7} the 0 times q.pop_front value 1*** ***q{ 1,3,5,7} the 1 times q.pop_front value 3*** ***q{ 1,3,5,7} the 2 times q.pop_front value 5*** ***q{ 1,3,5,7} the 3 times q.pop_front value 7*** ******* After 4 times pop_front for q{ 1,3,5,7}****** ***q[0]=0,q[1]=0,q[2]=0,q[3]=0*** *** the 0 times q.push_back value 1*** *** the 1 times q.push_back value 3*** *** the 2 times q.push_back value 5*** *** the 3 times q.push_back value 7*** ******* After 4 times push_back(2*i+1) for q{ } ****** ***q[0]=1,q[1]=3,q[2]=5,q[3]=7***12.5、 Array method practice

12.5.1、 Sum up 、 Quadrature method demo

sv_array_method.svmodule sv_array(); int on[6]; int td[6]; int dq[$]; int sum; int product; int x; initial begin $display("***array methods demo***"); foreach(on[i]) begin on[i] = i; $display("******on[%0d] = %0d", i, on[i]); end $display("*********on.sum=%0d*********", on.sum); $display("*********on.product=%0d*********", on.product); on.reverse(); $display("***on reverse : %0d, %0d, %0d, %0d, %0d, %0d***",on[0],on[1],on[2],on[3],on[4],on[5]); on.shuffle; $display("***on shuffle : %0d, %0d, %0d, %0d, %0d, %0d***",on[0],on[1],on[2],on[3],on[4],on[5]); on.sort; $display("***on sort : %0d, %0d, %0d, %0d, %0d, %0d***",on[0],on[1],on[2],on[3],on[4],on[5]); on.rsort; $display("***on rsort : %0d, %0d, %0d, %0d, %0d, %0d***",on[0],on[1],on[2],on[3],on[4],on[5]); end endmodule

- Makefile Same as before , But is

comp_fileParameters changed :make comp_file=sv_array_method.sv

rslt.log

***array methods demo*** ******on[0] = 0 ******on[1] = 1 ******on[2] = 2 ******on[3] = 3 ******on[4] = 4 ******on[5] = 5 *********on.sum=15********* *********on.product=0********* ***on reverse : 5, 4, 3, 2, 1, 0*** ***on shuffle : 3, 4, 2, 5, 0, 1*** ***on sort : 0, 1, 2, 3, 4, 5*** ***on rsort : 5, 4, 3, 2, 1, 0***12.5.2、 Queue to find an element or index method , Conditional summation demo

sv_array_method.sv$display("********************************"); dq=on.find(x) with (x>3); $display("***dp=on.find(x) with(x>3) dq: %0d, %0d, %0d, %0d, %0d, %0d***",dq[0],dq[1],dq[2],dq[3],dq[4],dq[5]); dq=on.find_index(x) with (x>3); $display("***dp=on.find_index(x) with(x>3) dq: %0d, %0d, %0d, %0d, %0d, %0d***",dq[0],dq[1],dq[2],dq[3],dq[4],dq[5]); sum=on.sum(x) with (x>3); $display("***sum=on.sum(x) with (x>3) sum : %0d", sum); sum=on.sum(x) with ((x>3) * 1); $display("***sum=on.sum(x) with ((x>3) * 1) sum : %0d", sum); sum=on.sum(x) with ((x>3) * x); $display("***sum=on.sum(x) with ((x>3) * x) sum : %0d", sum);

rslt.log******************************** ***dp=on.find(x) with(x>3) dq: 5, 4, 0, 0, 0, 0*** ***dp=on.find_index(x) with(x>3) dq: 0, 1, 0, 0, 0, 0*** ***sum=on.sum(x) with (x>3) sum : 0 ***sum=on.sum(x) with ((x>3) * 1) sum : 2 ***sum=on.sum(x) with ((x>3) * x) sum : 9

- 1

- 2

- 3

- 4

- 5

- 6

- 7

sum=on.sum(x) with (x>3)This kind of writing will only take the lowest result in the end 1 individual bit position ;- The top is larger than 3 Only 5 and 4, therefore

x>3Compare the last two 1. Two 1 Summation is 2, The corresponding binary is 0010, Because only take the lowest 1bit position , So here is 0. - If you want to put a few 1 The summation result of is shown , It would be

(x>3)*1,1 The default is 32bit Of , The end result is 32bit Of course. - Want to put

x>3Sum of numbers , It would be(x>3)*x

- The top is larger than 3 Only 5 and 4, therefore

Be careful

find_indexIt's corresponding tox>3The index of the value :0 1hinder 4 individual 0 It's invalid 0, You can contrastfindAs a result !

12.6、 Structure 、 Enumerate exercises

12.6.1、 Structure (unpacked struct) assignment demo

sv_struct_enum.sv

module

sv_struct_enum();

struct {

int height;

int weight;

logic [7:0] legs;

logic [7:0] hands;

logic [1:0] eyes;

logic noses;

} animal;

struct packed {

int height;

int weight;

logic [7:0] legs;

logic [7:0] hands;

logic [1:0] eyes;

logic noses;

} animal_packed;

enum {

IDLE, SFD, PREAMBLE, DATA, FCS, EFD} cur_st;

enum {

RED=1, GREEN, BULE} rgb;

initial begin

animal.height = 32'd132; animal.weight = 32'd200;

animal.legs = 8'd2; animal.hands = 2'd2;

animal.eyes = 2'd2; animal.noses = 1'd1;

$display("******@%0tns animal unpacked value *******", $time);

$display("******@%0tns height : %0d *******", $time, animal.height);

$display("******@%0tns weight : %0d *******", $time, animal.weight);

$display("******@%0tns legs : %0d *******", $time, animal.legs);

$display("******@%0tns hands : %0d *******", $time, animal.hands);

$display("******@%0tns eyes : %0d *******", $time, animal.eyes);

$display("******@%0tns noses : %0d *******", $time, animal.noses);

end

endmodule

rslt.log

******@0ns animal unpacked value *******

******@0ns height : 132 *******

******@0ns weight : 200 *******

******@0ns legs : 2 *******

******@0ns hands : 2 *******

******@0ns eyes : 2 *******

******@0ns noses : 1 *******

- Makefile Same as before , But is

comp_fileParameters changed :make comp_file=sv_struct_enum.sv

12.6.2、 Structure (packed struct) assignment demo

sv_struct_enum.sv

animal_packed = '{32'd132,32'd200,8'd2,8'd2,8'd2,1'd1};

#1

$display("******@%0tns animal packed value *******", $time);

$display("******@%0tns height : %0d *******", $time, animal_packed.height);

$display("******@%0tns weight : %0d *******", $time, animal_packed.weight);

$display("******@%0tns legs : %0d *******", $time, animal_packed.legs);

$display("******@%0tns hands : %0d *******", $time, animal_packed.hands);

$display("******@%0tns eyes : %0d *******", $time, animal_packed.eyes);

$display("******@%0tns noses : %0d *******", $time, animal_packed.noses);

rslt.log

******@1000ns animal packed value *******

******@1000ns height : 132 *******

******@1000ns weight : 200 *******

******@1000ns legs : 2 *******

******@1000ns hands : 2 *******

******@1000ns eyes : 2 *******

******@1000ns noses : 1 *******

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- Be careful

packed structThe assignment method is unique , Of course, it can also be usedunpacked structWhich assignment method ! - Attention is also needed

packed structYou need to add'

12.6.3、 Enumeration assignment demo

sv_struct_enum.sv

$display("******@%0tns Enumeration test *******", $time);

$display("******@%0tns cur_st Range {IDLE, SFD, PREAMBLE, DATA, FCS, EFD} *******", $time);

$display("******@%0tns Initial Value of cur_st : %s=%0d****", $time,cur_st,cur_st);

#5 cur_st = IDLE;

$display("******@%0tns Current Value of cur_st : %s=%0d****", $time,cur_st,cur_st);

#5 cur_st = SFD;

$display("******@%0tns Current Value of cur_st : %s=%0d****", $time,cur_st,cur_st);

#5 cur_st = 3;

$display("******@%0tns Current Value of cur_st : %s=%0d****", $time,cur_st,cur_st);

#5 rgb = RED;

d i s p l a y < / s p a n > < s p a n c l a s s = " t o k e n p u n c t u a t i o n " > ( < / s p a n > < s p a n c l a s s = " t o k e n s t r i n g " > " ∗ ∗ ∗ ∗ ∗ ∗ @ display</span><span class="token punctuation">(</span><span class="token string">"******@%0tns rgb Value of rgb : %s=%0d****"</span>, <span class="token variable"> display</span><spanclass="tokenpunctuation">(</span><spanclass="tokenstring">"∗∗∗∗∗∗@time,rgb,rgb);

#5 rgb = GREEN;

d i s p l a y < / s p a n > < s p a n c l a s s = " t o k e n p u n c t u a t i o n " > ( < / s p a n > < s p a n c l a s s = " t o k e n s t r i n g " > " ∗ ∗ ∗ ∗ ∗ ∗ @ display</span><span class="token punctuation">(</span><span class="token string">"******@%0tns rgb Value of rgb : %s=%0d****"</span>, <span class="token variable"> display</span><spanclass="tokenpunctuation">(</span><spanclass="tokenstring">"∗∗∗∗∗∗@time,rgb,rgb);

#5 rgb = 2;

d i s p l a y < / s p a n > < s p a n c l a s s = " t o k e n p u n c t u a t i o n " > ( < / s p a n > < s p a n c l a s s = " t o k e n s t r i n g " > " ∗ ∗ ∗ ∗ ∗ ∗ @ display</span><span class="token punctuation">(</span><span class="token string">"******@%0tns rgb Value of rgb : %s=%0d****"</span>, <span class="token variable"> display</span><spanclass="tokenpunctuation">(</span><spanclass="tokenstring">"∗∗∗∗∗∗@time,rgb,rgb);

- The type of enumeration element is string by default , If you directly assign integer compilation, there may be warning:

Warning-[ENUMASSIGN] Illegal assignment to enum variable. have access tocastMake a cast , namely :$cast(curs_st, 3)

rslt.log

******@1000ns Enumeration test *******

******@1000ns cur_st Range {

IDLE, SFD, PREAMBLE, DATA, FCS, EFD} *******

******@1000ns Initial Value of cur_st : IDLE=0****

******@6000ns Current Value of cur_st : IDLE=0****

******@11000ns Current Value of cur_st : SFD=1****

******@16000ns Current Value of cur_st : DATA=3****

******@21000ns rgb Value of rgb : RED=1****

******@26000ns rgb Value of rgb : GREEN=2****

******@31000ns rgb Value of rgb : GREEN=2****

12.7、 String practice

12.7.1、 String assignment demo

string.sv

module STRING();

string name;

string s =“now is the time”;

string old_s;

string a;

initial begin

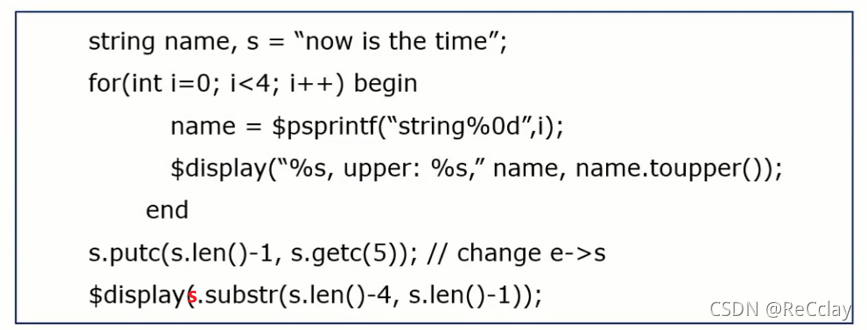

for<span class="token punctuation">(</span>int <span class="token assign-left variable">i</span><span class="token operator">=</span><span class="token number">0</span><span class="token punctuation">;</span> i<span class="token operator"><</span><span class="token number">4</span><span class="token punctuation">;</span> i++<span class="token punctuation">)</span> begin

name <span class="token operator">=</span> <span class="token variable">$psprintf</span><span class="token punctuation">(</span><span class="token string">"******string%0d"</span>, i<span class="token punctuation">)</span><span class="token punctuation">;</span>

<span class="token variable">$display</span><span class="token punctuation">(</span><span class="token string">"******%s, upper:%s"</span>, name, name.toupper<span class="token punctuation">(</span><span class="token punctuation">))</span><span class="token punctuation">;</span>

end

end

endmodule

- Makefile Same as before , But is

comp_fileParameters changed :make comp_file=string.sv

rslt.log

************string0, upper:******STRING0

************string1, upper:******STRING1

************string2, upper:******STRING2

************string3, upper:******STRING3

- 1

- 2

- 3

- 4

- Be careful module Your name cannot be string, So it's capitalized here

12.7.2、 obtain 、 Write a single character in the string demo

string.sv

old_s = s; for(int i=0; i<s.len; i++) begin a = s.getc(i); $display("****** the %dth character in string (%s) is : %c", i, s, a); ends.putc<span class="token punctuation">(</span>s.len<span class="token punctuation">(</span><span class="token punctuation">)</span>-1, s.getc<span class="token punctuation">(</span><span class="token number">5</span><span class="token punctuation">))</span><span class="token punctuation">;</span> <span class="token variable">$display</span><span class="token punctuation">(</span><span class="token string">"******After s.putc(s.len()-1, s.getc(5))"</span><span class="token punctuation">)</span><span class="token punctuation">;</span> <span class="token variable">$display</span><span class="token punctuation">(</span><span class="token string">"******Old string : %s"</span>, old_s<span class="token punctuation">)</span><span class="token punctuation">;</span> <span class="token variable">$display</span><span class="token punctuation">(</span><span class="token string">"******new string : %s"</span>, s<span class="token punctuation">)</span><span class="token punctuation">;</span>

rslt.log

****** the 0th character in string (now is the time) is : n

****** the 1th character in string (now is the time) is : o

****** the 2th character in string (now is the time) is : w

****** the 3th character in string (now is the time) is :

****** the 4th character in string (now is the time) is : i

****** the 5th character in string (now is the time) is : s

****** the 6th character in string (now is the time) is :

****** the 7th character in string (now is the time) is : t

****** the 8th character in string (now is the time) is : h

****** the 9th character in string (now is the time) is : e

****** the 10th character in string (now is the time) is :

****** the 11th character in string (now is the time) is : t

****** the 12th character in string (now is the time) is : i

****** the 13th character in string (now is the time) is : m

****** the 14th character in string (now is the time) is : e

******After s.putc(s.len()-1, s.getc(5))

******Old string : now is the time

******new string : now is the tims

12.7.3、 Intercepts a portion of a string

string.sv

old_s = s;

s = s.substr(s.len()-4, s.len()-1);

$display("******After substring s.substr(s.len()-4, s.len()-1)");

$display("******old string : %s", old_s);

$display("******new string : %s", s);

rslt.log

******After substring s.substr(s.len()-4, s.len()-1)

******old string : now is the tims

******new string : tims

substrYou can also directly fill in the index value , Such ass.substr(1, 3)

边栏推荐

- 基于Pytorch 框架手动完成线性回归

- Who has docker to install MySQL locally?

- Merging binary trees by recursion

- 漏洞复现-easy_tornado

- 轻松上手Fluentd,结合 Rainbond 插件市场,日志收集更快捷

- 太真实了,原来自己一直没有富裕起来是有原因的

- 云原生存储解决方案Rook-Ceph与Rainbond结合的实践

- 【数字IC验证快速入门】12、SystemVerilog TestBench(SVTB)入门

- Recursive method to construct binary tree from preorder and inorder traversal sequence

- DNS server configuration

猜你喜欢

The simple problem of leetcode is to judge whether the number count of a number is equal to the value of the number

Myabtis_ Plus

【踩坑系列】uniapp之h5 跨域的问题

在 Rainbond 中一键安装高可用 Nacos 集群

Call pytorch API to complete linear regression

Vulnerability recurrence easy_ tornado

Es FAQ summary

让Livelink初始Pose与动捕演员一致

在Rainbond中实现数据库结构自动化升级

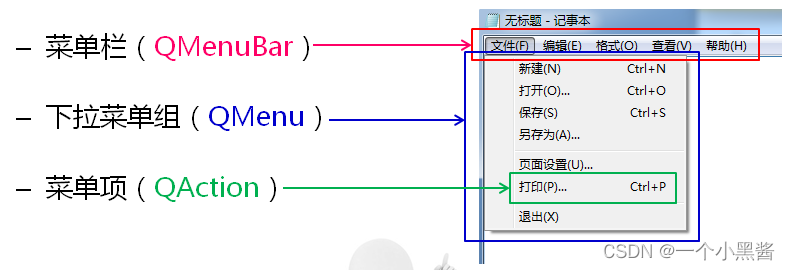

Main window in QT learning 27 application

随机推荐

Recursive construction of maximum binary tree

Implementation of replacement function of shell script

利用 Helm 在各类 Kubernetes 中安装 Rainbond

柯基数据通过Rainbond完成云原生改造,实现离线持续交付客户

解析创新教育体系中的创客教育

Rainbond 5.7.1 支持对接多家公有云和集群异常报警

Dedecms collects content without writing rules

【数字IC验证快速入门】14、SystemVerilog学习之基本语法1(数组、队列、结构体、枚举、字符串...内含实践练习)

Roulette chart 2 - writing of roulette chart code

[quick start of Digital IC Verification] 17. Basic grammar of SystemVerilog learning 4 (randomization)

快解析内网穿透助力外贸管理行业应对多种挑战

Introduction à l'objet blob

【數字IC驗證快速入門】15、SystemVerilog學習之基本語法2(操作符、類型轉換、循環、Task/Function...內含實踐練習)

Zsh shell adds automatic completion and syntax highlighting

Register of assembly language by Wang Shuang

Topic not received? Try this

Lua 编程学习笔记

【无标题】

Basic use of CTF web shrink template injection nmap

机器人教育在动手实践中的真理