当前位置:网站首页>06-SDRAM : SDRAM control module

06-SDRAM : SDRAM control module

2022-08-02 00:17:00 【Liu Yan son】

设计文件

// SDRAM控制模块

module sdram_ctrl(

input wire clk , //sdram时钟

input wire rst_n , //sdram复位信号

output wire init_end , //SDRAM 初始化完成标志

//SDRAM写端口

input wire sdram_wr_req , //写SDRAM请求信号

input wire [23:0] sdram_wr_addr , //SDRAM写操作的地址

input wire [9:0] wr_burst_len , //写sdram时数据突发长度

input wire [15:0] sdram_data_in , //写入SDRAM的数据

output wire sdram_wr_ack , //写SDRAM响应信号

//SDRAM读端口

input wire sdram_rd_req , //读SDRAM请求信号

input wire [23:0] sdram_rd_addr , //SDRAM读操作的地址

input wire [9:0] rd_burst_len , //读sdram时数据突发长度

output wire [15:0] sdram_data_out , //从SDRAM读出的数据

output wire sdram_rd_ack , //读SDRAM响应信号

//FPGA与SDRAM硬件接口

output wire sdram_cke , // SDRAM 时钟有效信号

output wire sdram_cs_n , // SDRAM 片选信号

output wire sdram_ras_n , // SDRAM 行地址选通

output wire sdram_cas_n , // SDRAM 列地址选通

output wire sdram_we_n , // SDRAM 写使能

output wire [1:0] sdram_bank , // SDRAM Bank地址

output wire [12:0] sdram_addr , // SDRAM 地址总线

inout wire [15:0] sdram_dq // SDRAM 数据总线

);

//==========================================parameter===========================================================

//==========================================reg=================================================================

//==========================================wire=================================================================

wire [3:0] init_cmd ; //初始化阶段写入sdram的指令

wire [1:0] init_bank ; //初始化阶段Bank地址

wire [12:0] init_addr ; //初始化阶段地址数据,辅助预充电操作

//sdram_a_ref

wire atref_req ; //自动刷新请求

wire atref_end ; //自动刷新结束标志

wire [3:0] atref_cmd ; //自动刷新阶段写入sdram的指令

wire [1:0] atref_bank ; //自动刷新阶段Bank地址

wire [12:0] atref_addr ; //地址数据,辅助预充电操作

wire atref_en ; //自动刷新使能

//sdram_write

wire wr_en ; //写使能

wire wr_end ; //一次写结束信号

wire [3:0] wr_sdram_cmd ; //写阶段命令

wire [1:0] wr_sdram_bank ; //写数据阶段Bank地址

wire [12:0] wr_sdram_addr ; //写阶段数据地址

wire wr_sdram_en ; //SDRAM写使能

wire [15:0] wr_sdram_data ; //写入SDRAM的数据

//sdram_read

wire rd_en ; //读使能

wire rd_end ; //一次突发读结束

wire [3:0] rd_sdram_cmd ; //读数据阶段写入sdram的指令

wire [1:0] rd_sdram_bank ; //读阶段Bank地址

wire [12:0] rd_sdram_addr ; //读阶段数据地址

//==========================================assign=================================================================

//==========================================always=================================================================

//==========================================状态机=================================================================

//==========================================模块例化=================================================================

//------------- sdram_init_inst -------------

sdram_initial sdram_initial_inst

(

.clk (clk ), //系统时钟,频率100MHz

.rst_n (rst_n ), //复位信号,低电平有效

.init_cmd (init_cmd ), //初始化阶段写入sdram的指令

.init_bank (init_bank ), //初始化阶段Bank地址

.init_addr (init_addr ), //初始化阶段地址数据,辅助预充电操作

.init_end (init_end ) //初始化结束信号

);

//------------- sdram_arbit_inst -------------

sdram_arbit sdram_arbit_inst

(

.clk (clk ), //系统时钟

.rst_n (rst_n ), //复位信号

//sdram_init

.init_cmd (init_cmd ), //初始化阶段命令

.init_end (init_end ), //初始化结束标志

.init_bank (init_bank ), //初始化阶段Bank地址

.init_addr (init_addr ), //初始化阶段数据地址

//sdram_auto_ref

.auto_ref_req (atref_req ), //自刷新请求

.auto_ref_end (atref_end ), //自刷新结束

.auto_ref_cmd (atref_cmd ), //自刷新阶段命令

.auto_ref_bank (atref_bank ), //自动刷新阶段Bank地址

.auto_ref_addr (atref_addr ), //自刷新阶段数据地址

.aref_en (atref_en ), //自刷新使能

//sdram_write

.wr_req (sdram_wr_req ), //写数据请求

.wr_end (wr_end ), //一次写结束信号

.wr_en (wr_en ), //写数据使能

.write_cmd (wr_sdram_cmd ), //写阶段命令

.write_bank (wr_sdram_bank ), //写阶段Bank地址

.write_addr (wr_sdram_addr ), //写阶段数据地址

.wr_sdram_en (wr_sdram_en ), //写数据有效

.wr_sdram_data (wr_sdram_data ), //要写入sdram的数据

//sdram_read

.rd_req (sdram_rd_req ), //读数据请求

.rd_end (rd_end ), //一次读结束

.rd_en (rd_en ), //读数据使能

.read_cmd (rd_sdram_cmd ), //读阶段命令

.read_addr (rd_sdram_addr ), //读阶段数据地址

.read_bank (rd_sdram_bank ), //读阶段Bank地址

//SDRAM接口

.sdram_cke (sdram_cke ), //SDRAM时钟使能

.sdram_cs_n (sdram_cs_n ), //SDRAM片选信号

.sdram_ras_n (sdram_ras_n ), //SDRAM行地址选通

.sdram_cas_n (sdram_cas_n ), //SDRAM列地址选通

.sdram_we_n (sdram_we_n ), //SDRAM写使能

.sdram_bank (sdram_bank ), //SDRAM Bank地址

.sdram_addr (sdram_addr ), //SDRAM地址总线

.sdram_dq (sdram_dq ) //SDRAM数据总线

);

//------------- sdram_atref_inst -------------

sdram_auto_ref sdram_auto_ref_inst

(

.clk (clk ), //系统时钟,频率100MHz

.rst_n (rst_n ), //复位信号,低电平有效

.init_end (init_end ), //初始化结束信号

.auto_ref_en (atref_en ), //自动刷新使能

.auto_ref_req (atref_req ), //自动刷新请求

.auto_ref_cmd (atref_cmd ), //自动刷新阶段写入sdram的指令

.auto_ref_bank (atref_bank ), //自动刷新阶段Bank地址

.auto_ref_addr (atref_addr ), //地址数据,辅助预充电操作

.auto_ref_end (atref_end ) //自动刷新结束标志

);

//------------- sdram_write_inst -------------

sdram_write sdram_write_inst

(

.clk (clk ), //系统时钟,频率100MHz

.rst_n (rst_n ), //复位信号,低电平有效

.init_end (init_end ), //初始化结束信号

.wr_en (wr_en ), //写使能

.wr_addr (sdram_wr_addr ), //写SDRAM地址

.wr_data (sdram_data_in ), //待写入SDRAM的数据(写FIFO传入)

.wr_burst_len (wr_burst_len ), //写突发SDRAM字节数

.wr_ack (sdram_wr_ack ), //写SDRAM响应信号

.wr_end (wr_end ), //一次突发写结束

.write_cmd (wr_sdram_cmd ), //写数据阶段写入sdram的指令

.write_bank (wr_sdram_bank ), //写数据阶段Bank地址

.write_addr (wr_sdram_addr ), //地址数据,辅助预充电操作

.wr_sdram_en (wr_sdram_en ), //数据总线输出使能

.wr_sdram_data (wr_sdram_data ) //写入SDRAM的数据

);

//------------- sdram_read_inst -------------

sdram_read sdram_read_inst

(

.clk (clk ), //系统时钟,频率100MHz

.rst_n (rst_n ), //复位信号,低电平有效

.init_end (init_end ), //初始化结束信号

.rd_en (rd_en ), //读使能

.rd_addr (sdram_rd_addr ), //读SDRAM地址

.rd_data (sdram_dq ), //自SDRAM中读出的数据

.rd_burst_len (rd_burst_len ), //读突发SDRAM字节数

.rd_ack (sdram_rd_ack ), //读SDRAM响应信号

.rd_end (rd_end ), //一次突发读结束

.read_cmd (rd_sdram_cmd ), //读数据阶段写入sdram的指令

.read_bank (rd_sdram_bank ), //读数据阶段Bank地址

.read_addr (rd_sdram_addr ), //地址数据,辅助预充电操作

.rd_sdram_data (sdram_data_out ) //SDRAM读出的数据

);

endmodule

边栏推荐

- contentEditable属性

- 短视频SEO优化教程 自媒体SEO优化技巧方法

- JSP page指令errorPage属性起什么作用呢?

- 短视频SEO搜索运营获客系统功能介绍

- security CSRF Vulnerability Protection

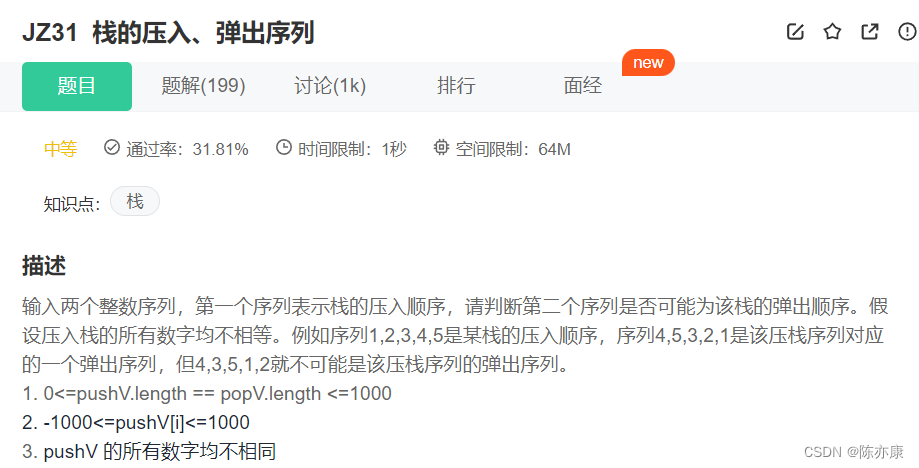

- Interview high-frequency test questions solution - stack push and pop sequence, effective parentheses, reverse Polish expression evaluation

- [Headline] Written test questions - minimum stack

- Is TCP reliable?Why?

- Win11如何获得最佳电源效率?

- 在CentOS下安装MySQL

猜你喜欢

Short video seo search optimization main content

带你搞懂MySQL隔离级别,两个事务同时操作同一行数据会怎样?

Short video SEO search operation customer acquisition system function introduction

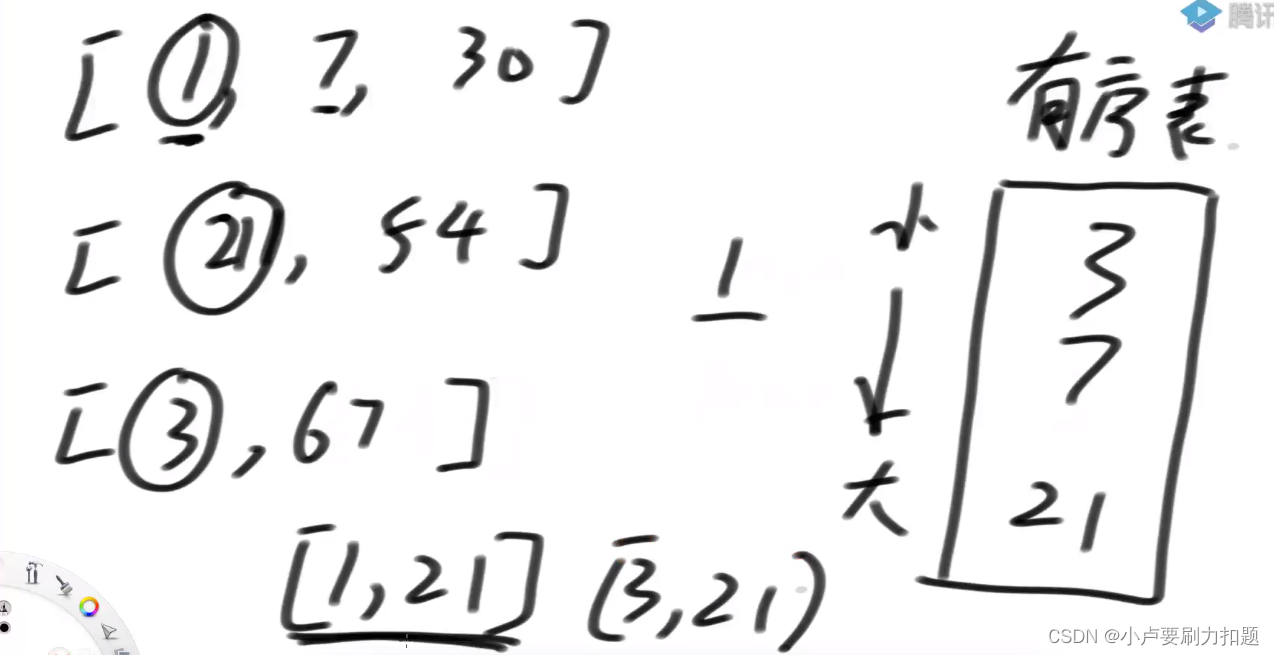

632. 最小区间

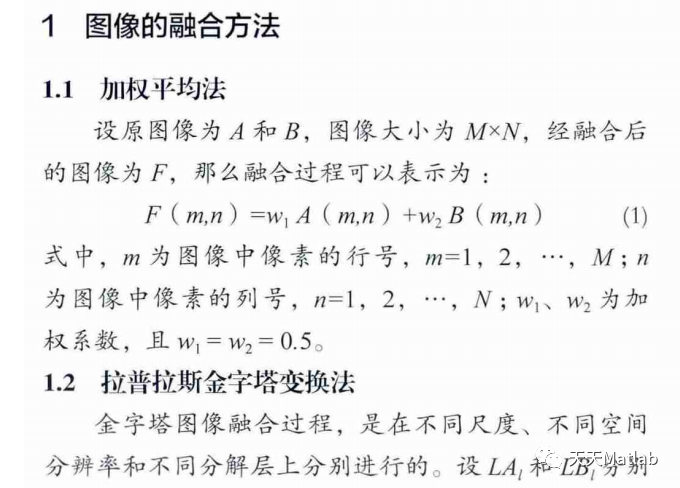

【图像融合】基于加权和金字塔实现图像融合附matlab代码

如何设计循环队列?快进来学习~

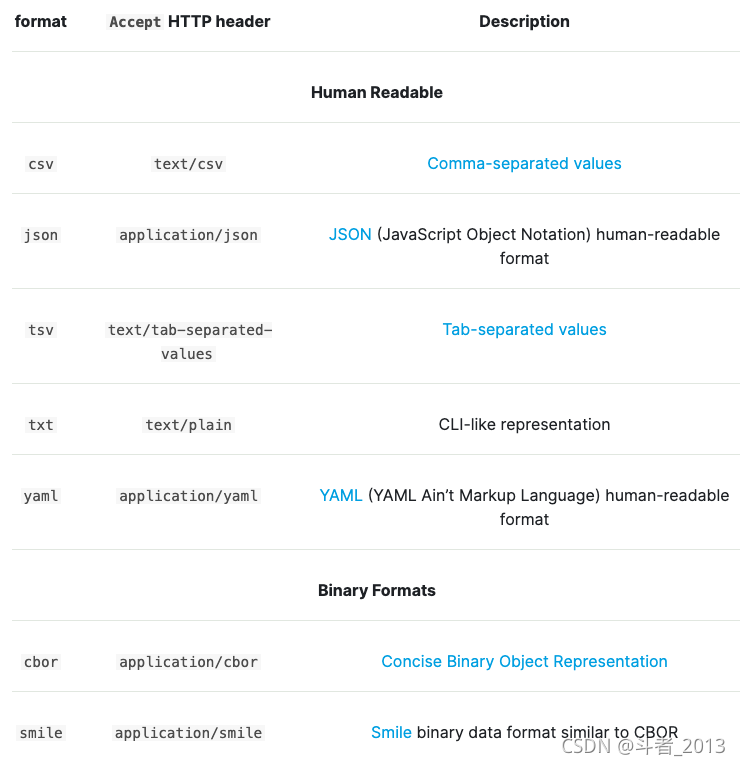

ES中SQL查询详解

Win11内存管理错误怎么办?

Interview high-frequency test questions solution - stack push and pop sequence, effective parentheses, reverse Polish expression evaluation

如何重装Win11?一键重装Win11方法

随机推荐

IP Core: FIFO

短视频SEO搜索运营获客系统功能介绍

async和await用法介绍

What is it like to trade for a living?

632. 最小区间

async/await 原理及执行顺序分析

mysql8安装make报错如何解决

信息系统项目管理师必背核心考点(五十七)知识管理工具

Short video SEO optimization tutorial Self-media SEO optimization skills and methods

contentEditable属性

GetHashCode方法与=

在MySQL登录时出现Access denied for user ‘root‘@‘localhost‘ (using password YES) 拒绝访问问题解决

WEB安全基础 - - - XRAY使用

短视频SEO优化教程 自媒体SEO优化技巧方法

QML包管理

当奈飞的NFT忘记了Web2的业务安全

【Leetcode】475. Heaters

06-SDRAM :SDRAM控制模块

如何设计循环队列?快进来学习~

电机原理动图合集