当前位置:网站首页>06-SDRAM :SDRAM控制模块

06-SDRAM :SDRAM控制模块

2022-08-01 23:59:00 【刘颜儿】

设计文件

// SDRAM控制模块

module sdram_ctrl(

input wire clk , //sdram时钟

input wire rst_n , //sdram复位信号

output wire init_end , //SDRAM 初始化完成标志

//SDRAM写端口

input wire sdram_wr_req , //写SDRAM请求信号

input wire [23:0] sdram_wr_addr , //SDRAM写操作的地址

input wire [9:0] wr_burst_len , //写sdram时数据突发长度

input wire [15:0] sdram_data_in , //写入SDRAM的数据

output wire sdram_wr_ack , //写SDRAM响应信号

//SDRAM读端口

input wire sdram_rd_req , //读SDRAM请求信号

input wire [23:0] sdram_rd_addr , //SDRAM读操作的地址

input wire [9:0] rd_burst_len , //读sdram时数据突发长度

output wire [15:0] sdram_data_out , //从SDRAM读出的数据

output wire sdram_rd_ack , //读SDRAM响应信号

//FPGA与SDRAM硬件接口

output wire sdram_cke , // SDRAM 时钟有效信号

output wire sdram_cs_n , // SDRAM 片选信号

output wire sdram_ras_n , // SDRAM 行地址选通

output wire sdram_cas_n , // SDRAM 列地址选通

output wire sdram_we_n , // SDRAM 写使能

output wire [1:0] sdram_bank , // SDRAM Bank地址

output wire [12:0] sdram_addr , // SDRAM 地址总线

inout wire [15:0] sdram_dq // SDRAM 数据总线

);

//==========================================parameter===========================================================

//==========================================reg=================================================================

//==========================================wire=================================================================

wire [3:0] init_cmd ; //初始化阶段写入sdram的指令

wire [1:0] init_bank ; //初始化阶段Bank地址

wire [12:0] init_addr ; //初始化阶段地址数据,辅助预充电操作

//sdram_a_ref

wire atref_req ; //自动刷新请求

wire atref_end ; //自动刷新结束标志

wire [3:0] atref_cmd ; //自动刷新阶段写入sdram的指令

wire [1:0] atref_bank ; //自动刷新阶段Bank地址

wire [12:0] atref_addr ; //地址数据,辅助预充电操作

wire atref_en ; //自动刷新使能

//sdram_write

wire wr_en ; //写使能

wire wr_end ; //一次写结束信号

wire [3:0] wr_sdram_cmd ; //写阶段命令

wire [1:0] wr_sdram_bank ; //写数据阶段Bank地址

wire [12:0] wr_sdram_addr ; //写阶段数据地址

wire wr_sdram_en ; //SDRAM写使能

wire [15:0] wr_sdram_data ; //写入SDRAM的数据

//sdram_read

wire rd_en ; //读使能

wire rd_end ; //一次突发读结束

wire [3:0] rd_sdram_cmd ; //读数据阶段写入sdram的指令

wire [1:0] rd_sdram_bank ; //读阶段Bank地址

wire [12:0] rd_sdram_addr ; //读阶段数据地址

//==========================================assign=================================================================

//==========================================always=================================================================

//==========================================状态机=================================================================

//==========================================模块例化=================================================================

//------------- sdram_init_inst -------------

sdram_initial sdram_initial_inst

(

.clk (clk ), //系统时钟,频率100MHz

.rst_n (rst_n ), //复位信号,低电平有效

.init_cmd (init_cmd ), //初始化阶段写入sdram的指令

.init_bank (init_bank ), //初始化阶段Bank地址

.init_addr (init_addr ), //初始化阶段地址数据,辅助预充电操作

.init_end (init_end ) //初始化结束信号

);

//------------- sdram_arbit_inst -------------

sdram_arbit sdram_arbit_inst

(

.clk (clk ), //系统时钟

.rst_n (rst_n ), //复位信号

//sdram_init

.init_cmd (init_cmd ), //初始化阶段命令

.init_end (init_end ), //初始化结束标志

.init_bank (init_bank ), //初始化阶段Bank地址

.init_addr (init_addr ), //初始化阶段数据地址

//sdram_auto_ref

.auto_ref_req (atref_req ), //自刷新请求

.auto_ref_end (atref_end ), //自刷新结束

.auto_ref_cmd (atref_cmd ), //自刷新阶段命令

.auto_ref_bank (atref_bank ), //自动刷新阶段Bank地址

.auto_ref_addr (atref_addr ), //自刷新阶段数据地址

.aref_en (atref_en ), //自刷新使能

//sdram_write

.wr_req (sdram_wr_req ), //写数据请求

.wr_end (wr_end ), //一次写结束信号

.wr_en (wr_en ), //写数据使能

.write_cmd (wr_sdram_cmd ), //写阶段命令

.write_bank (wr_sdram_bank ), //写阶段Bank地址

.write_addr (wr_sdram_addr ), //写阶段数据地址

.wr_sdram_en (wr_sdram_en ), //写数据有效

.wr_sdram_data (wr_sdram_data ), //要写入sdram的数据

//sdram_read

.rd_req (sdram_rd_req ), //读数据请求

.rd_end (rd_end ), //一次读结束

.rd_en (rd_en ), //读数据使能

.read_cmd (rd_sdram_cmd ), //读阶段命令

.read_addr (rd_sdram_addr ), //读阶段数据地址

.read_bank (rd_sdram_bank ), //读阶段Bank地址

//SDRAM接口

.sdram_cke (sdram_cke ), //SDRAM时钟使能

.sdram_cs_n (sdram_cs_n ), //SDRAM片选信号

.sdram_ras_n (sdram_ras_n ), //SDRAM行地址选通

.sdram_cas_n (sdram_cas_n ), //SDRAM列地址选通

.sdram_we_n (sdram_we_n ), //SDRAM写使能

.sdram_bank (sdram_bank ), //SDRAM Bank地址

.sdram_addr (sdram_addr ), //SDRAM地址总线

.sdram_dq (sdram_dq ) //SDRAM数据总线

);

//------------- sdram_atref_inst -------------

sdram_auto_ref sdram_auto_ref_inst

(

.clk (clk ), //系统时钟,频率100MHz

.rst_n (rst_n ), //复位信号,低电平有效

.init_end (init_end ), //初始化结束信号

.auto_ref_en (atref_en ), //自动刷新使能

.auto_ref_req (atref_req ), //自动刷新请求

.auto_ref_cmd (atref_cmd ), //自动刷新阶段写入sdram的指令

.auto_ref_bank (atref_bank ), //自动刷新阶段Bank地址

.auto_ref_addr (atref_addr ), //地址数据,辅助预充电操作

.auto_ref_end (atref_end ) //自动刷新结束标志

);

//------------- sdram_write_inst -------------

sdram_write sdram_write_inst

(

.clk (clk ), //系统时钟,频率100MHz

.rst_n (rst_n ), //复位信号,低电平有效

.init_end (init_end ), //初始化结束信号

.wr_en (wr_en ), //写使能

.wr_addr (sdram_wr_addr ), //写SDRAM地址

.wr_data (sdram_data_in ), //待写入SDRAM的数据(写FIFO传入)

.wr_burst_len (wr_burst_len ), //写突发SDRAM字节数

.wr_ack (sdram_wr_ack ), //写SDRAM响应信号

.wr_end (wr_end ), //一次突发写结束

.write_cmd (wr_sdram_cmd ), //写数据阶段写入sdram的指令

.write_bank (wr_sdram_bank ), //写数据阶段Bank地址

.write_addr (wr_sdram_addr ), //地址数据,辅助预充电操作

.wr_sdram_en (wr_sdram_en ), //数据总线输出使能

.wr_sdram_data (wr_sdram_data ) //写入SDRAM的数据

);

//------------- sdram_read_inst -------------

sdram_read sdram_read_inst

(

.clk (clk ), //系统时钟,频率100MHz

.rst_n (rst_n ), //复位信号,低电平有效

.init_end (init_end ), //初始化结束信号

.rd_en (rd_en ), //读使能

.rd_addr (sdram_rd_addr ), //读SDRAM地址

.rd_data (sdram_dq ), //自SDRAM中读出的数据

.rd_burst_len (rd_burst_len ), //读突发SDRAM字节数

.rd_ack (sdram_rd_ack ), //读SDRAM响应信号

.rd_end (rd_end ), //一次突发读结束

.read_cmd (rd_sdram_cmd ), //读数据阶段写入sdram的指令

.read_bank (rd_sdram_bank ), //读数据阶段Bank地址

.read_addr (rd_sdram_addr ), //地址数据,辅助预充电操作

.rd_sdram_data (sdram_data_out ) //SDRAM读出的数据

);

endmodule

边栏推荐

猜你喜欢

REST会消失吗?事件驱动架构如何搭建?

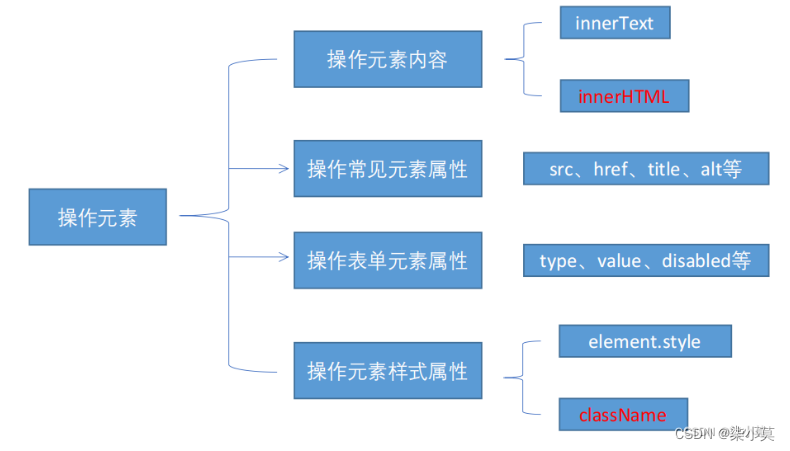

DOM 基础操作

Win11内存管理错误怎么办?

不就是个TCC分布式事务,有那么难吗?

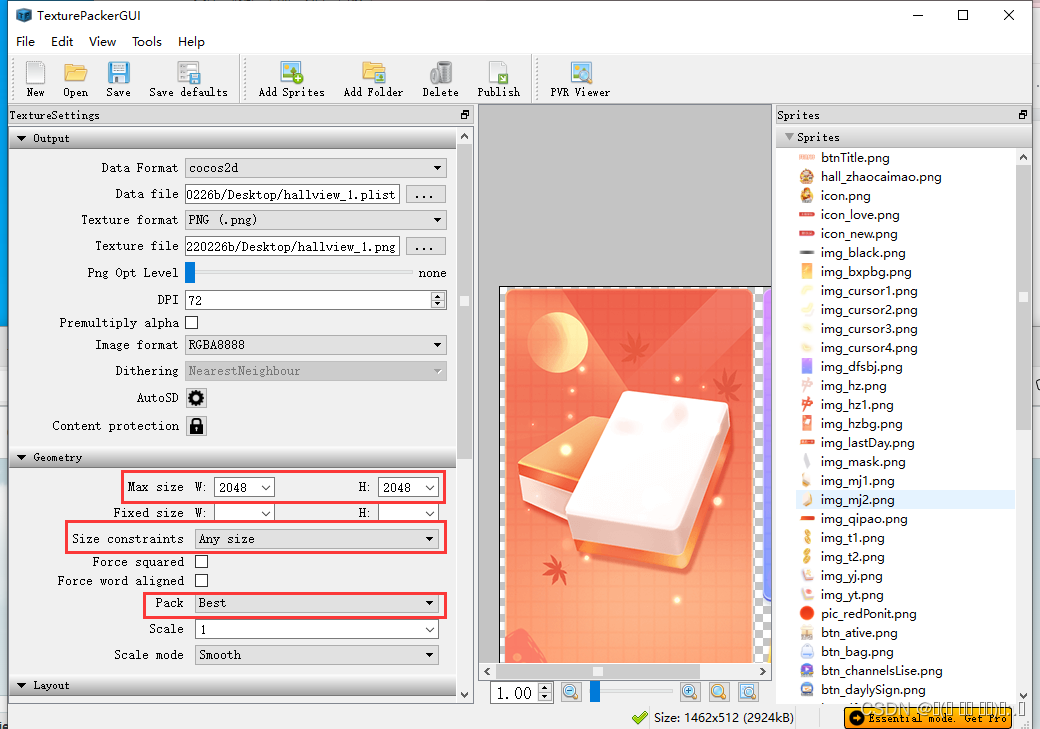

TexturePacker使用文档

How to reinstall Win11?One-click method to reinstall Win11

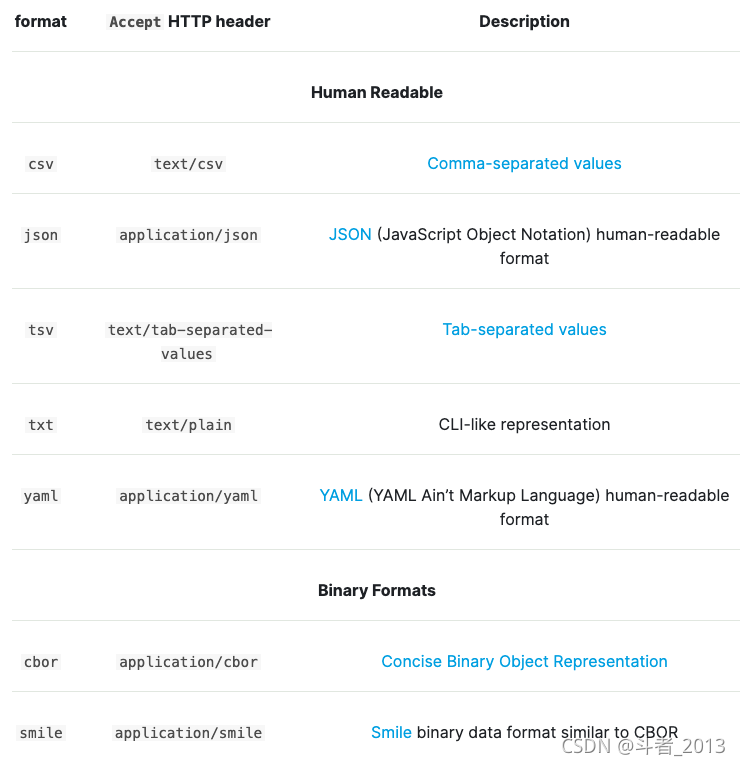

ES中SQL查询详解

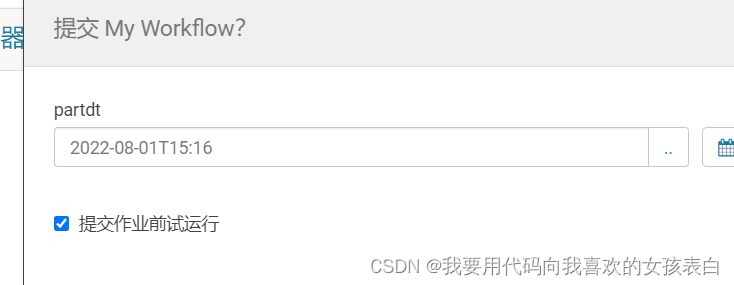

cdh的hue上oozie启动报错,Cannot allocate containers as requested resource is greater than maximum allowed

With a monthly salary of 12K, the butterfly changed to a new one and moved forward bravely - she doubled her monthly salary through the career change test~

Flink Yarn Per Job - CliFrontend

随机推荐

DOM 基础操作

FAST-LIO2 code analysis (2)

类型“FC<Props>”的参数不能赋给类型“ForwardRefRenderFunction<unknown, Props>”的参数。 属性“defaultProps”的类型不兼容。 不

【Leetcode】475. Heaters

Share an interface test project (very worth practicing)

An interview question about iota in golang

solidity

cdh6打开oozieWeb页面,Oozie web console is disabled.

【MySQL系列】MySQL数据库基础

Spark Sql之union

TCP 可靠吗?为什么?

security CSRF Vulnerability Protection

洞见云原生微服务及微服务架构浅析

【ACWing】230. 排列计数

thinkphp漏洞总结

Flink Yarn Per Job - 提交流程一

Various Joins of Sql

recursion: method calls itself

yay 报错 response decoding failed: invalid character ‘<‘ looking for beginning of value;

一篇永久摆脱Mysql时区错误问题,idea数据库可视化插件配置